DeepComputing và Xcalibyte vừa mở đặt hàng trước cho chiếc laptop RISC-V đầu tiên trong ngành công nghiệp - ROMA, được sản xuất hướng đến các nhà phát triển. Thiết bị hoạt động với con chip RISC-V 4 nhân và hỗ trợ hầu hết các phiên bản của hệ điều hành Linux.

ROMA là 1 nền tảng phát triển (development platform) có khả năng biên dịch gốc (native) RISC-V, cho phép các nhà phát triển kiểm tra phần mềm của họ chạy native trên RISC-V như thế nào. ROMA cũng giúp việc chuyển mã phát triển trên nó qua các hệ thống nhúng khác. Laptop trang bị vi xử lý RISC-V 4 nhân, đóng gói theo kiểu SoM (System on Module) với 2 tùy chọn Pro (12 nm) và Standard (28 nm). Đây cũng là laptop RISC-V đầu tiên có bộ tăng tốc GPU, NPU cho video và AI. Bộ nhớ trong LPDDR4/LPDDR4X của ROMA có dung lượng đến 16 GB, trong khi khả năng lưu trữ đến 256 GB.

Nền tảng ROMA thân thiện với Web3, tích hợp ví kiểu MetaMask, dễ dàng tạo NFT, hứa hẹn mang đến trải nghiệm tích hợp nhiều hơn với kính AR và loa AI trong tương lai, hoạt động hoàn toàn trên phần mềm và phần cứng RISC-V. Tích hợp sẵn ví MetaMask, NFT và PoS (Proof-of-Stake) blockchain giúp ROMA trở thành 1 công cụ cần thiết cho Metaverse trong tương lai. Có đến 7 công ty đóng góp vào sự phát triển của ROMA, gồm DeepComputing (kỹ thuật), PW (lắp ráp), Xcalibyte (tinh chỉnh hệ thống), ECP (bảo mật), XC (crypto), Rexeen (voice), LatticeX Foundation (PoS blockchain, NFT).

ROMA

ROMA là 1 nền tảng phát triển (development platform) có khả năng biên dịch gốc (native) RISC-V, cho phép các nhà phát triển kiểm tra phần mềm của họ chạy native trên RISC-V như thế nào. ROMA cũng giúp việc chuyển mã phát triển trên nó qua các hệ thống nhúng khác. Laptop trang bị vi xử lý RISC-V 4 nhân, đóng gói theo kiểu SoM (System on Module) với 2 tùy chọn Pro (12 nm) và Standard (28 nm). Đây cũng là laptop RISC-V đầu tiên có bộ tăng tốc GPU, NPU cho video và AI. Bộ nhớ trong LPDDR4/LPDDR4X của ROMA có dung lượng đến 16 GB, trong khi khả năng lưu trữ đến 256 GB.

Nền tảng ROMA thân thiện với Web3, tích hợp ví kiểu MetaMask, dễ dàng tạo NFT, hứa hẹn mang đến trải nghiệm tích hợp nhiều hơn với kính AR và loa AI trong tương lai, hoạt động hoàn toàn trên phần mềm và phần cứng RISC-V. Tích hợp sẵn ví MetaMask, NFT và PoS (Proof-of-Stake) blockchain giúp ROMA trở thành 1 công cụ cần thiết cho Metaverse trong tương lai. Có đến 7 công ty đóng góp vào sự phát triển của ROMA, gồm DeepComputing (kỹ thuật), PW (lắp ráp), Xcalibyte (tinh chỉnh hệ thống), ECP (bảo mật), XC (crypto), Rexeen (voice), LatticeX Foundation (PoS blockchain, NFT).

Để đánh dấu sự ra đời của ROMA, 100 khách hàng đầu tiên đặt trước còn được tặng 1 NFT độc quyền, cũng như có thể yêu cầu khắc tên lên sản phẩm.

RISC-V là gì?

RISC-V là 1 kiến trúc tập lệnh (ISA - Instruction Set Architecture) tiêu chuẩn mở (open source) thế hệ thứ 5 của kiến trúc RISC, được phát triển từ năm 1981 bởi Đại học California, Berkeley, Mỹ. Trong kỹ thuật máy tính thì RISC (Reduced Instruction Set Computer) là máy tính có thiết kế để đơn giản hóa các lệnh riêng lẻ được cung cấp cho máy nhằm hoàn thành các tác vụ. So với CISC (Complex Instruction Set Computer), RISC cần nhiều mã lệnh hơn để hoàn thành 1 tác vụ, do các lệnh riêng lẻ được viết bằng mã đơn giản.

Hiện tại thế giới có 2 thiết kế vi xử lý phổ biến là Arm và x86, thống trị gần như toàn bộ thị trường, nhưng với mô hình kinh doanh khác biệt. Trong khi Intel tự thiết kế x86 và sản xuất vi xử lý để bán thì Arm bán giấy phép sử dụng thiết kế của họ cho những bên có nhu cầu, đơn cử như Samsung hay Qualcomm. Dĩ nhiên các bên thứ 3 mua quyền sử dụng thiết kế Arm cần ký thỏa thuận giữ bí mật, vì đây là sở hữu trí tuệ. Trong khi đó, RISC-V lại hoàn toàn khác.

Nếu muốn sử dụng máy tính, người ta cần cài đặt hệ điều hành, và nếu lựa chọn là Windows thì phải trả tiền bản quyền, trong khi Linux lại miễn phí. RISC-V cũng tương tự như vậy, nhưng nó nhắm đến thị trường thiết kế bán dẫn. Kiến trúc tập lệnh (ISA) là các lệnh mà vi xử lý có thể hiểu được native trong khi vi kiến trúc là cách mà vi xử lý thực hiện lệnh, Arm cấp phép cho cả 2 nhưng RISC-V chỉ cung cấp ISA. Điều này cho phép các nhà nghiên cứu hay sản xuất tự xác định cách thức mà họ muốn sử dụng, từ đó có thể mở rộng cho nhiều thiết bị khác nhau, từ chip 16 bit công suất thấp thường dùng trong hệ thống nhúng, cho đến CPU 128 bit trong siêu máy tính.

Những con chip RISC thường có ít lệnh hơn so với chip dùng thiết kế CISC, đồng thời lệnh của RISC cũng đơn giản hơn để thực hiện trong phần cứng. Lệnh được đơn giản hóa nghĩa là các nhà sản xuất chip có thể đạt được hiệu quả cao hơn khi thiết kế chip. Những lệnh phức tạp sẽ được chia thành nhiều lệnh đơn giản bằng phần mềm, hay trình biên dịch. Bên trong các vi xử lý là hàng tỉ transistor (bóng bán dẫn), và với chip CISC, có nhiều transistor trong số này đại diện cho các lệnh có sẵn. RISC đơn giản và có ít lệnh hơn nên không cần nhiều transistor như CISC, vì vậy xét trên cùng 1 diện tích đế, người ta có thể bổ sung thêm những thứ khác như bộ đệm, chức năng xử lý bổ sung cho video, AI hay tính năng khác. Ngoài ra, các chip RISC của MIPS và Arm thường được sử dụng trong thiết bị IoT (Internet of Things) do ít transistor nên chúng có thể được sản xuất với kích thước vật lý nhỏ, ít tiêu thụ năng lượng và dễ tích hợp/nhúng.

Định luật Moore không còn đúng, RISC có thể là lời giải tiếp theo

Quảng cáo

Hiện tại thì người ta vẫn đang chạy đua để thu nhỏ transistor bằng tiến trình công nghệ mới, nhưng điều này có giới hạn. Chúng ta đang ở 5 nm, và hướng đến 3 nm cùng với hàng loạt công nghệ phụ trợ nhằm tăng hiệu suất vi xử lý nhờ tăng mật độ bán dẫn. Ngày 15/11/1971, Intel thương mại hóa thành công mẫu vi xử lý (microprocessor) đầu tiên - Intel 4004 - với giá 60 USD. Con chip này sản xuất trên tiến trình 10 μm công nghệ pMOS tăng cường tải cổng silicon (silicon-gate enhancement-load pMOS) với diện tích đế 12 mm2, có khả năng thực hiện đến 92,000 lệnh mỗi giây, mỗi chu kỳ lệnh 10.8 ms. Intel 4004 có 2300 transistor. 50 năm sau, Alder Lake ra đời với tiến trình 10 nm (Intel 7), có 100 tỉ transistor.

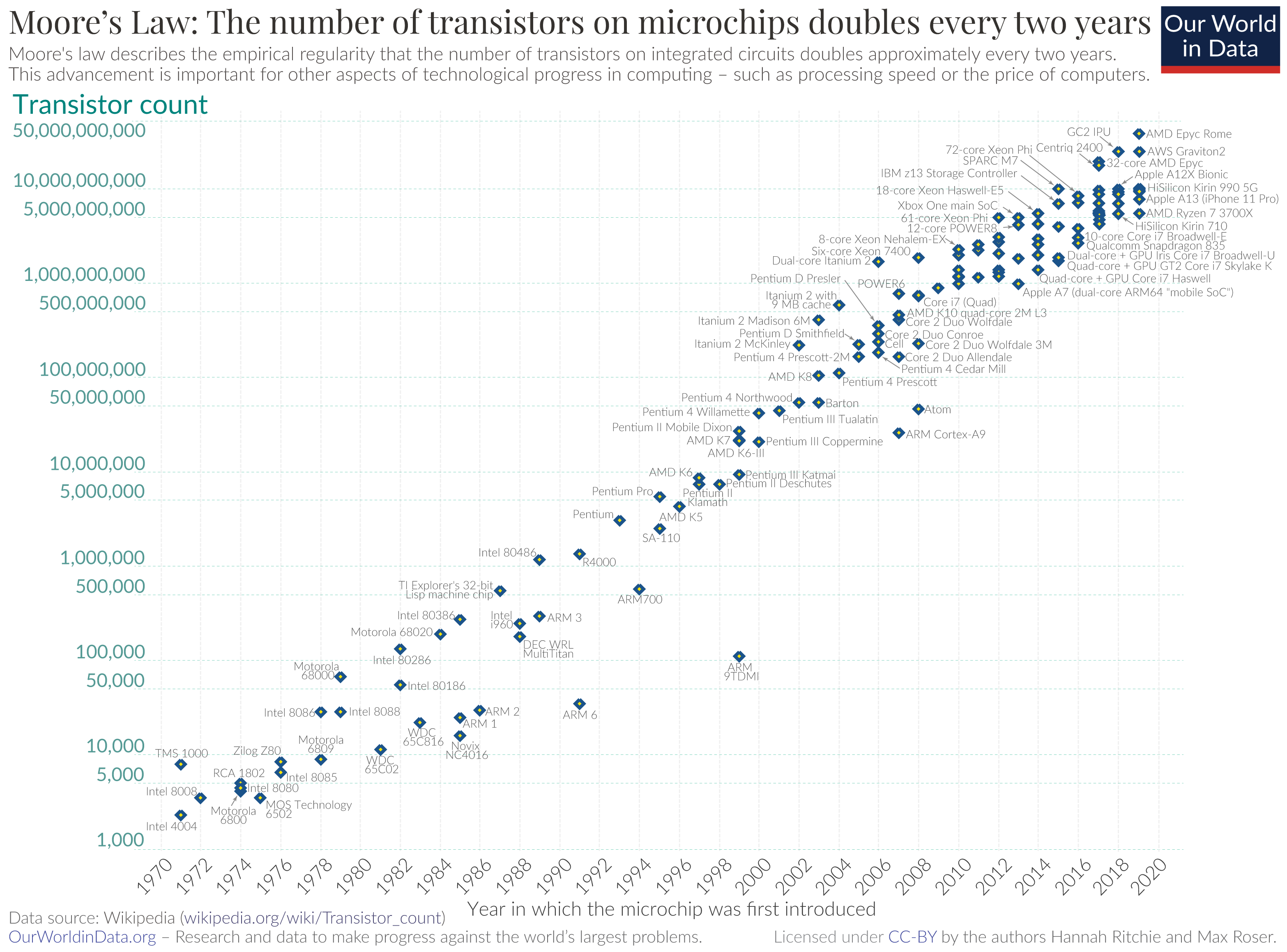

Gordon Earle Moore, đồng sáng lập Intel, năm 1965 đã đưa ra giả thuyết mà chúng ta hay gọi là Định luật Moore, rằng số lượng transistor có thể nhồi nhét trên 1 con chip sẽ tăng gấp đôi sau mỗi 2 năm. Thực tế cho thấy việc thu nhỏ transistor để tăng mật độ của chúng trên vi xử lý hiện đại ngày càng khó khăn hơn do giới hạn về công nghệ. Các nhà nghiên cứu vẫn miệt mài tìm cách, nhưng không thể theo được những gì mà Moore nhận định cách đây gần 60 năm.

Chi phí, tài nguyên con người để chế tạo ra transistor nhỏ hơn ngày càng cao, đơn cử như TSMC đã chi hơn 17 tỉ USD để tạo ra chip trên tiến trình 5 nm. RISC-V có thể là lời giải cho bài toán tăng hiệu suất nhờ những tập lệnh đơn giản, để ít phải phụ thuộc vào số lượng transistor. Bù lại, các nhà nghiên cứu vẫn đang tích cực phát triển trình biên dịch đủ khả năng, hiệu năng đáp ứng cho những gì mà Arm và x86 đã xây dựng trong nhiều thập kỷ qua.

Có gì trong vi xử lý Prodigy đến 128 nhân của startup bán dẫn Tachyum?

Tachyum Prodigy là 1 vi xử lý đa năng (Universal Processor), có khả năng chạy bất kỳ dòng mã nào nhờ trang bị trình biên dịch nhị phân động (dynamic binary translator). Con chip của startup bán dẫn này có phiên bản cao nhất (dự kiến) sở hữu đến 128…

tinhte.vn