Đầu năm nay, Intel có CEO mới, và khởi động kế hoạch kinh doanh mới, mở rộng cả khả năng sản xuất, cũng như mở luôn cả các fab chế tác chip bán dẫn của họ để sản xuất thương mại cho các đơn vị khác, hệt như cách Samsung và TSMC đang vận hành. Rạng sáng nay 27/07, Intel đã livestream tường thuật sự kiện Intel Accelerated, đưa ra chiến lược nâng cấp chip xử lý CPU trong tương lai, không chỉ phục vụ cho chính họ mà còn cả những đơn vị khác. Đặc biệt hơn cả, Intel cũng đã công bố tiến trình chip bán dẫn trong tương lai của họ từ nay đến năm 2025:

![[IMG]](https://photo2.tinhte.vn/data/attachment-files/2021/07/5566284_Tinhte_Intel1.jpg)

Đầu năm nay, tân CEO Intel Pat Gelsinger đã đưa ra kế hoạch tên là IDM 2.0, với ba yếu tố chính:

Mục tiêu ở đây là, Intel sẽ tiếp tục phát triển và hoàn thiện những tiến trình chip bán dẫn đã đặt ra, sau tiến trình 10nm đang trong quá trình sản xuất thương mại hóa ở thời điểm hiện tại, nhưng cùng lúc vẫn phải nhờ tới những đơn vị khác để thúc đẩy doanh số chip CPU, củng cố thị phần của họ. Nhưng mục tiêu xa nhất vẫn là mở rộng IFS (Intel Foundry Services) để kiếm tiền từ cả những hãng khác bằng cách chế tác, chứ fab không chỉ phục vụ riêng mình Intel nữa.

![[IMG]](https://photo2.tinhte.vn/data/attachment-files/2021/07/5566284_Tinhte_Intel1.jpg)

Định hướng để cạnh tranh với chính TSMC, hay bất kỳ fab nào khác

Đầu năm nay, tân CEO Intel Pat Gelsinger đã đưa ra kế hoạch tên là IDM 2.0, với ba yếu tố chính:

- Xây dựng (tăng tốc phát triển tiến trình 7nm)

- Mở rộng (nhờ TSMC sản xuất vài mẫu CPU thương mại)

- Thương mại hóa (mở Intel fab phục vụ các đối tác sản xuất chip)

Mục tiêu ở đây là, Intel sẽ tiếp tục phát triển và hoàn thiện những tiến trình chip bán dẫn đã đặt ra, sau tiến trình 10nm đang trong quá trình sản xuất thương mại hóa ở thời điểm hiện tại, nhưng cùng lúc vẫn phải nhờ tới những đơn vị khác để thúc đẩy doanh số chip CPU, củng cố thị phần của họ. Nhưng mục tiêu xa nhất vẫn là mở rộng IFS (Intel Foundry Services) để kiếm tiền từ cả những hãng khác bằng cách chế tác, chứ fab không chỉ phục vụ riêng mình Intel nữa.

Dẫn đầu kế hoạch này là tiến sỹ Ann B. Kelleher, phó chủ tịch kiêm giám đốc điều hành mảng phát triển công nghệ của Intel. Ban đầu mảng này thuộc System Architecture Group, đơn vị nghiên cứu và phát triển kiến trúc chip bán dẫn, nhưng đến tháng 7/2020, họ tách riêng ra để chỉ tập trung nghiên cứu công nghệ, giúp các fab của Intel làm việc hiệu quả nhất.

Và về cơ bản, mục tiêu dẫn đầu công nghệ chip bán dẫn của Intel vẫn dựa vào một đơn vị đo rất quen thuộc đối với anh em, đó là performance per watt.

Đổi tên tiến trình chip bán dẫn

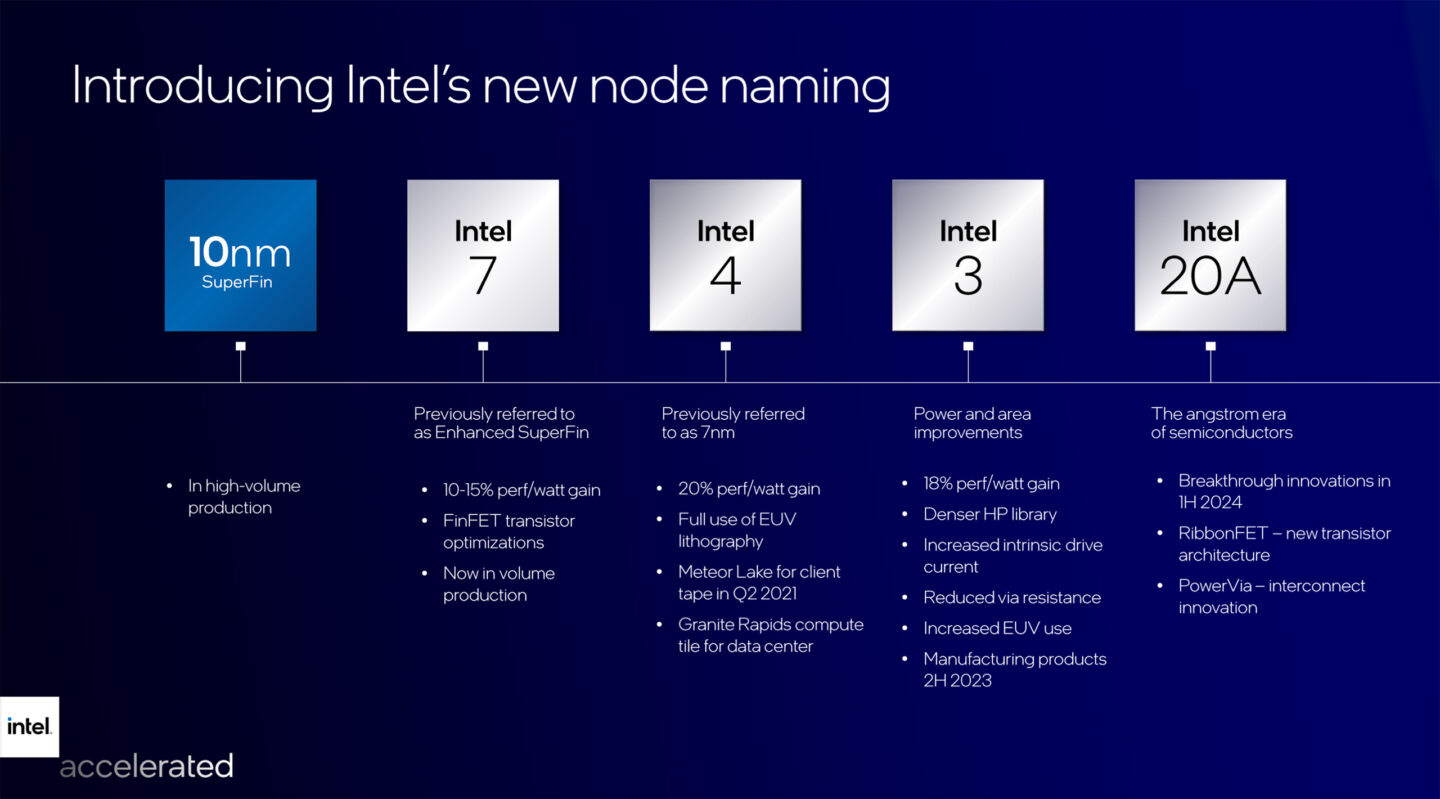

Thay vì tiếp tục dùng đơn vị đo nanomet bên cạnh những tiến trình mới, thì Intel sử dụng những con số để có sự đồng nhất với tốc độ phát triển của ngành chip bán dẫn thế giới. Ai cũng đã biết mật độ transistor của tiến trình 10nm Intel ngang ngửa tiến trình 7nm của TSMC, nhưng nghĩ đến con số càng nhỏ thì tâm lý chung của thị trường sẽ mặc định cho rằng lượng transistor trên bề mặt die chip bán dẫn sẽ nhiều hơn. Thực tế thì, ở cái thời con người còn sử dụng transistor 2D planar, con số nanomet vẫn còn ý nghĩa về mặt vật lý. Nhưng tới khi chúng ta chuyển đổi sang tiến trình sản xuất FinFET 3D transistor, thì 7 hay 5nm đôi khi chỉ mang giá trị quảng cáo.

Cũng vì lý do đó, Intel quyết định rằng sau tiến trình 10nm, họ sẽ không dùng khái niệm nanomet trong mỗi tiến trình sản xuất chip bán dẫn trong tương lai gần nữa:

Cụ thể hơn là như thế này:

- 2020: Intel 10nm SuperFin (10SF). Tiến trình đang sử dụng để sản xuất chip CPU kiến trúc Tiger Lake và GPU Xe-LP với những sản phẩm như SG1 hay DG1.

- Nửa cuối 2021: Intel 7. Đây cơ bản chính là 10nm Enhanced Super Fin. Kể từ giờ những CPU như Alder Lake hay Sapphire Rapids sẽ được gọi là Intel 7, với hiệu năng performance per watt tăng từ 10-15% so với kiến trúc 10nm Super Fin. Hiện tại CPU Alder Lake sắp ra mắt vào cuối năm nay sẽ được gọi tên là kiến trúc Intel 7.

- Nửa cuối 2022: Intel 4. Hiểu đơn giản là tiến trình 7nm của Intel có mật độ transistor ngang ngửa với 7nm của TSMC. Đầu năm nay Intel cho biết những chip xử lý kiến trúc Meteor Lake sẽ sử dụng compute tile dựa trên tiến trình này, và đang được thử nghiệm. Intel kỳ vọng hiệu năng chip Intel 4 sẽ tăng 20% so với Intel 7. Những sản phẩm trong tương lai như kiến trúc Xeon Granite Rapids sẽ được sản xuất trên tiến trình này.

- Nửa cuối 2023: Intel 3. Hay có thể hiểu đây là tiến trình 7nm+ của Intel, đủ những chi tiết mới để được coi là một tiến trình mới hoàn toàn.

- 2024: Intel 20A. Thay vì gọi là Intel 2, thì đơn vị đo Angstrom được ứng dụng, dù rằng 20 Angstrom thì cũng bằng 2nm. Tiến trình này cơ bản chính là Intel 5nm. Họ sẽ chuyển dịch từ việc ứng dụng transistor FinFET sang những transistor Gate-All-Around gọi là RibbonFET. Cùng với đó, công nghệ PowerVia cũng sẽ được công bố và ứng dụng.

- 2025: Intel 18A. Intel kỳ vọng đến năm 2025, họ sẽ ứng dụng được tiến trình 18A để sản xuất những con chip xử lý dựa trên máy EUV của ASML, gọi là thiết bị High-NA, sử dụng ánh sáng để khắc transistor chính xác hơn rất nhiều. Intel cũng cho biết, High-NA, Intel 3 và Intel 20A cũng sẽ là giải pháp và tiến trình họ cung cấp cho các đối tác để sản xuất chip bán dẫn.

Angstrom: Thời kỳ hậu nanomet, transistor xếp như những tòa nhà cao tầng

Quảng cáo

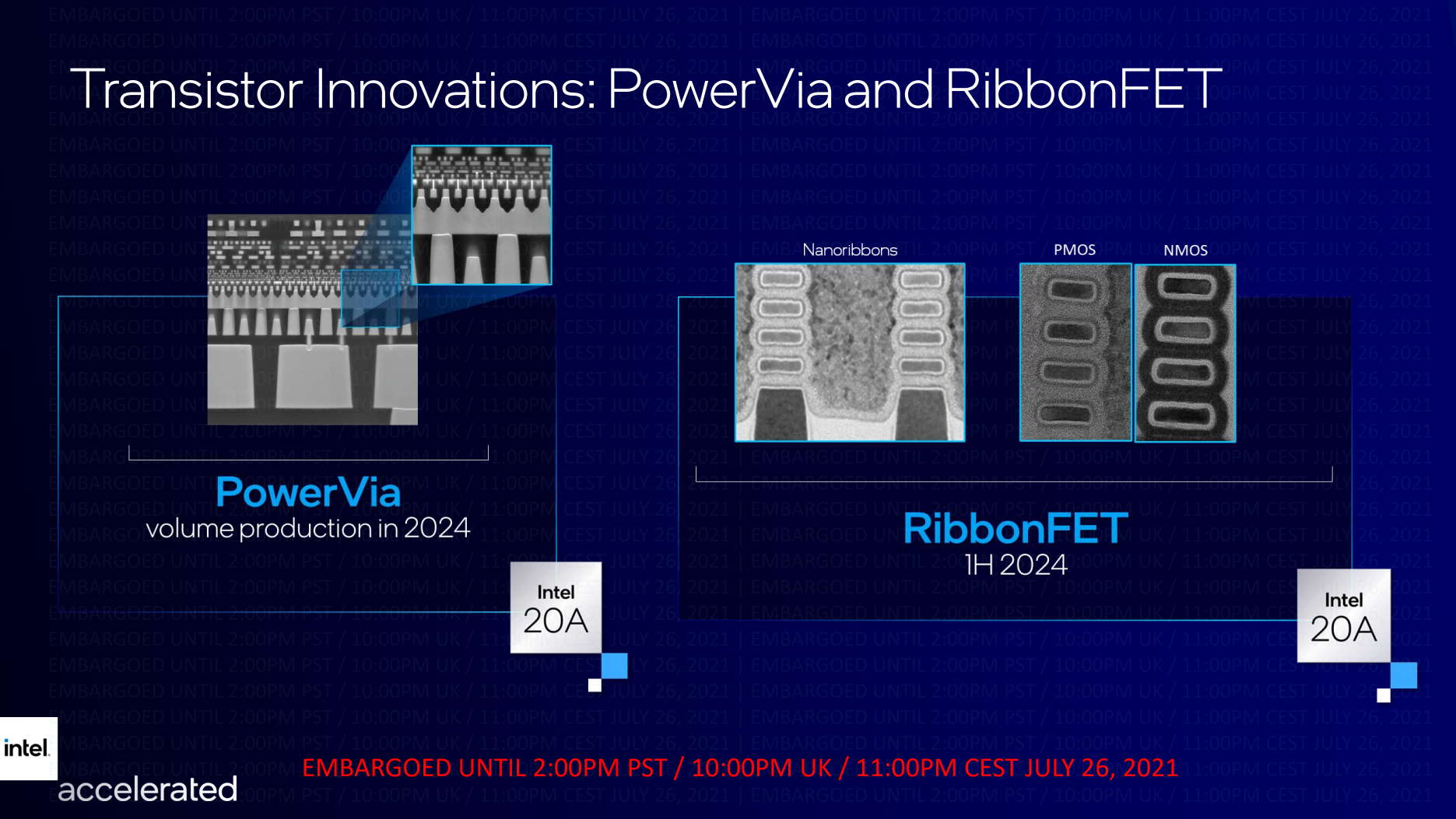

Như đã đề cập, không chỉ mang cái tên mới, Intel còn kỳ vọng sẽ ứng dụng được thiết kế transistor mới hoàn toàn của họ, kể từ khi họ tạo ra FinFET 22nm vào năm 2011. RibbonFET, hay còn gọi là NanoSheet, hoặc như đã nói ở trên, là transistor Gate-All-Around có thể tăng tốc độ chuyển giá trị 0 và 1, cũng như đủ khả năng tối ưu điện năng sử dụng trong con chip CPU thế hệ mới, từ đó tạo ra một die chip xử lý nhỏ hơn, mật độ transistor cao hơn nhiều so với trước.

PowerVia cũng là thứ rất quan trọng để tạo ra những transistor xếp chồng lên nhau theo chiều dọc, tạo ra một giải pháp gọi là “backside power delivery” để tối ưu không làm lãng phí điện năng cũng như tối ưu truyền dữ liệu, thông qua việc loại bỏ đường điện đầu vào ở mặt trước tấm wafer chip bán dẫn. Không có PowerVia, thì cũng không có RibbonFET và Intel 20A. Bố cục của công nghệ này như sau:

- Ở dưới đáy tấm wafer là đường cấp điện cho transistor.

- Phía trên đường cấp điện là các lớp transistor RibbonFET chồng lên nhau.

- Trên cùng của tấm wafer silicon là các đường dẫn cho dữ liệu.

Trên những chip bán dẫn hiện giờ, transistor ở lớp dưới cùng tấm wafer, rồi hai lớp truyền dữ liệu và cấp điện phải được “in” đồng thời để chạm được vào lớp transistor ở dưới, ví dụ bằng hình minh họa của Intel:

Trước kia, Intel đã công bố thiết kế chip xếp chồng, gọi là Foveros. Intel 20A sẽ dựa trên công nghệ này để trở thành hiện thực. Và cũng nhờ đó, định luật Moore sẽ bước vào một kỷ nguyên mới. Thay vì cố gắng thu gọn khoảng cách giữa từng transistor trên một đơn vị diện tích die silicon, thì xếp chồng transistor lên nhau sẽ giúp tăng số lượng transistor lên, giữ cho định luật Moore vẫn còn giá trị.

Quảng cáo

Với tên gọi "Foveros 3D", kỹ thuật sản xuất chip mới được Intel mô tả là xếp chồng các thành phần 2D. Chi tiết hơn, nhiều thành phần của một bộ vi xử lý sẽ được chia ra thành các chiplet nhỏ hơn, mỗi chiplet có thể được sản xuất bằng những tiến trình khác nhau. Đối với tiến trình Intel 20A, hai phiên bản của Foveros 3D sẽ lần lượt được ứng dụng:

- Foveros Omni ứng dụng thế hệ mới của công nghệ chồng chip, tối ưu khả năng kết nối dữ liệu và tương tác giữa các die chip bán dẫn, tạo ra thiết kế dạng module tiện lợi. Dự kiến Foveros Omni sẽ đi vào sản xuất thương mại hóa vào năm 2023.

- Bước tiến tiếp theo là Foveros Direct, chuyển dịch từ việc kết nối copper-to-copper sang những đường dẫn dữ liệu trở kháng thấp. Nhờ Foveros Direct, Intel sẽ có thể sản xuất những con chip bán dẫn với khoảng cách giữa các transistor là rất nhỏ, tăng mật độ đường dẫn để chồng thêm những lớp transistor mới, tạo ra giải pháp mà công nghệ sản xuất hiện giờ chưa thể đạt được. Cầu nối giữa các die được Intel gọi là công nghệ EMIB (Embedded Multi-Die Interconnect Bridge), với những lợi thế so với cầu nối copper-to-copper được mô tả trong clip dưới đây:

Có lẽ, nếu Intel thành công và tốc độ nghiên cứu phát triển sản phẩm của họ đạt mục tiêu đề ra, thì Intel sẽ một lần nữa tạo ra cuộc cách mạng của ngành chip bán dẫn, thứ mà nếu mô tả công bằng thì không khác gì khoa học viễn tưởng, khi con người dạy những hạt cát biết làm toán và phục vụ chúng ta.

Theo Anandtech, ArsTechnica