Con CPU, GPU hay bất kì bộ xử lý nào, kể cả chip RAM, chip nhớ trong SSD thật ra đều là những mạch điện siêu phức tạp, trong đó có các bóng bán dẫn, những đường nối điện rất bé ở mức nm. Kể cả bóng bán dẫn thật ra cũng được hình thành nhờ vào hàng loạt những đường cắt rồi sau đó bổ sung thêm một số vật liệu khác. Vậy làm sao người ta có thể tạo ra những đường này?

Lưu ý trước khi đọc tiếp: 10nm, 7nm, 5nm, 3nm chỉ là tên gọi cho những tiến trình sản xuất chip, nó không đại diện cho bất kì kích thước vật lý nào trong con chip, không phải là kích thước bóng bán dẫn, không phải là khoảng cách giũa các cực, không phải là khoảng cách giữa các vây fin của bán dẫn. Hiện nay các bán dẫn dùng trong chip hiện đại là 3D, mà vật thể 3D thì không thể đo bằng chỉ 1 chiều được.

Rồi, giờ vào việc nào.

Lưu ý trước khi đọc tiếp: 10nm, 7nm, 5nm, 3nm chỉ là tên gọi cho những tiến trình sản xuất chip, nó không đại diện cho bất kì kích thước vật lý nào trong con chip, không phải là kích thước bóng bán dẫn, không phải là khoảng cách giũa các cực, không phải là khoảng cách giữa các vây fin của bán dẫn. Hiện nay các bán dẫn dùng trong chip hiện đại là 3D, mà vật thể 3D thì không thể đo bằng chỉ 1 chiều được.

Rồi, giờ vào việc nào.

Quá trình quang khắc (photolithography) diễn ra như thế nào?

Mời các bạn nhìn vào một con chip thì thực tế trông nó sẽ thế nào nha. Lưu ý đây là một con chip khác cũ rồi, chứ các SoC hiện đại ngày nay sẽ càng phức tạp và càng nhỏ hơn nữa

Bạn có thấy những đường nối này không? Nó là các đường mạch để cấu thành một con chip, zoom sát vào nữa thì người ta sẽ thấy các bóng bán dẫn nhỏ xíu nằm bên dưới. Mình đưa cái video này để bạn có thể hiểu được là những thứ này nó nhỏ tới mức nào.

Để tạo ra được những đường nét này, người ta sử dụng quy trình quang khắc, bao gồm việc in ra các đường mong muốn, rồi xử lý hóa chất để tạo hình. Phần này sẽ hình dung rõ nhất khi bạn xem video này, chứ giải thích bằng chữ thì dài và khó hiểu lắm.

Những cái đường được quang khắc này (pattern) là thứ sẽ giúp hình thành nên các linh kiện điện tử cũng như các mạch nối trong CPU. Nhìn qua video thì đơn giản nhưng thực tế người ta sẽ làm việc này vài chục lần, tạo ra cả chục lớp khác nhau thì quá trình litho mới hoàn tất.

Làm sao người ta có thể in được những đường ngày càng nhỏ và sát nhau?

Nhưng vấn đề là máy in quang khắc chắc chắn sẽ có mức giới hạn của nó, trong khi các hãng thiết kế chip thì muốn chip ngày càng bé hơn => tức là bóng bán dẫn cũng nhỏ nhỏ đi, vậy làm sao người ta có thể vượt qua giới hạn này?

Ví dụ cụ thể: các máy quang khắc hiện nay sử dụng tia Extreme Ultraviolet (EUV) loại xịn nhất của ASML có thể khắc được các đường nhỏ nhất vào khoản 13nm. Nhưng giờ chúng ta cần những đường nhỏ hơn nữa để tạo ra những con chip có khả năng đáp ứng được các dây chuyền sản xuất càng lúc càng bé như 10nm, 7nm, 5nm, 3nm thì làm thế nào?

Quảng cáo

Con số 13nm ở trên là giới hạn “độ phân giải” (nguyên văn: resolution limit) của những cỗ máy quang khắc được ASML sản xuất, những cỗ máy này đang được Intel, Samsung, TSMC và nhiều công ty chip lớn trên thế giới mua về sử dụng. Do kích thước chip ngày càng nhỏ, số bóng bán dẫn trên 1 đơn vị diện tích ngày càng tăng lên, các máy quang khắc cũng phải thu nhỏ “độ phân giải” cho tương ứng.

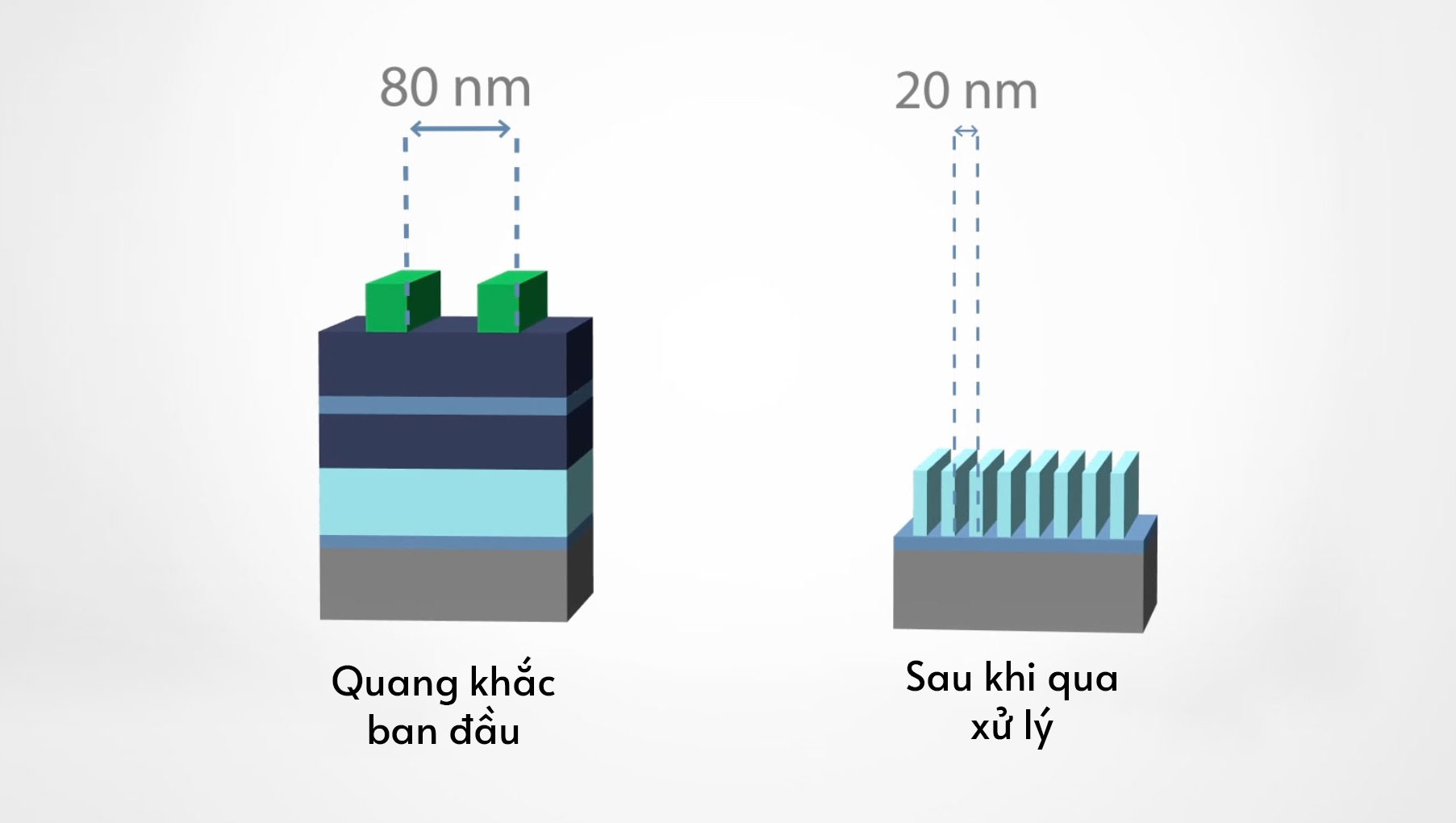

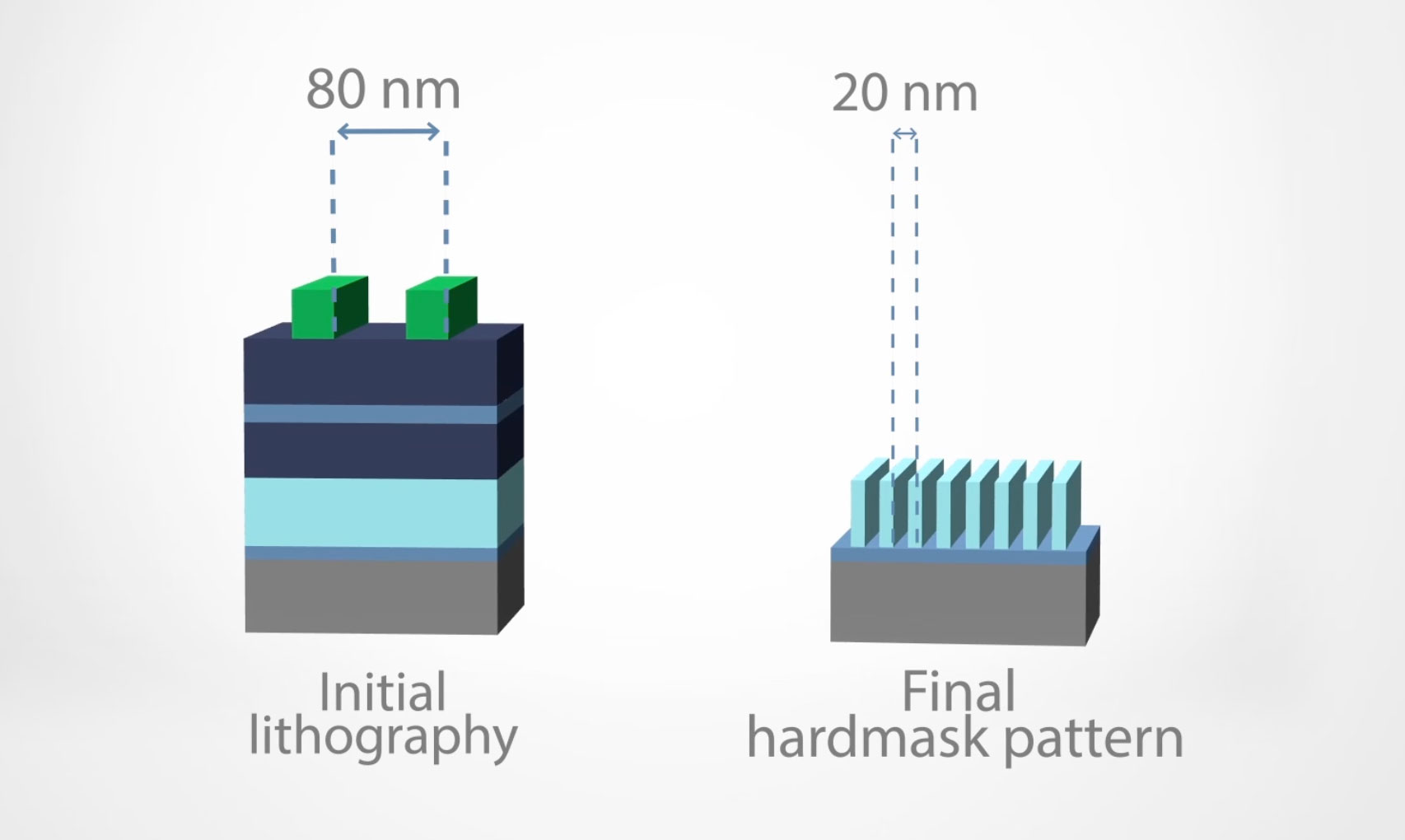

Trong thế giới của các hãng sản xuất bán dẫn, họ dùng kĩ thuật tên là multi-patterning, tức là thực hiện biến đổi nhiều lần thay vì chỉ thực hiện 1 lần. Cứ qua mỗi khâu in, khắc ăn mòn, làm đầy (deposition), rồi lại khắc, ăn mòn, làm đầy… các đường mạch sẽ càng gần nhau hơn, nhỏ hơn. Đây cũng là cách mà các hãng làm chip có thể tăng được mật độ bóng bán dẫn trên mỗi mm vuông đấy.

Multi-patterning này có thể được làm 2 lần (double patterning), 3 lần (triple patterning) hay thậm chí nhiều hơn. Khi ra mắt dây chuyền 20nm, TSMC đã sử dụng double patterning để sản xuất ra chip 20nm đấy. Hay như công ty LAM Research, họ nghiên cứu kĩ thuật multi-patterning có thể khắc được những đường nhỏ và tăng mật độ lên gấp 4 lần so với việc chỉ dùng 1 lần quang khắc. Với những con chip NAND vertical, các ô nhớ được sắp theo chiều dọc để tăng mật độ lưu trữ, và người ta cũng dùng multi patterning để tạo ra cấu trúc bán dẫn 3D cực kì phức tạp cả theo phương dọc và ngang.

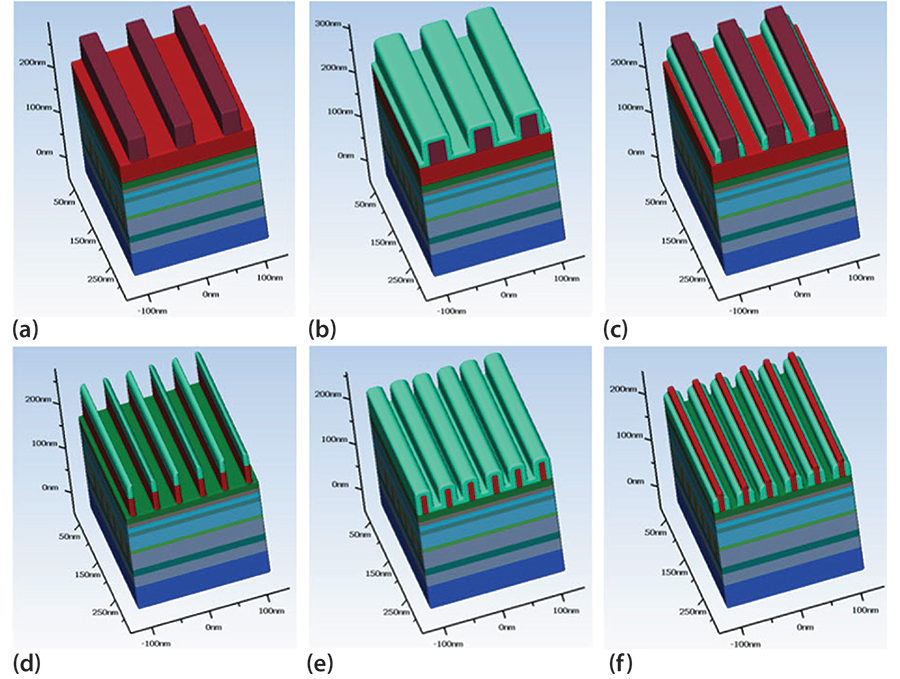

Đây là hình ví dụ của một phần bán dẫn được khắc theo phương pháp self-aligned quadruple-patterning (SAQP).

a: Các đường trục màu đỏ được vẽ ra trên bề mặt cứng

b: Lớp điện môi đầu tiên được phủ lên (dielectric spacer deposition)

Quảng cáo

c: Ăn mòn lớp điện môi để mở ra những đường trục mới và lớp bên dưới của nó

d: Ăn mòn đường trục và chuyển các đường spacer đầu tiên vào lớp dưới, tạo ra đường trục thứ hai

e: Phủ lớp điện môi thứ hai bao

f: Ăn mòn lớp điện môi thứ hai để mở ra những đường trục thứ hai

Bạn cũng có thể xem video bên dưới để hình dung về quy trình này dễ dàng hơn

Ngoài SAQP, người ta còn dùng nhiều kĩ thuật khác nữa như SAB, SADP, SALELE để sản xuất ra những con chip ở mức 5nm trở xuống. Bạn có thể tìm hiểu thêm về 4 phương pháp này tại link. Còn trong khuôn khổ bài này thì dừng ở đây thôi chứ không thì phức tạp lắm 😁

Tóm lại, quá trình multi patterning giúp tạo ra những đường nhỏ hơn trong hệ thống mạch điện của một con chip, vượt qua cả giới hạn nhỏ nhất mà máy in litho có thể in được, nhờ vậy người ta có thể tiếp tục sáng tạo nên những con chip ngày càng nhỏ và giảm sự phụ thuộc vào độ phân giải của máy in litho.

Và để có thể xử lý được nhiều lớp, nhiều tầng như vậy, người ta cũng dùng mỗi tầng một mask - một bản đồ để biết cần vẽ nên các đường như thế nào. Một con chip Intel 14nm có thể cần tới 50 mask. Hay một con chip 3nm mà ASML đề cập làm tham chiếu sẽ cần đến 80 lớp khác nhau, trong đó 26 lớp phải in bằng máy EUV, còn lại thì dùng máy DUV.

Thách thức của việc xử lý nhiều lớp này đó là:

- Tốn thời gian, sẽ tăng chi phí sản xuất

- Sản lượng sẽ giảm đi

- Độ chính xác khi in, khắc sẽ phải giữ ở mức rất cao, sai số chỉ trong vòng 1nm, nếu không thì chip sẽ hỏng

Thế nên việc thu nhỏ chip không hề dễ dàng, có rất nhiều thách thức về mặt vật lý và kĩ thuật mà các công ty phải trải qua để tạo ra các sản phẩm tốt hơn, đó là chưa bàn đến chi phí và các khía cạnh kinh doanh. Bản thân các hãng làm máy sản xuất chip như ASML cũng phải cố gắng để cải thiện hệ thống, tăng sản lượng và tăng độ chính xác. Thật tốt khi vẫn còn đang rất nhiều người làm việc để chúng ta có thêm những con chip mạnh mẽ, tiết kiệm điện.