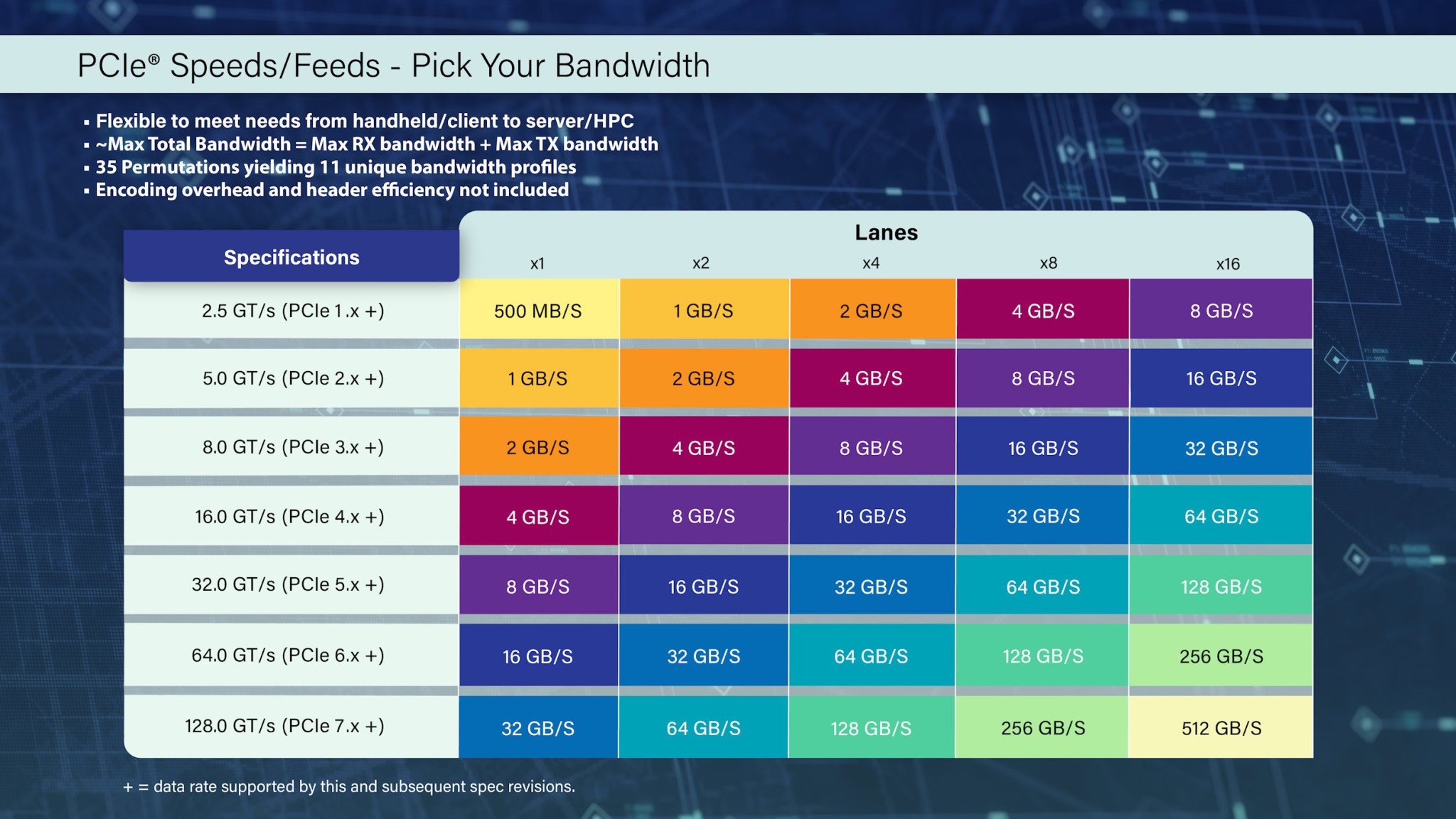

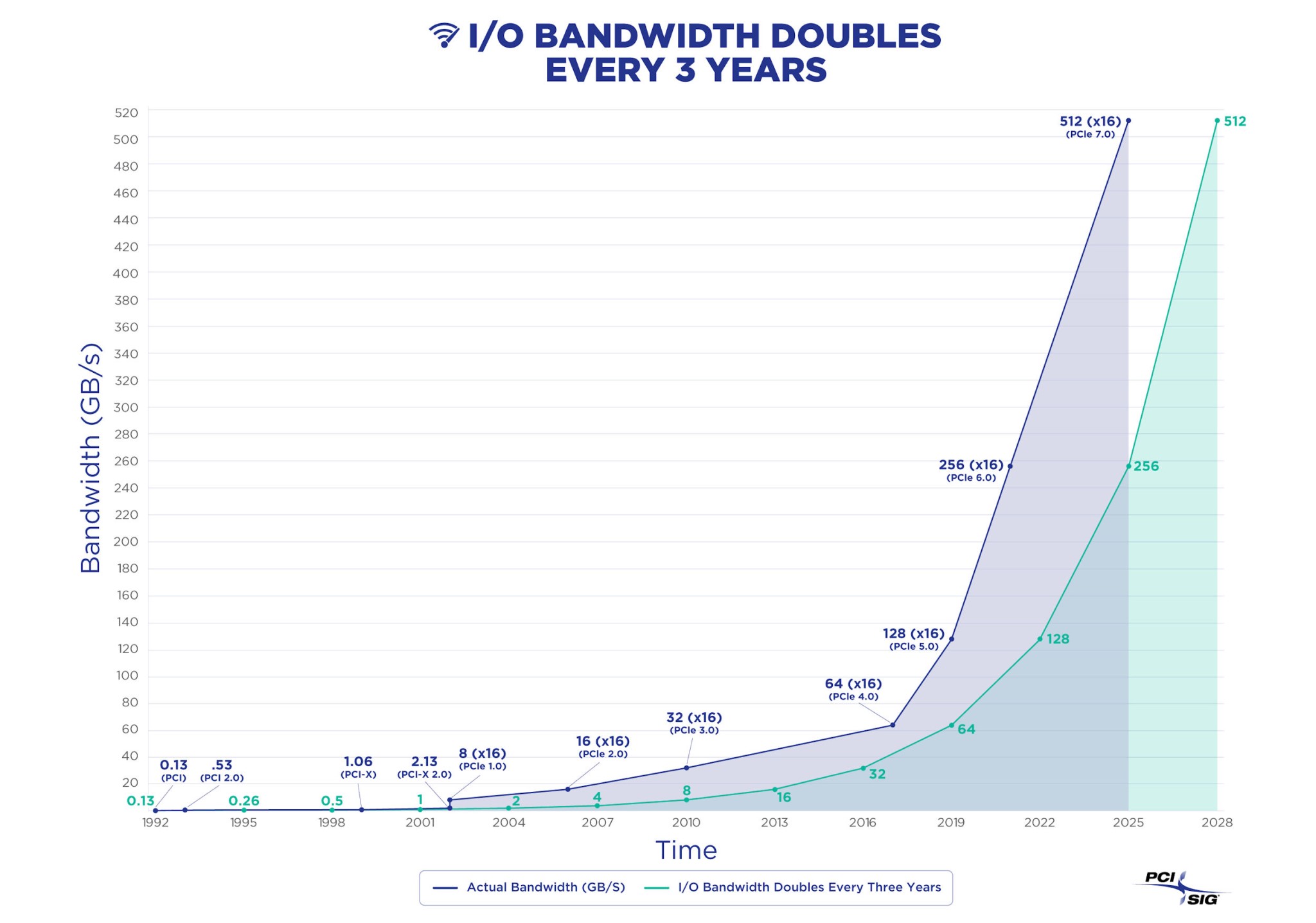

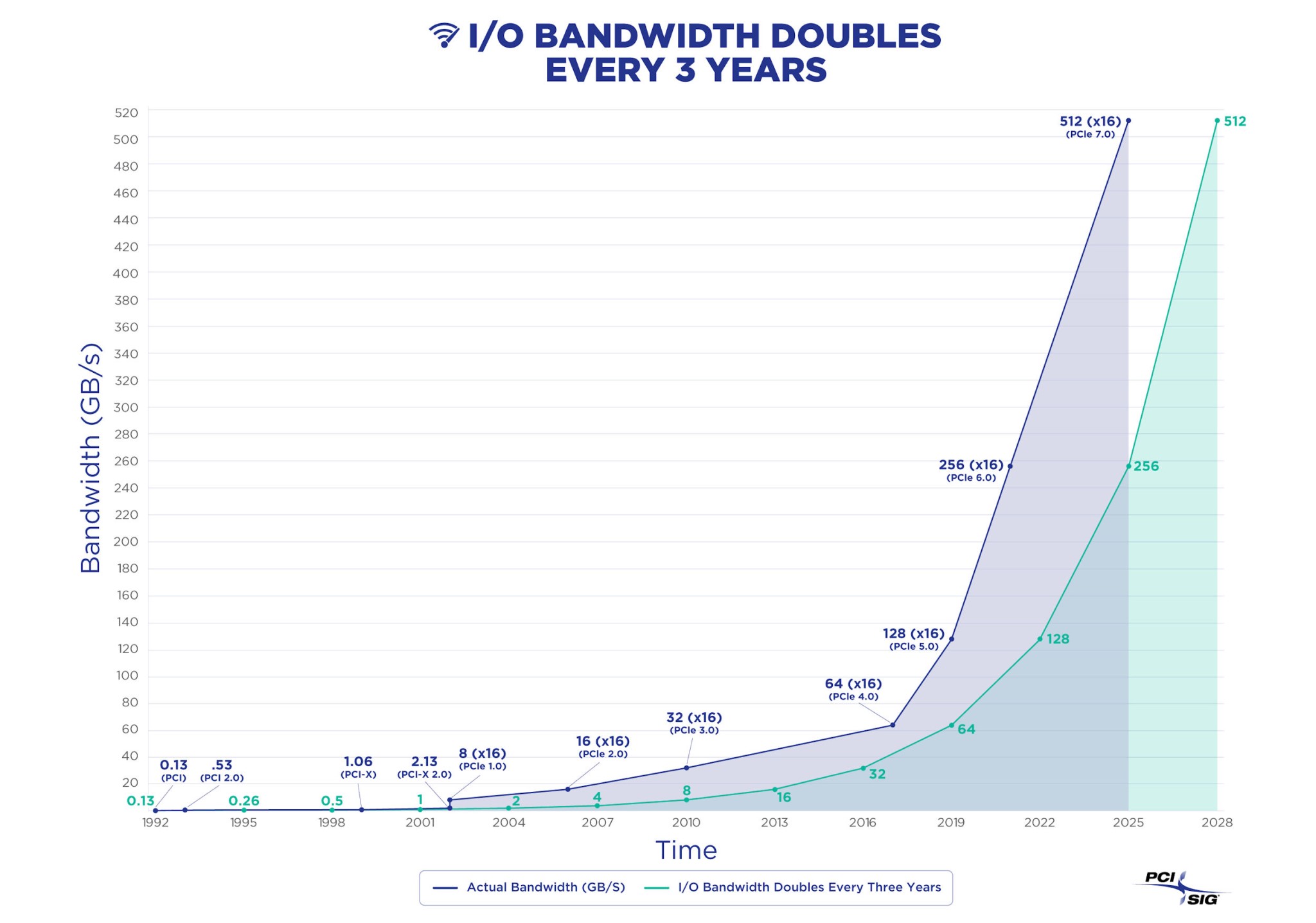

PCIe 5.0 còn chưa phổ biến, thế nhưng mà tổ chức chịu trách nhiệm thông qua tiêu chuẩn PCI Express - PCI-SIG - đã công bố thông số kỹ thuật của PCIe 7.0, theo kế hoạch ra mắt vào 2025. Theo đó, tốc độ truyền dữ liệu của PCI Express 7.0 sẽ đạt đến mức 128 GT/s (gigatransfer per second), tương đương 512 GBps thông lượng 2 chiều (bi-directional throughput) với kết nối x16.

Thông lượng 2 chiều 512 GBps là con số lý thuyết, trước khi mã hóa (encoding overhead) cũng như chưa tính ảnh hưởng từ hiệu suất header, vì vậy băng thông thực tế sẽ khác. Giao diện PCIe 7.0 vẫn sử dụng chế độ mã hóa FLIT (FLow control unIT) 1b/1b và công nghệ tín hiệu PAM4 (Pulse Amplitude Modulation) được giới thiệu với PCIe 6.0. Đây là những cải tiến mới so với mã hóa 128b/130b và tín hiệu NRZ (Non-Return-to-Zero) trên PCIe 3.0 đến PCIe 5.0 trước đó. Nhờ vậy, băng thông thực tế của PCIe 7.0 dù không đạt được mức 512 GBps lý thuyết nhưng vẫn tăng gấp đôi so với PCIe 6.0.

Trước đây khi chuyển sang PCIe 4.0 và PCIe 5.0, trace length (khoảng cách lớn nhất mà tín hiệu có thể truyền được) bị giảm xuống so với các thế hệ PCIe cũ, do tốc độ truyền tín hiệu được đẩy lên cao. PCIe 3.0 có trace length 16 - 20 inch, và PCIe 4.0 chỉ đạt được 10 - 12 inch, nếu độ dài đường dẫn tín hiệu vượt quá con số này, bất kể bộ phát và bộ thu có mạnh đến đâu, tín hiệu cũng không thể chuyển đi đến đích được. Để giải quyết vấn đề, người ta thêm vào 1 bộ phận gọi là retimer, hoạt động tương tự như 1 thiết bị mở rộng (extension device) hay repeater. Lớp vật lý này sẽ tinh chỉnh tín hiệu bằng cách sử dụng CTLE (Continuous Time Linear Equalization), DFE (Decision Feedback Equalization) và Tx FIR EQ (Transmit Final Impulse Response Equalization, hoặc gọi tắt là TxEQ).

PCIe 7.0 nhanh hơn gấp đôi so với PCIe 6.0, do đó trace length của nó còn ngắn hơn nữa. Chính vì vậy người ta phải bổ sung nhiều retimer hơn, PCB dày hơn, vật liệu chất lượng tốt hơn... khi thiết kế bo mạch chủ. Anh em chắc chắn sẽ thấy mức giá mainboard hỗ trợ PCIe 7.0 trong tương lai đắt hơn hẳn. Bù lại, việc mỗi làn PCIe (x1) có thông lượng 2 chiều đến 32 GBps, các thiết bị kết nối có thể không cần chiếm nhiều làn PCIe như hiện tại. Chẳng hạn 1 ổ SSD PCIe 5.0 cần giao tiếp x8 (64 GBps) thì với PCIe 7.0 chỉ cần giao tiếp x2 là đủ.

Card đồ họa, mainboard PCIe 5.0 đã có trên thị trường và SSD cũng rục rịch xuất hiện rồi. Với PCIe 6.0 được PCI-SIG hoàn thiện thông số kỹ thuật hồi đầu năm, Renesas tiên phong cung cấp những con chip PCIe 6.0 đầu tiên cho thiết bị thế hệ mới vào tháng 4. Tuy nhiên để người dùng có thể chạm tay vào những sản phẩm PCIe 6.0 đầu cuối thì còn khá lâu, và theo lộ trình đó, PCIe 7.0 sẽ còn lâu hơn nữa. Dự kiến PCI-SIG sẽ hoàn thiện thông số kỹ thuật PCIe 7.0 vào năm 2025, rồi tầm 3 năm sau, người dùng mới có thể trải nghiệm được thiết bị thế hệ mới.

Thông lượng 2 chiều 512 GBps là con số lý thuyết, trước khi mã hóa (encoding overhead) cũng như chưa tính ảnh hưởng từ hiệu suất header, vì vậy băng thông thực tế sẽ khác. Giao diện PCIe 7.0 vẫn sử dụng chế độ mã hóa FLIT (FLow control unIT) 1b/1b và công nghệ tín hiệu PAM4 (Pulse Amplitude Modulation) được giới thiệu với PCIe 6.0. Đây là những cải tiến mới so với mã hóa 128b/130b và tín hiệu NRZ (Non-Return-to-Zero) trên PCIe 3.0 đến PCIe 5.0 trước đó. Nhờ vậy, băng thông thực tế của PCIe 7.0 dù không đạt được mức 512 GBps lý thuyết nhưng vẫn tăng gấp đôi so với PCIe 6.0.

Trước đây khi chuyển sang PCIe 4.0 và PCIe 5.0, trace length (khoảng cách lớn nhất mà tín hiệu có thể truyền được) bị giảm xuống so với các thế hệ PCIe cũ, do tốc độ truyền tín hiệu được đẩy lên cao. PCIe 3.0 có trace length 16 - 20 inch, và PCIe 4.0 chỉ đạt được 10 - 12 inch, nếu độ dài đường dẫn tín hiệu vượt quá con số này, bất kể bộ phát và bộ thu có mạnh đến đâu, tín hiệu cũng không thể chuyển đi đến đích được. Để giải quyết vấn đề, người ta thêm vào 1 bộ phận gọi là retimer, hoạt động tương tự như 1 thiết bị mở rộng (extension device) hay repeater. Lớp vật lý này sẽ tinh chỉnh tín hiệu bằng cách sử dụng CTLE (Continuous Time Linear Equalization), DFE (Decision Feedback Equalization) và Tx FIR EQ (Transmit Final Impulse Response Equalization, hoặc gọi tắt là TxEQ).

PCIe 7.0 nhanh hơn gấp đôi so với PCIe 6.0, do đó trace length của nó còn ngắn hơn nữa. Chính vì vậy người ta phải bổ sung nhiều retimer hơn, PCB dày hơn, vật liệu chất lượng tốt hơn... khi thiết kế bo mạch chủ. Anh em chắc chắn sẽ thấy mức giá mainboard hỗ trợ PCIe 7.0 trong tương lai đắt hơn hẳn. Bù lại, việc mỗi làn PCIe (x1) có thông lượng 2 chiều đến 32 GBps, các thiết bị kết nối có thể không cần chiếm nhiều làn PCIe như hiện tại. Chẳng hạn 1 ổ SSD PCIe 5.0 cần giao tiếp x8 (64 GBps) thì với PCIe 7.0 chỉ cần giao tiếp x2 là đủ.

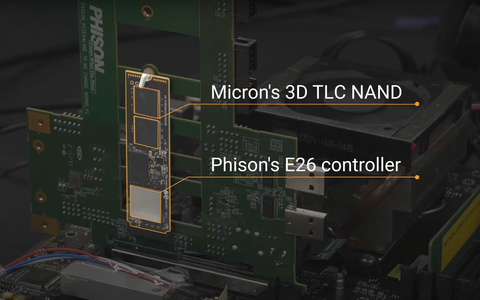

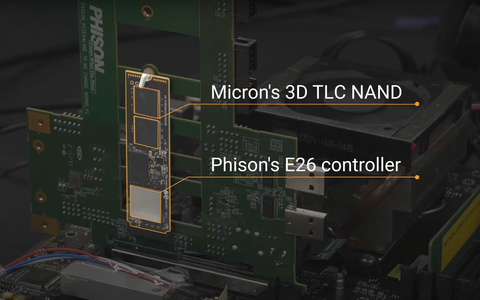

Anh em sắp có ổ SSD PCIe 5.0 với tốc độ đọc lên đến 12 GBps, ghi 10 GBps

Mẫu SSD tham chiếu của Phison có băng thông đọc ghi tuần tự lên đến 12 GBps và 10 GBps. Tuy nhiên, sản phẩm thử nghiệm này sử dụng kích thước khác với các SSD đang có trên thị trường và sử dụng PCIe 5.0 chưa phổ biến.

tinhte.vn

Card đồ họa, mainboard PCIe 5.0 đã có trên thị trường và SSD cũng rục rịch xuất hiện rồi. Với PCIe 6.0 được PCI-SIG hoàn thiện thông số kỹ thuật hồi đầu năm, Renesas tiên phong cung cấp những con chip PCIe 6.0 đầu tiên cho thiết bị thế hệ mới vào tháng 4. Tuy nhiên để người dùng có thể chạm tay vào những sản phẩm PCIe 6.0 đầu cuối thì còn khá lâu, và theo lộ trình đó, PCIe 7.0 sẽ còn lâu hơn nữa. Dự kiến PCI-SIG sẽ hoàn thiện thông số kỹ thuật PCIe 7.0 vào năm 2025, rồi tầm 3 năm sau, người dùng mới có thể trải nghiệm được thiết bị thế hệ mới.