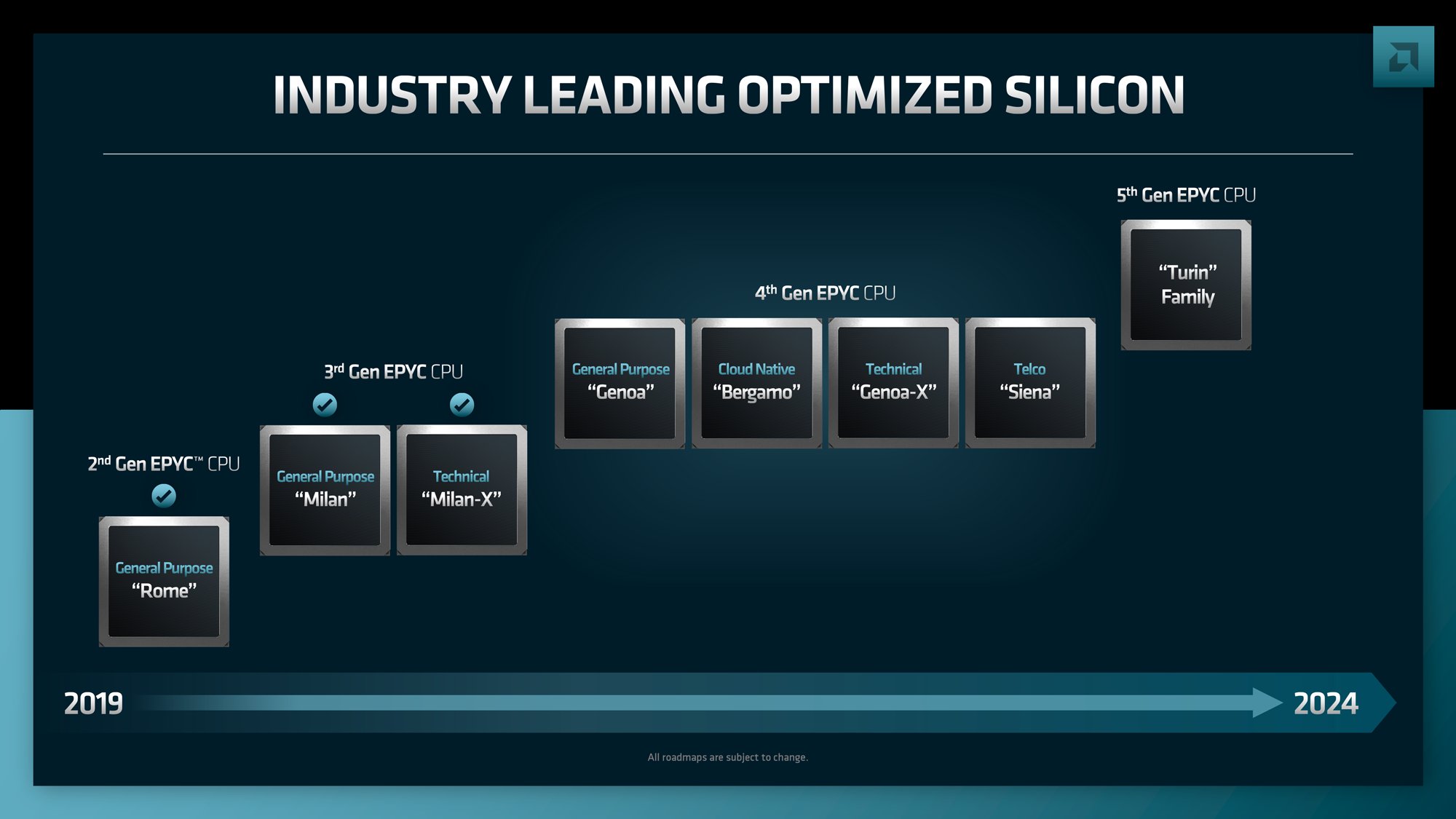

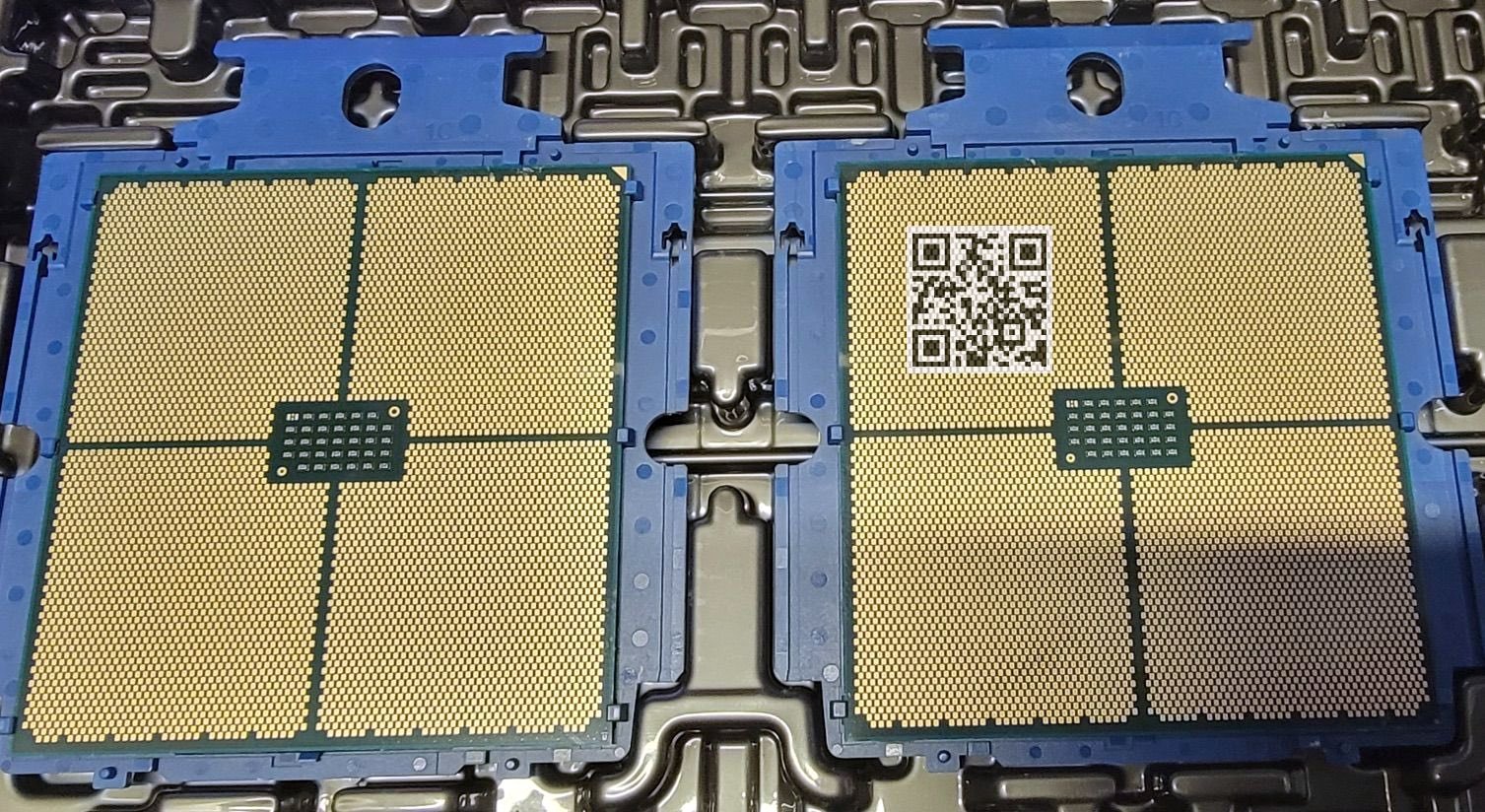

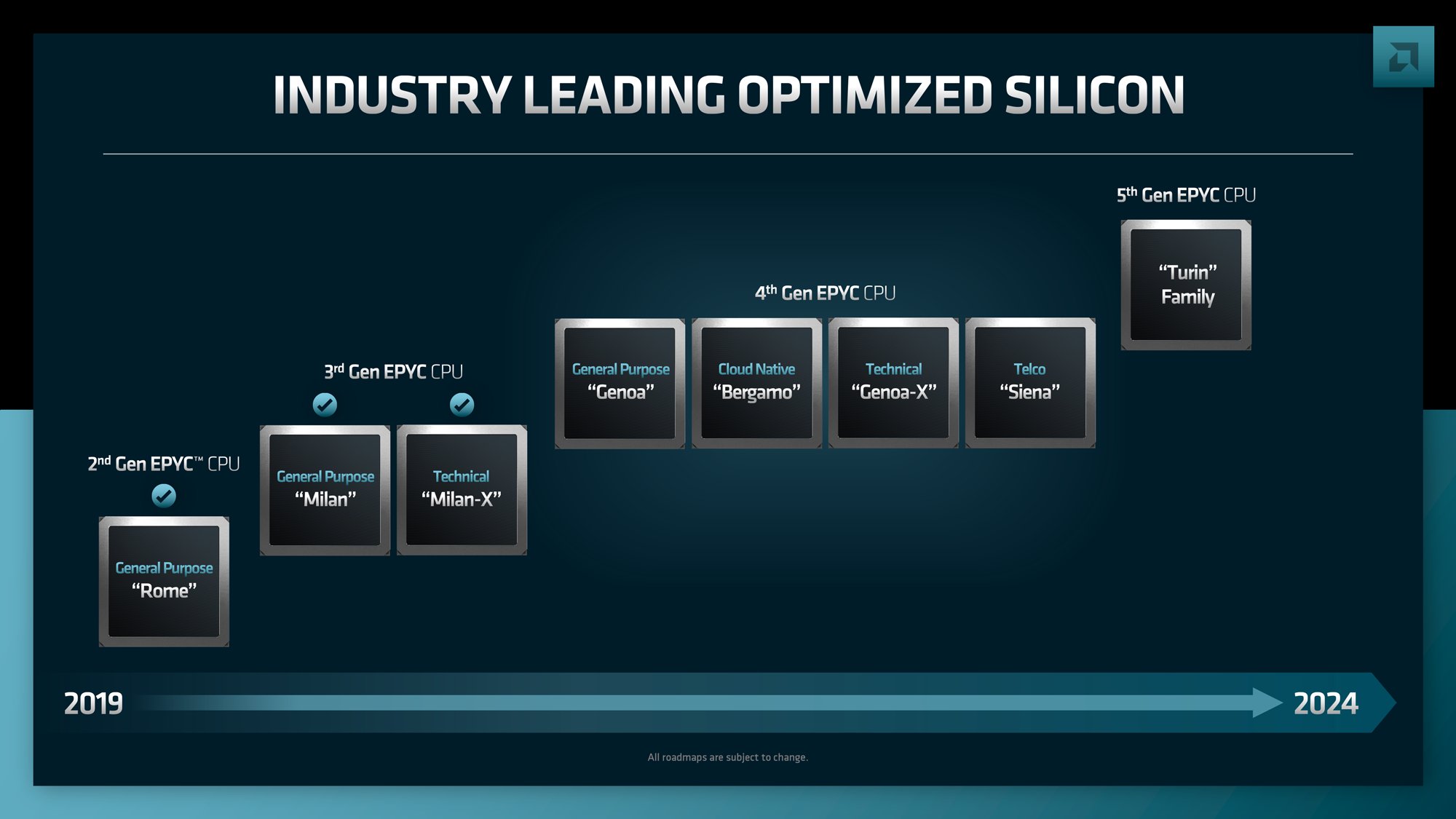

Mặc dù đợt ra mắt vi xử lý Xeon Scalable thế hệ 5 “Emerald Rapids” của Intel mới đây có chút ấn tượng khi cho thấy sự trở lại của phe xanh, nhưng có lẽ nó vẫn chưa đủ để qua mặt được các chip EPYC Zen 4/4c. Dĩ nhiên phe đỏ cũng sẽ không ngồi im khi mới đây, thông tin và hình ảnh rò rỉ trên Twitter/X cho thấy thế hệ chip server tiếp theo của AMD đã bước sang giai đoạn engineering sample (ES). Nếu mọi thứ đúng như kế hoạch ban đầu thì loạt vi xử lý EPYC Turin mới này sẽ được ra mắt trong năm 2024.

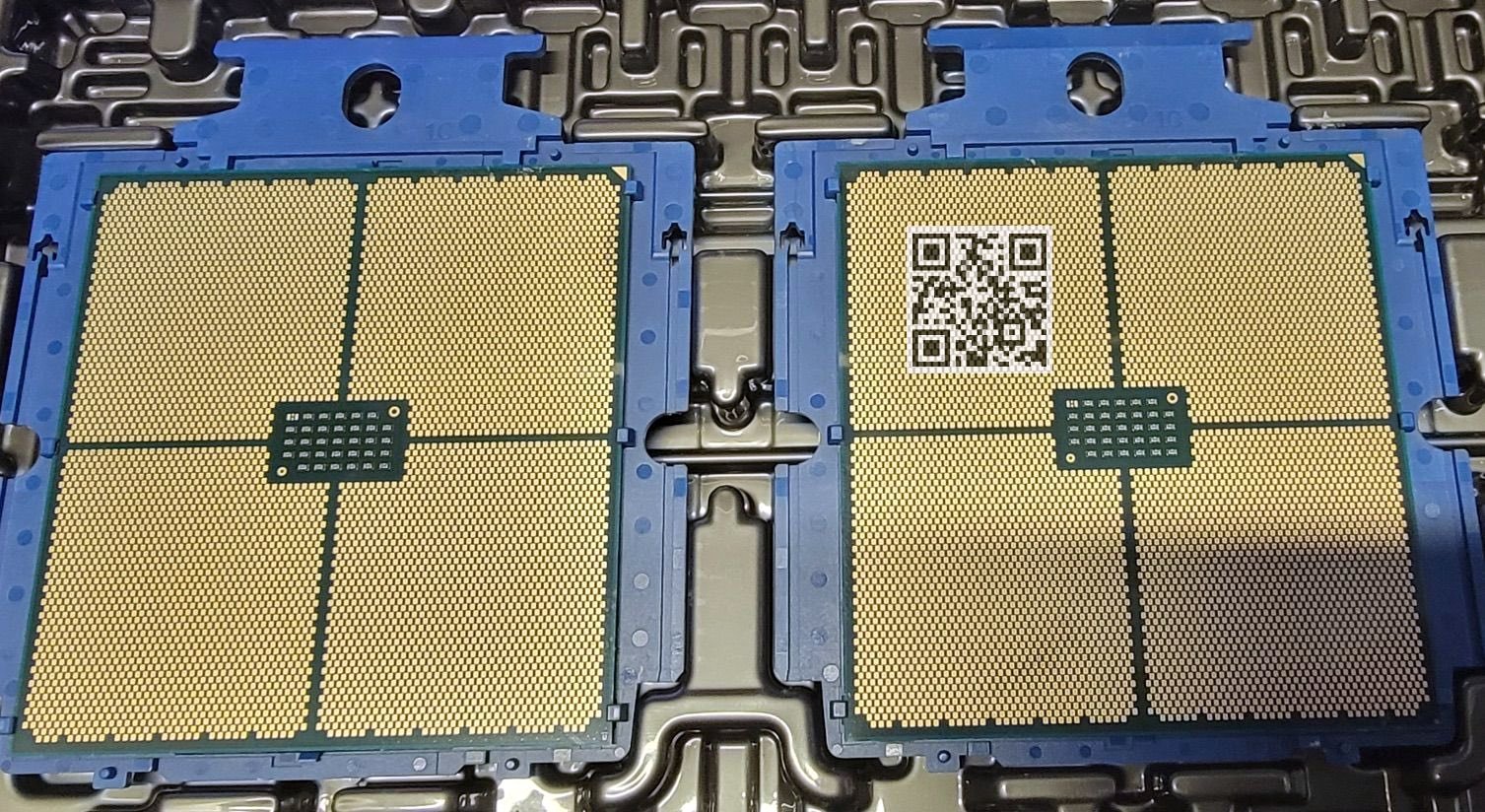

Theo những thông tin sơ bộ, Turin hay tên mã của dòng chip EPYC thế hệ 5 này sẽ dùng chung kiểu đóng gói như thế hệ 4 hiện tại. Chúng vẫn sử dụng socket SP5 và có lẽ vẫn tương thích với các mainboard có sẵn (nhưng tất nhiên update BIOS là việc cần thiết). Điểm khác biệt chính giữa Genoa và Turin là Turin sẽ được sản xuất trên tiến trình N4/N4P của TSMC, cho phép AMD "nhồi nhét" được nhiều transistor hơn so với tiến trình N5 của thế hệ trước.

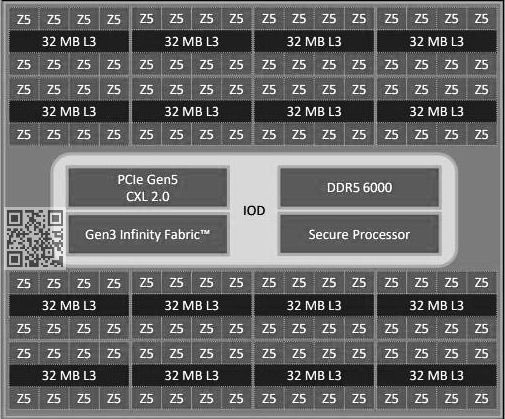

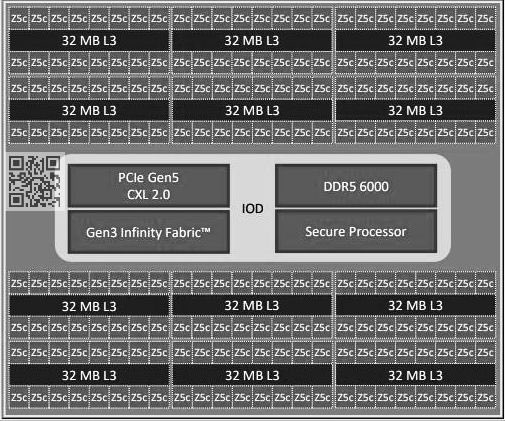

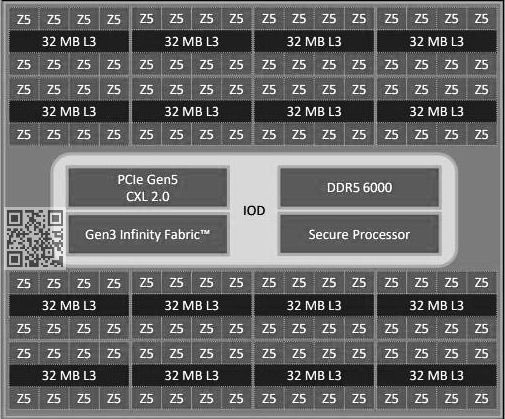

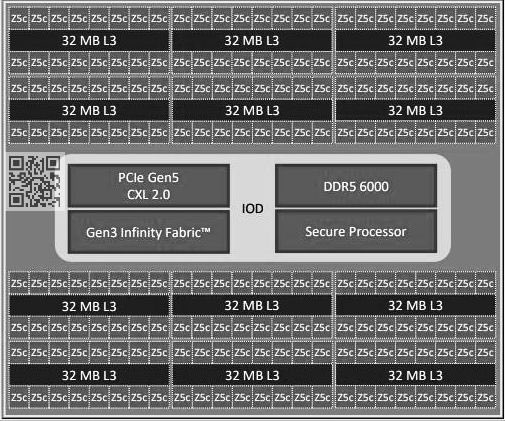

Rò rỉ diagram Turin Zen5 và Zen 5c

Dựa vào ảnh sơ đồ cấu tạo, có thể thấy Turin sẽ có ít nhất 2 kiểu thiết kế - Zen 5 và Zen 5c. Tương tự Zen 4 và 4c, Zen 5c dường như là bản rút gọn - "compact" của Zen 5 với kiến trúc tương tự nhưng xung nhịp và bộ đệm bị giới hạn. Do đó 1 CCD Zen 5c sẽ có số lượng nhân lên tới 16, nhiều gấp đôi 1 CCD Zen 5. Tuy vậy CCD Zen 5c sẽ bự hơn CCD Zen 5 nên con chip Turin 5c chỉ "nhét" tối đa được 12 CCD (192 nhân), so với 16 CCD trên Turin 5 (128 nhân). Các con số này trên Genoa (Zen 4) và Bergamo (Zen 4c) và 96 và 128 nhân.

Không có nhiều thông tin về die sIOD quản lý tất cả các kết nối I/O với hệ thống, nhưng có vẻ cả 2 thiết kế Turin 5 và 5c sẽ dùng chung một die sIOD. Die này sẽ hỗ trợ các giao tiếp phổ biến nhất như PCI Express 5.0 (CXL 2.0), DDR-6000, Infinity Fabric thế hệ 3 và bộ xử lý bảo mật riêng.

Tới đây tuy chưa rõ kiến trúc Zen 5 sẽ như thế nào nhưng ít nhất, chúng ta có thể thấy 2024 là một năm rất "căng thẳng" trong trận đấu server giữa AMD và Intel.

Theo những thông tin sơ bộ, Turin hay tên mã của dòng chip EPYC thế hệ 5 này sẽ dùng chung kiểu đóng gói như thế hệ 4 hiện tại. Chúng vẫn sử dụng socket SP5 và có lẽ vẫn tương thích với các mainboard có sẵn (nhưng tất nhiên update BIOS là việc cần thiết). Điểm khác biệt chính giữa Genoa và Turin là Turin sẽ được sản xuất trên tiến trình N4/N4P của TSMC, cho phép AMD "nhồi nhét" được nhiều transistor hơn so với tiến trình N5 của thế hệ trước.

Rò rỉ diagram Turin Zen5 và Zen 5c

Dựa vào ảnh sơ đồ cấu tạo, có thể thấy Turin sẽ có ít nhất 2 kiểu thiết kế - Zen 5 và Zen 5c. Tương tự Zen 4 và 4c, Zen 5c dường như là bản rút gọn - "compact" của Zen 5 với kiến trúc tương tự nhưng xung nhịp và bộ đệm bị giới hạn. Do đó 1 CCD Zen 5c sẽ có số lượng nhân lên tới 16, nhiều gấp đôi 1 CCD Zen 5. Tuy vậy CCD Zen 5c sẽ bự hơn CCD Zen 5 nên con chip Turin 5c chỉ "nhét" tối đa được 12 CCD (192 nhân), so với 16 CCD trên Turin 5 (128 nhân). Các con số này trên Genoa (Zen 4) và Bergamo (Zen 4c) và 96 và 128 nhân.

Không có nhiều thông tin về die sIOD quản lý tất cả các kết nối I/O với hệ thống, nhưng có vẻ cả 2 thiết kế Turin 5 và 5c sẽ dùng chung một die sIOD. Die này sẽ hỗ trợ các giao tiếp phổ biến nhất như PCI Express 5.0 (CXL 2.0), DDR-6000, Infinity Fabric thế hệ 3 và bộ xử lý bảo mật riêng.

Tới đây tuy chưa rõ kiến trúc Zen 5 sẽ như thế nào nhưng ít nhất, chúng ta có thể thấy 2024 là một năm rất "căng thẳng" trong trận đấu server giữa AMD và Intel.