Trong một bài viết trước, chúng ta được biết dây chuyền bán dẫn tiên tiến nhất của Intel có hiệu suất chỉ 10%. Đây là một con số rất tệ để có thể đi vào sản xuất hàng loạt. Tuy vậy, hiệu suất là con số mang tính tương đối vì nó lệ thuộc vào nhiều yếu tố, cụ thể là kích thước die chip. Trong bài này, chúng ta phân tích rõ hơn ý nghĩa con số trên và những gì có thể xảy đến trong tương lai.

Đối với kỹ thuật in lithography, một chi tiết quan trọng quyết định tới hiệu suất (yield) bán dẫn là mật độ lỗi (defect density hay defect rate hay D0). Thông thường nó được đo bằng số lỗi trên một cm^2 (def/cm^2). Đối với tiến trình Intel 18A, theo chia sẻ của CEO Pat Gelsinger hồi còn tại chức, giá trị D0 này là 0.4 def/cm^2. Tức cứ 2.5 cm^2 thì xuất hiện 1 hạt lỗi. Nhưng đây là con số được công bố hồi tháng 9/2024. Có nghĩa trên lý thuyết hiện tại giá trị D0 này sẽ thấp hơn 0.4 nhiều.

Đối với ngành bán dẫn nói chung, hệ số D0 được xem là "ổn" để đi vào sản xuất là 0.5, tức cứ 2 cm^2 mới có 1 hạt lỗi. Nhưng của Intel 18A là 0.4. Vậy mọi thứ đã "sai" chỗ nào?

Có 2 vấn đề cần bàn. (1) D0 là giá trị trung bình. (2) con chip được sản xuất có kích thước cỡ nào?

Đối với kỹ thuật in lithography, một chi tiết quan trọng quyết định tới hiệu suất (yield) bán dẫn là mật độ lỗi (defect density hay defect rate hay D0). Thông thường nó được đo bằng số lỗi trên một cm^2 (def/cm^2). Đối với tiến trình Intel 18A, theo chia sẻ của CEO Pat Gelsinger hồi còn tại chức, giá trị D0 này là 0.4 def/cm^2. Tức cứ 2.5 cm^2 thì xuất hiện 1 hạt lỗi. Nhưng đây là con số được công bố hồi tháng 9/2024. Có nghĩa trên lý thuyết hiện tại giá trị D0 này sẽ thấp hơn 0.4 nhiều.

Đối với ngành bán dẫn nói chung, hệ số D0 được xem là "ổn" để đi vào sản xuất là 0.5, tức cứ 2 cm^2 mới có 1 hạt lỗi. Nhưng của Intel 18A là 0.4. Vậy mọi thứ đã "sai" chỗ nào?

Có 2 vấn đề cần bàn. (1) D0 là giá trị trung bình. (2) con chip được sản xuất có kích thước cỡ nào?

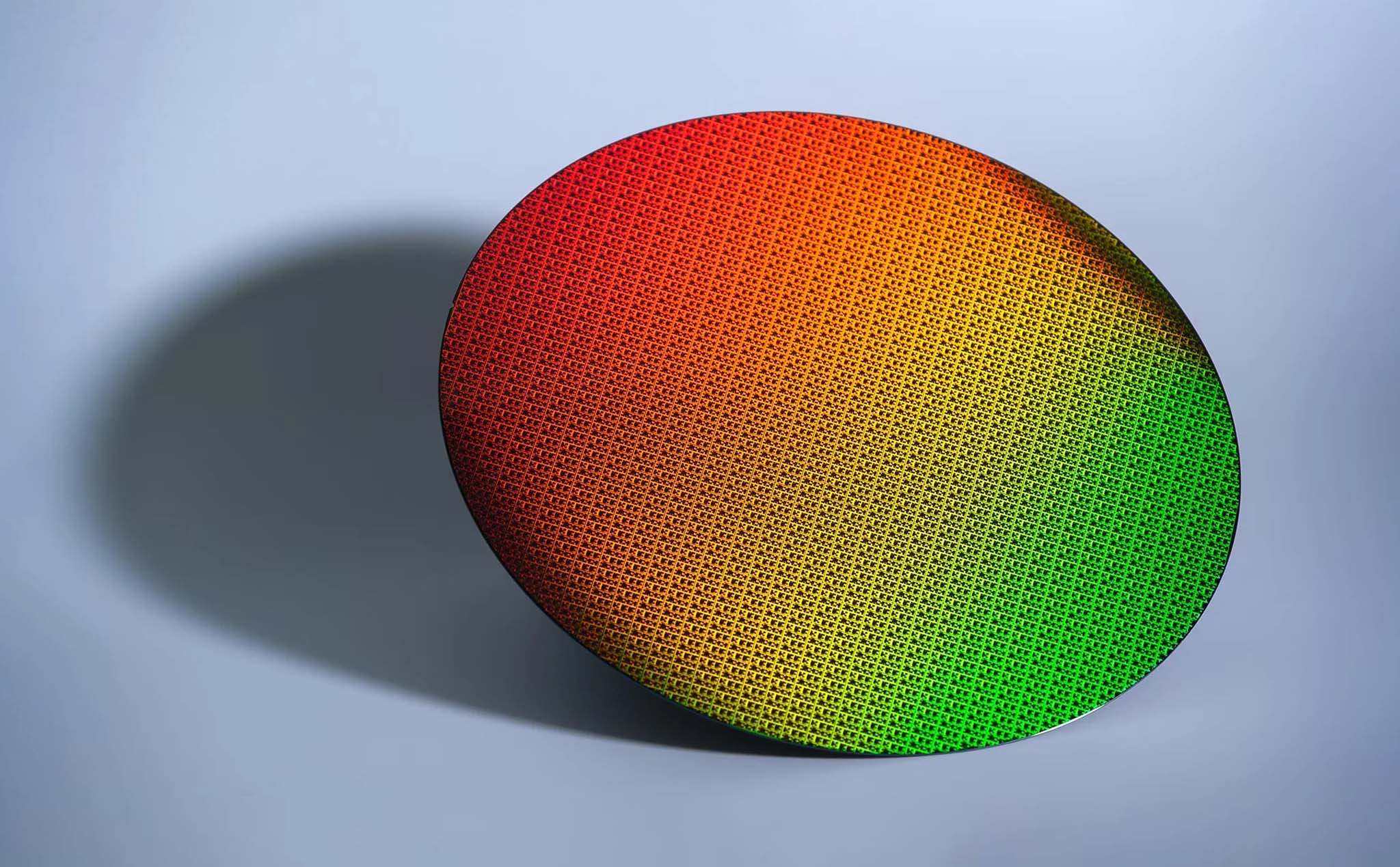

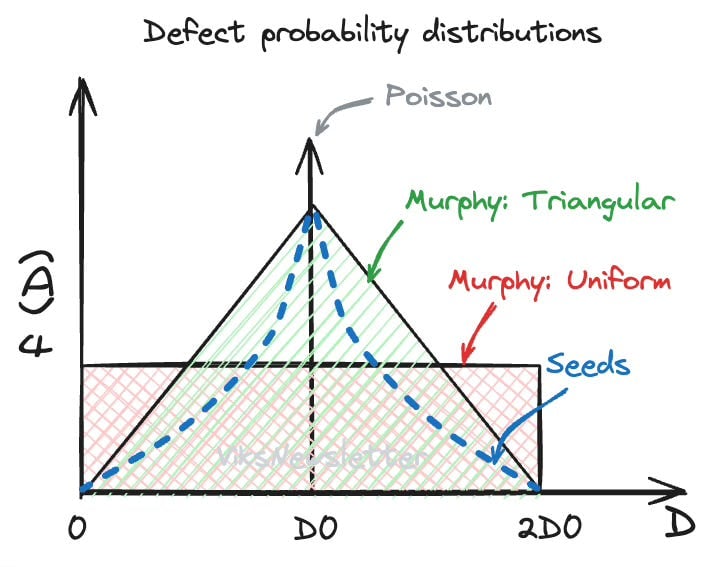

Một số mô hình phân bổ hạt lỗi trên wafer bán dẫn

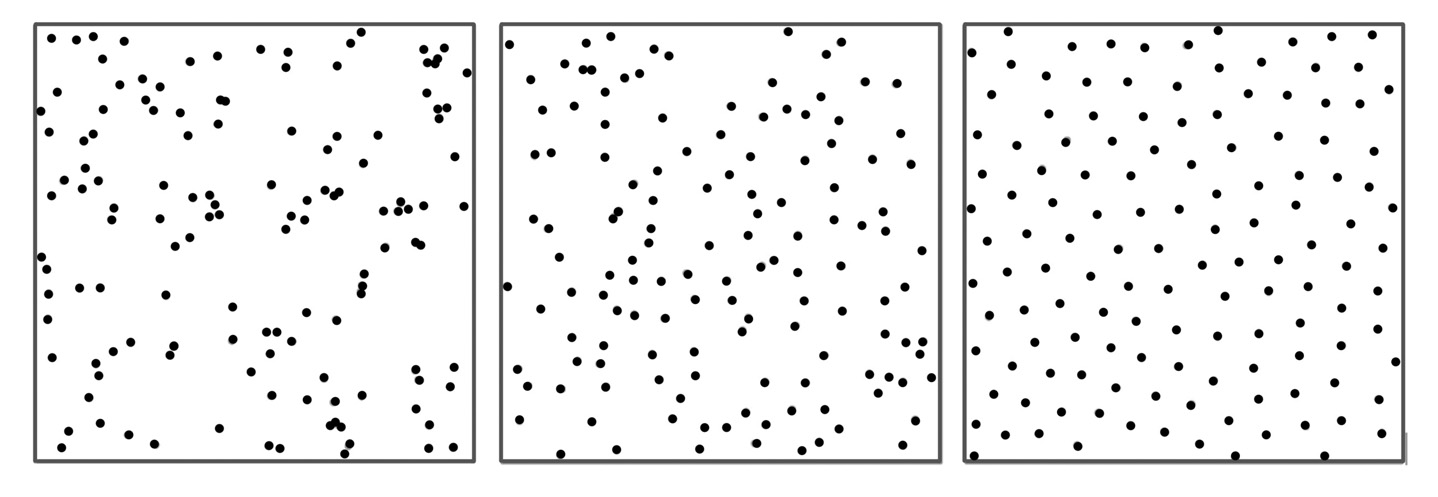

Ở vấn đề (1), chúng ta cần nói chút về cơ học lượng tử hay xác suất thống kê. D0 thực tế là sự chia đều tổng số hạt lỗi trên toàn bộ tấm wafer, không có nghĩa cứ nhất định các hạt lỗi sẽ luôn cách đều nhau 1 khoảng như vậy (2.5 cm^2 trong trường hợp Intel 18A). Sẽ có tình huống một khoảng 2.5 cm^2 chứa nhiều hạt và có khoảng không chứa hạt lỗi nào. Sự phân bổ hạt lỗi là ngẫu nhiên và nó cơ bản là một bài toán xác suất. Chúng ta có một số mô hình phân bổ hạt lỗi có thể chia theo "cấp độ" từ "tệ nhất" (Poisson) cho tới "lạc quan nhất" (Seeds). Dĩ nhiên các mô hình chỉ là công cụ để "dự đoán", không chắc chắn sẽ đúng thực tế 100% nhưng chúng cho chúng ta cái nhìn sơ bộ về hiệu suất thực tế có thể đạt được.

Vấn đề (2) như đã nêu từ trước, là kích thước con chip. Nó cũng tuân theo quy luật xác suất. Nguyên lý bất định nói rằng chúng ta không thể biết chắc chắn cùng lúc tất cả các thuộc tính của vật chất, hoặc là vị trí, hoặc là tốc độ. Và hệ quả của nguyên lý này là kích thước lấy mẫu càng lớn thì khả năng "dương tính" càng cao. Một diện tích nhỏ như 2 cm^2 sẽ ít có khả năng gặp hạt lỗi hơn là một diện tích lớn như 5 cm^2, 10 cm^2. Nói đơn giản là chip càng bự thì càng dễ dính hạt lỗi và ngược lại.

Với cơ học lượng tử, không có gì là chắc chắn

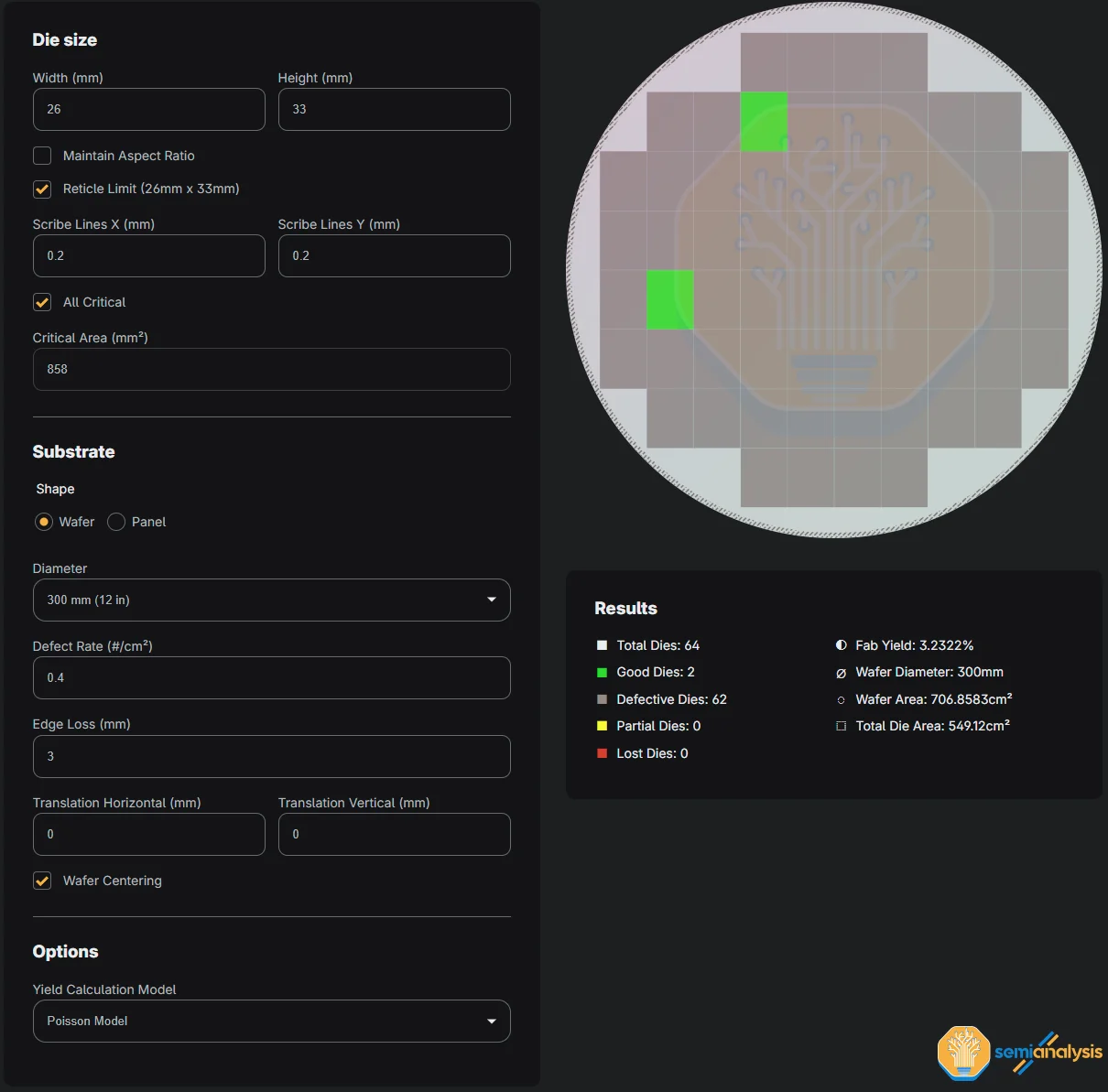

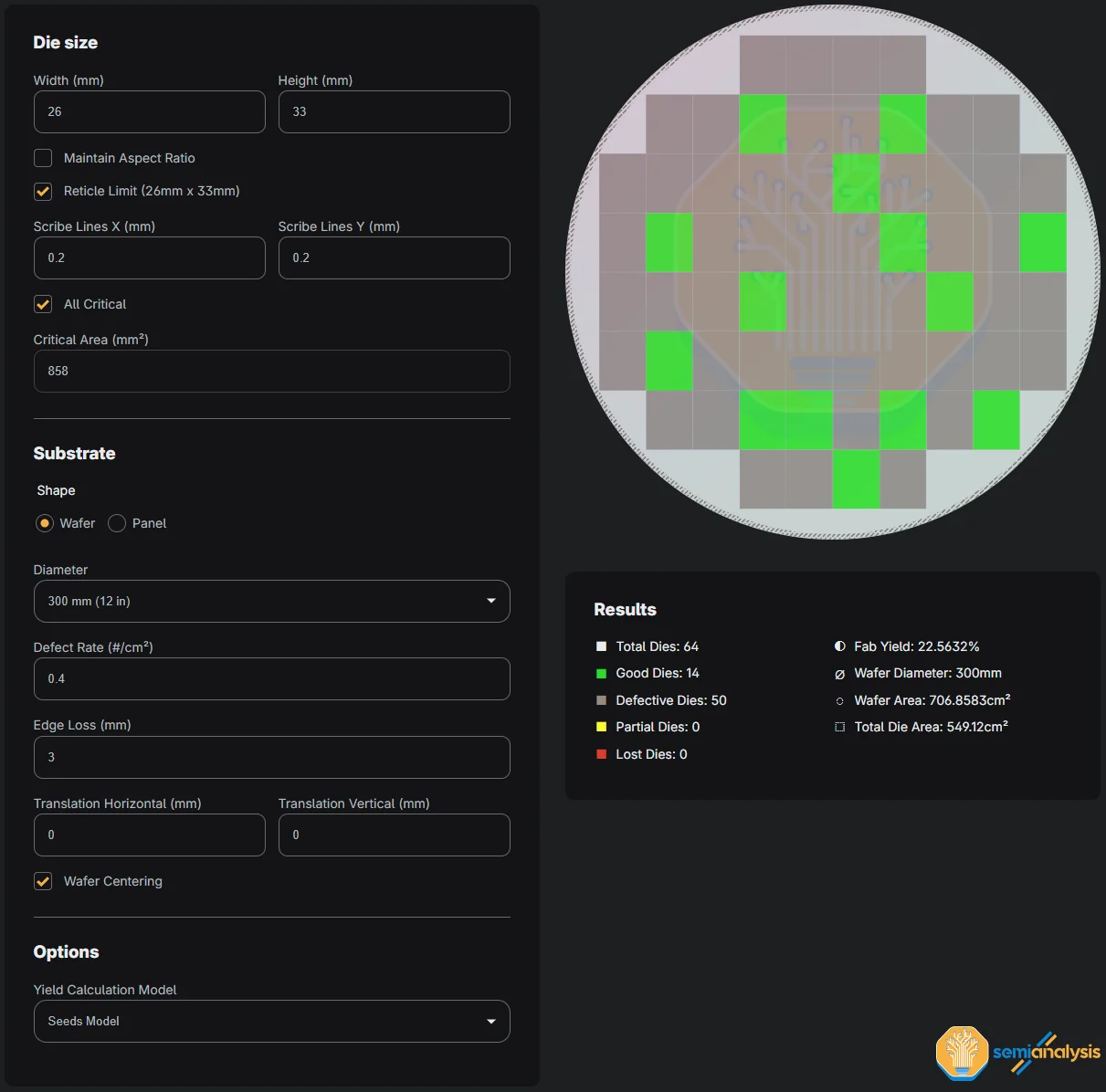

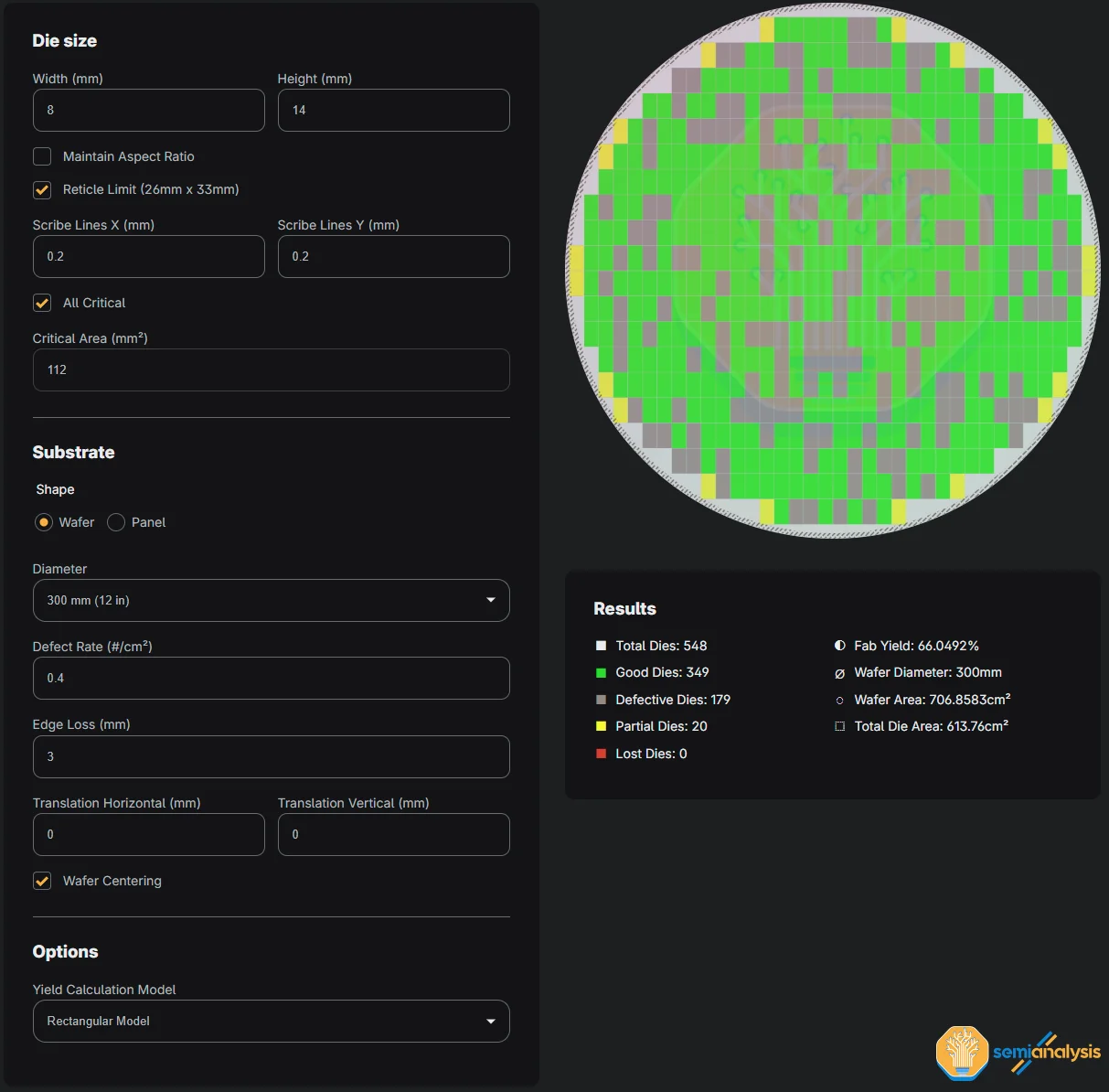

Vậy node Intel 18A thì thế nào? Cách tốt nhất để hình dung vấn đề này là một công cụ chuyên dụng để mô phỏng hiệu suất bán dẫn. Ở đây chúng ta có SemiAnalysis Die Yield Calculator, bạn có thể tự tay kiểm chứng.

Nhưng trước khi đi vào chi tiết, bạn cần nắm một số vấn đề:

- Kích thước chip (Width x Height) là chiều cao và chiều rộng mà con chip bạn muốn sản xuất

- Giới hạn reticle - mỗi tiến trình lithography sẽ có kích thước reticle/photomask tối đa cho phép. Bạn không thể in ra con chip lớn hơn giới hạn này (trừ phi dùng chiplet). Với EUV, giới hạn này là 26 x 33 mm

- Cự ly giữa các chip (Scribe) là khoảng cách tối thiểu để tách die này với die kia. Bạn cần có cự ly này để phục vụ quá trình cắt die sau khi xử lý xong wafer

- Hình dạng (Shape) và kích thước wafer (đường kính). Wafer chủ yếu có hình tròn và cỡ tiêu chuẩn hiện nay từ 200 - 300 mm (vẫn có các hãng gia công dùng wafer bé hơn, nên vẫn cần tính hiệu suất)

- Mật độ lỗi (D0) như đã nêu ở trên

- Lượng silicon mất ở rìa (Edge Loss). Cần con số này vì các die chip ở ngoài cùng sẽ bị "ăn" mất góc

- Mô hình hiệu suất hoặc phân bổ lỗi. Bạn chọn tương ứng tuỳ theo Poisson, Murphy, Rectangular, Moore, Seeds

Quảng cáo

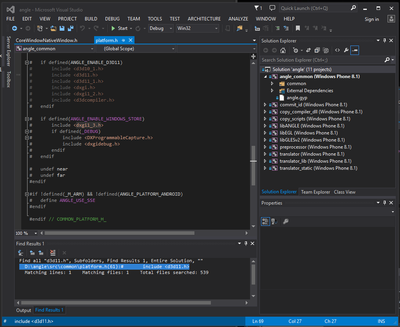

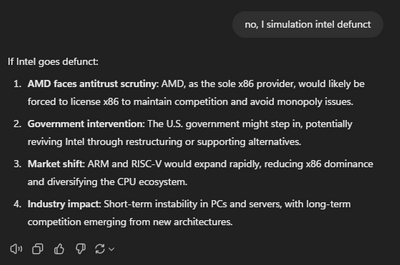

Sau khi nắm hết các thông số trên, chúng ta có thể bắt đầu "vọc" xem node Intel 18A "ngon" hay "dở". Thực tế hầu hết các thông số là giữ nguyên, chúng ta chỉ thay đổi kích thước chip, mật độ lỗi và mô hình hiệu suất. Trước tiên, hãy thử với con chip bự bằng đúng kích thước reticle EUV (26 x 33 mm), D0 0.4. Thay đổi lần lượt 5 mô hình hiệu suất và bạn có thể thấy mọi thứ chênh lệch đến mức nào, từ 3.2% (tệ nhất) cho tới 22.6% (tốt nhất).

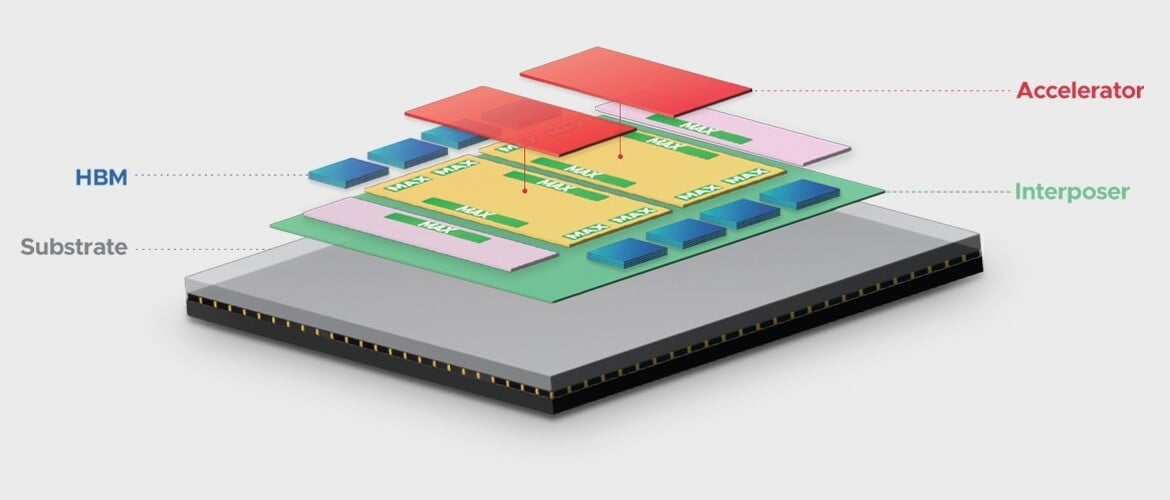

Cùng kích thước die chip, hệ số D0 nhưng khác mô hình vẫn cho hiệu suất khác nhau

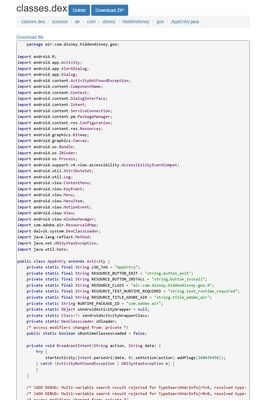

Nhắc lại một chút câu chuyện hợp đồng gia công chip với Broadcom. Thực tế chúng ta không rõ công ty này đã yêu cầu Intel gia công con chip bự đến thế nào. Song các sản phẩm của Broadcom gần đây nếu có liên quan tới AI đều có kích thước rất lớn. Model 3.5D XDSiP mới nhất của hãng có tổng diện tích tới 6000 mm^2, với phần silicon logic lên tới 2500 mm^2 (phần còn lại là chip nhớ HBM)! Không lâu trước đó, OpenAI cho biết họ đã hợp tác với Broadcom để làm chip AI do TSMC gia công. Được biết D0 của TSMC trên N7 và N5 khi vừa ra mắt đạt 0.33 (hiện tại có thể chỉ còn 0.1). Bạn có thể "nghịch" nốt nếu thích.

Con chip 6000 mm^2 của Broadcom

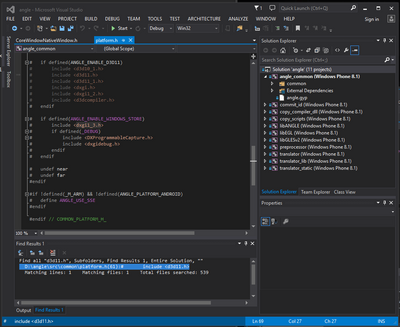

Vấn đề cần nói ở chỗ, không phải ai cũng có nhu cầu làm ra con chip siêu to siêu khổng lồ. Trừ số ít sản phẩm hàng đầu ra còn lại đa số chip có kích thước vừa và nhỏ. Ví dụ như chip Ryzen/EPYC của AMD, mỗi die chiplet khá gọn (chiplet Zen 4/5 chỉ có 71 mm^2). Hay như die chip Raptor Lake của Intel to hơn khá nhiều tới 208 mm^2 (23.8 x 10.8 mm). Bạn có thể tự nhập thông số này vào công cụ trên, áp dụng chung D0 0.4 để thấy được vấn đề. Kể cả mô hình tệ nhất thì hiệu suất cũng không dưới 30%.

Quảng cáo

Ngay cả ở D0 0.4, Intel 18A vẫn đủ "tốt" để sản xuất chip bé

Được biết mẫu chip sắp tới của Intel, Panther Lake, theo "đo lường" của các "chuyên gia" Photoshop, có kích thước vào khoảng 8 x 14 mm (112 mm^2). Cứ cho D0 của Intel 18A "dậm chân tại chỗ" ở 0.4 thì với mô hình tệ nhất, hiệu suất vẫn trên 50%. Có nghĩa tiến trình này không hề tệ như thông tin ban đầu chúng ta nhận được (nó vẫn tệ với các con chip bự nhưng đấy chỉ là một nửa ổ bánh mỳ).

Samsung và TSMC đang "vật vã" với tiến trình 3 nm

Mặc dù cùng tuyên bố đi vào sản xuất hàng loạt chip 3 nm từ năm ngoái, nhưng tới nay cả Samsung lẫn TSMC vẫn đang chật vật trong việc đạt được hiệu suất sản xuất mong muốn.

Theo nguồn tin ChosunBiz của Hàn, Samsung và TSMC cùng gặp khó khăn...

tinhte.vn

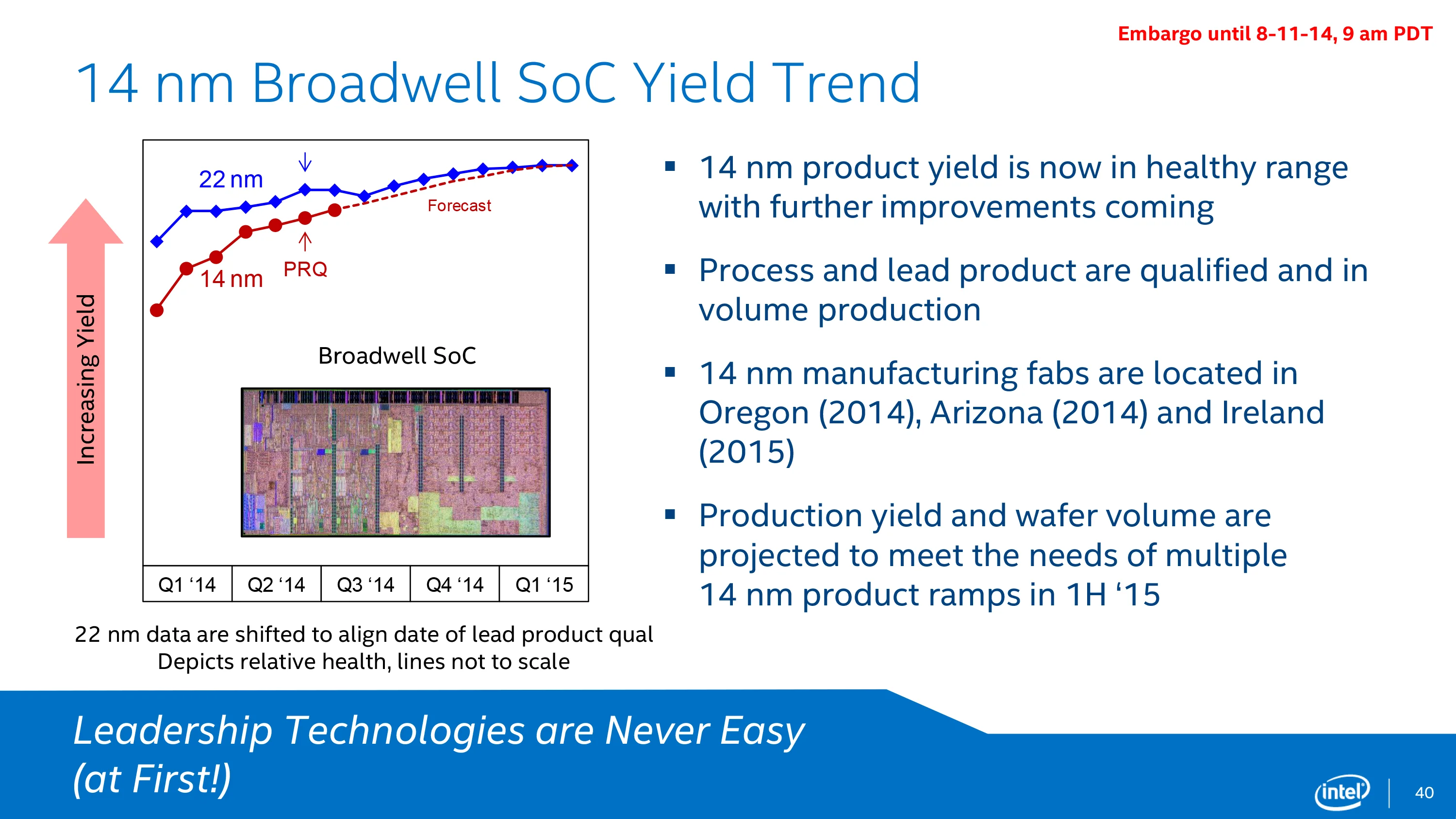

Tổng quan lại thì không riêng Intel mà bất kỳ hãng gia công nào, chip bự vẫn luôn có hiệu suất thấp hơn chip nhỏ. Còn nhớ hơn 10 năm trước, TSMC cũng từng gặp trục trặc ở 40 nm, khiến cho cả AMD lẫn NVIDIA phải lao đao vì không đủ sản lượng GPU bán ra thị trường. Cách đây không lâu, TSMC lẫn Samsung đều cùng gặp vất vả trong việc cải thiện hiệu suất 3 nm, cho thấy mọi tiến trình bán dẫn, lúc khởi đầu bao giờ cũng gian nan. Nên việc Intel 18A chưa được tốt cách đây vài tháng cũng là điều dễ hiểu.

Cải thiện hiệu suất là vấn đề cần có thời gian