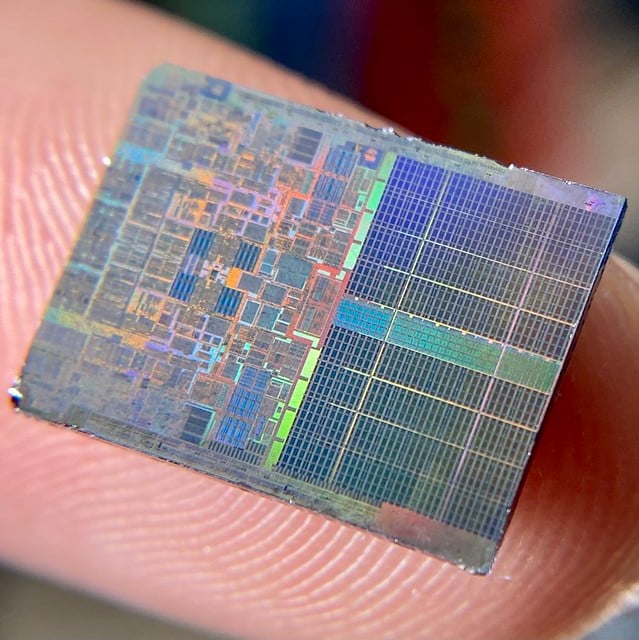

Lời dẫn: Tất cả chúng ta đều coi CPU là bộ não của hệ thống máy tính, từ máy bàn tới laptop, từ máy chủ tới điện thoại. Nhưng “bộ não” ấy có ý nghĩa gì? Bên trong một die silicon với hàng tỷ transistor vận hành ra sao để cỗ máy tính của chúng ta hoạt động?

Trong loạt bài viết 4 phần này, chúng ta sẽ tập trung vào thiết kế phần cứng chip xử lý máy tính, từ kiến trúc tập lệnh cho tới thiết kế transistor khiến những thiết bị công nghệ trong tay anh em vận hành như ý muốn. Rồi kế đến là cả những lý thuyết như thiết kế vi mạch bán dẫn, VLSI (tích hợp cỡ rất lớn), gia công bán dẫn, rồi cả những xu hướng trong tương lai của chip vi xử lý nữa.

Phần 1: Cơ bản kiến trúc chip xử lý máy vi tính

Phần 2: Quy trình thiết kế chip CPU

Phần 3: Dàn bề mặt và quang khắc chip CPU

Phần 4: Xu hướng tương lai, và những chủ đề nóng của kiến trúc chip xử lý máy tính

Trong loạt bài viết 4 phần này, chúng ta sẽ tập trung vào thiết kế phần cứng chip xử lý máy tính, từ kiến trúc tập lệnh cho tới thiết kế transistor khiến những thiết bị công nghệ trong tay anh em vận hành như ý muốn. Rồi kế đến là cả những lý thuyết như thiết kế vi mạch bán dẫn, VLSI (tích hợp cỡ rất lớn), gia công bán dẫn, rồi cả những xu hướng trong tương lai của chip vi xử lý nữa.

Phần 1: Cơ bản kiến trúc chip xử lý máy vi tính

Phần 2: Quy trình thiết kế chip CPU

Phần 3: Dàn bề mặt và quang khắc chip CPU

Phần 4: Xu hướng tương lai, và những chủ đề nóng của kiến trúc chip xử lý máy tính

Thực tế nhiệm vụ của chip CPU là gì?

Hãy bắt đầu luôn ở ngưỡng kiến thức cao cấp, về việc một con chip CPU làm gì, và những khối kiến trúc cơ bản kết hợp lại ra sao để thành một thiết kế vận hành xử lý được những phép tính và những tác vụ. Trong đó bao gồm nhân vi xử lý, phân cấp bộ nhớ, dự báo nhánh, v.v…

Đầu tiên là khái niệm cơ bản về nhiệm vụ của một con chip CPU. Dễ hiểu nhất là chip CPU vận hành theo một nhóm các chỉ thị, để thực hiện tính toán và xử lý tác vụ dựa trên dữ liệu đầu vào. Lấy ví dụ, nó có thể đọc giá trị từ bộ nhớ, cộng nó với một giá trị khác, và cuối cùng là lưu trữ giá trị đã cộng ngược lại bộ nhớ ở một vị trí khác. Nhưng cũng có thể tác vụ sẽ phức tạp hơn, chẳng hạn như chia hai số nếu như kết quả phép tính cộng trước đó cho ra kết quả lớn hơn 0…

Khi anh em muốn chạy một chương trình, dù là hệ điều hành hay là một trò chơi điện tử, bản chất từng chương trình máy tính đó là một nhóm những chỉ thị để chip CPU xử lý. Những chỉ thị này được tải từ bộ nhớ, và trên một chip xử lý đơn giản, những chỉ thị này sẽ được xử lý lần lượt cho tới khi chương trình kết thúc.

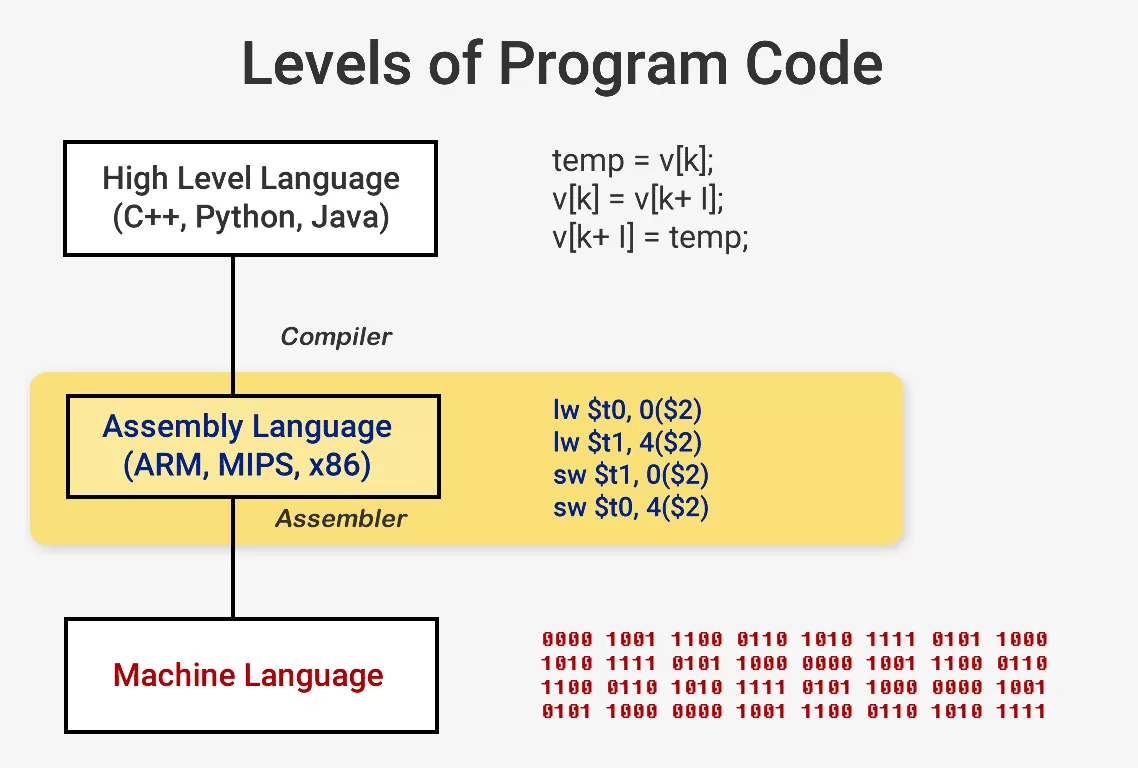

Đó là lúc cần hiểu ngôn ngữ lập trình. Các nhà phát triển phần mềm thường viết các chương trình máy tính nhờ vào những ngôn ngữ lập trình cấp cao, C++ hay Python chẳng hạn. Vấn đề là CPU đọc không hiểu những dòng code lập trình ấy. Kiến trúc con chip silicon khiến nó chỉ hiểu đúng hai giá trị, 1 và 0, chí ít là đối với máy tính điện toán truyền thống chứ chưa bàn tới máy tính lượng tử. Vậy là chúng ta cần phải dịch những dòng code lập trình sang ngôn ngữ nhị phân.

Cơ bản về chỉ thị CPU

Những chương trình máy tính được biên dịch thành một nhóm những chỉ thị cấp thấp gọi là ngôn ngữ assembly, một phần của kiến trúc tập lệnh (ISA - Instruction Set Architecture).

Kiến trúc tập lệnh là một nhóm những chỉ thị mà chip CPU được xây dựng để hiểu và thực hiện những chỉ thị được giao. Và trong số những kiến trúc tập lệnh nổi tiếng nhất, có thể kể tới x86, ARM, MIPS, RISC-V hay PowerPC… Giống hệt như thực tế là cú pháp khi viết một hàm trong ngôn ngữ C++ khác với cú pháp để viết một hàm có nhiệm vụ y hệt trong Python, mỗi kiến trúc tập lệnh lại có cú pháp khác nhau.

Quảng cáo

Những kiến trúc tập lệnh có thể được chia thành hai dạng: Độ dài cố định và độ dài động.

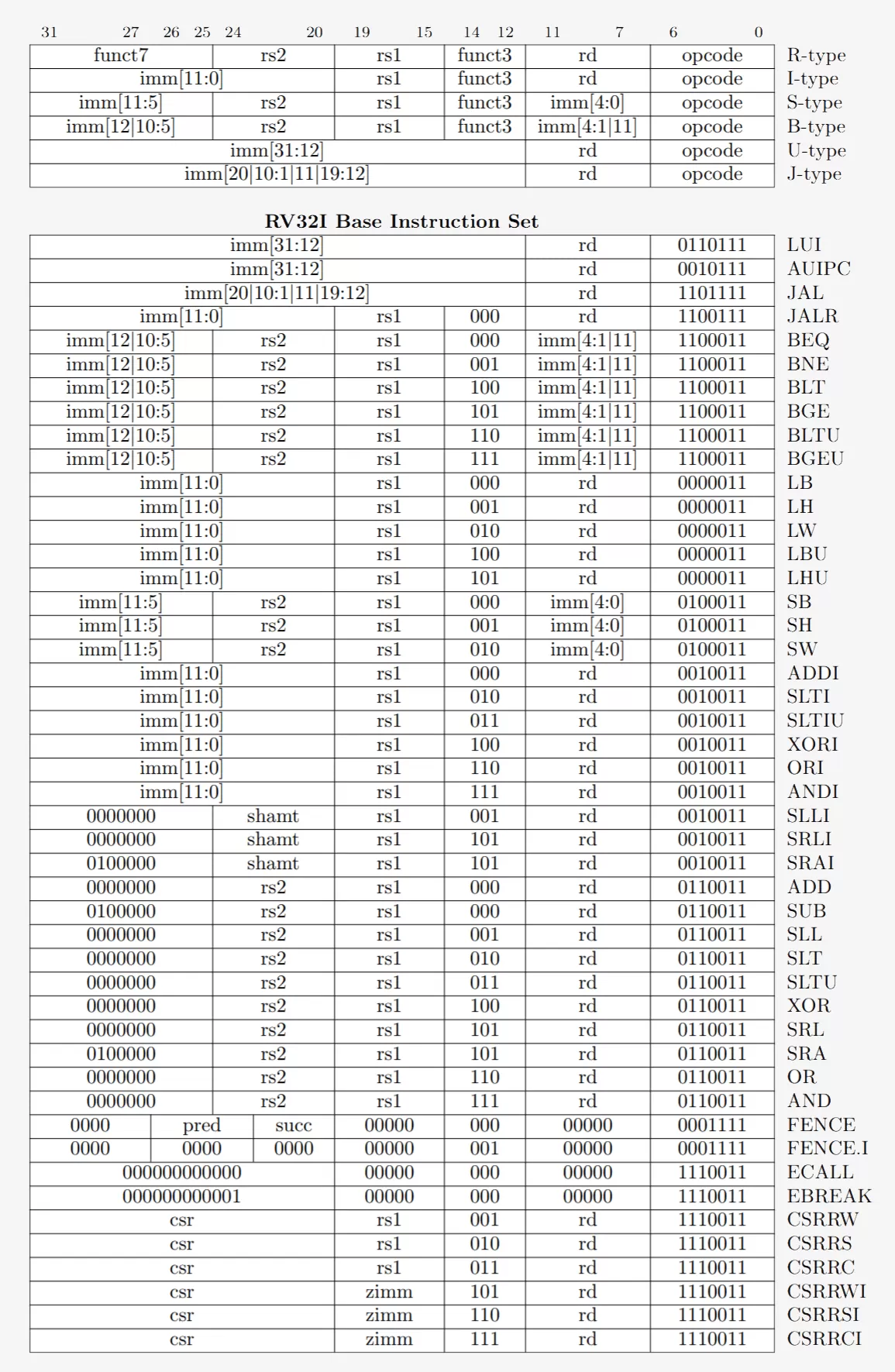

RISC-V sử dụng chỉ thị độ dài cố định, có nghĩa là mỗi chỉ thị sẽ có dung lượng bit cố định, tùy thuộc vào dạng chỉ thị đó là gì. Cái này khác biệt so với x86, một kiến trúc tập lệnh độ dài động. Đối với x86, chỉ thị được mã hóa theo nhiều cách khác nhau, mỗi phần sẽ lại có số bit khác nhau. Vì sự phức tạp này, trên những con chip xử lý kiến trúc x86, phần giải mã chỉ thị thường là phần phức tạp nhất của toàn bộ thiết kế chip xử lý.

Ví dụ hình dưới, là một vài chỉ thị của kiến trúc tập lệnh RISC-V. Phần bên phải gọi là opcode, độ dài 7 bits, xác định loại chỉ thị để CPU xử lý. Mỗi chỉ thị có những giá trị để xác định sử dụng thanh gi nào, thực hiện nhiệm vụ nào. Đây chính là quá trình bẻ gãy những chỉ thị assembly trở thành những dòng nhị phân để CPU hiểu và làm theo:

Thông thường, chỉ thị độ dài cố định giải mã dễ hơn vì kết cấu thông thường, nhưng sẽ giới hạn tổng số chỉ thị mà kiến trúc tập lệnh hỗ trợ. Những phiên bản kiến trúc tập lệnh RISC-V phổ biến có cỡ 100 chỉ thị, mã nguồn mở. Còn trong khi đó, x86 là tài sản sở hữu trí tuệ có bản quyền, và thực sự ngoại trừ Intel và AMD, chẳng ai biết chính xác có bao nhiêu chỉ thị dựa trên kiến trúc tập lệnh x86. Hầu hết đều tin rằng con số này ở mức vài nghìn chỉ thị.

Dù kiến trúc tập lệnh khác nhau, nhưng những chức năng cơ bản để CPU vận hành xử lý các phép tính nhìn chung là giống hệt nhau.

Quảng cáo

Rồi, giải thích xong về chỉ thị và kiến trúc tập lệnh, chúng ta có thể tính tới chuyện mở máy tính lên, chạy vài chương trình để xem chip CPU vận hành như thế nào. Việc thực hiện tác vụ, chạy chỉ thị có vài phần cơ bản, được chia nhỏ trong những bước vận hành của chip vi xử lý.

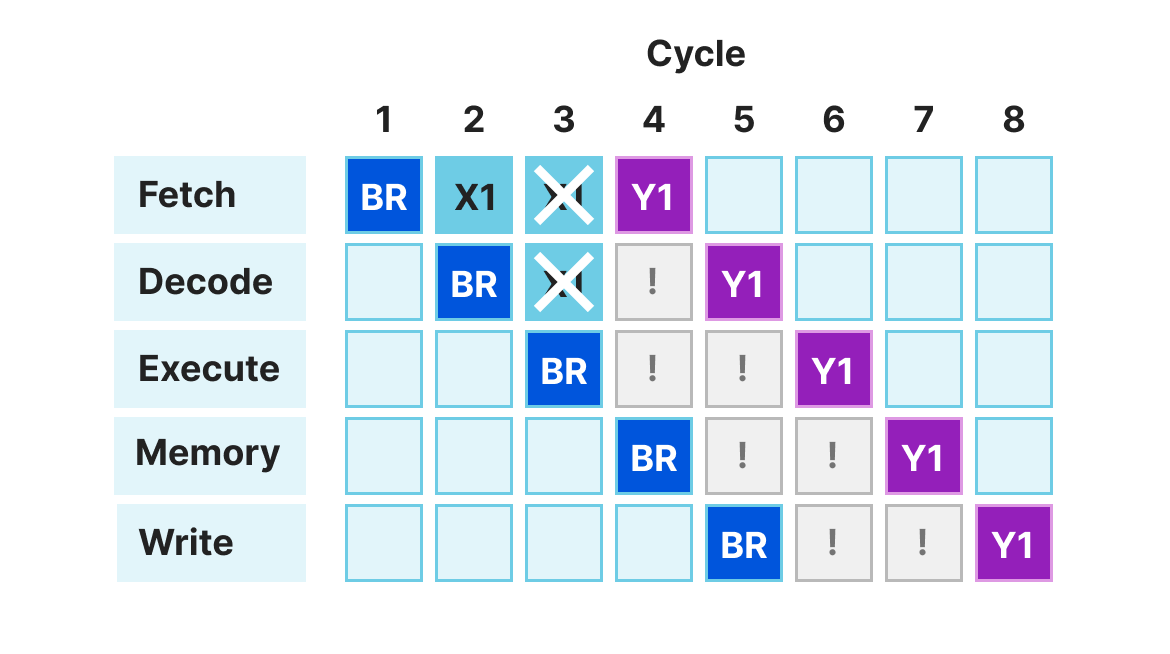

Fetch, Decode, Execute

Bước đầu tiên, là thực hiện lệnh nạp chỉ thị từ bộ nhớ vào CPU để bắt đầu quá trình tính toán. Bước thứ 2, chỉ thị được giải mã để CPU hiểu dưới dạng những chuỗi nhị phân, để nó hiểu chỉ thị đó làm nhiệm vụ gì. Có vài dạng chỉ thị khác nhau, tính toán, phân nhánh hay ghi nhớ…

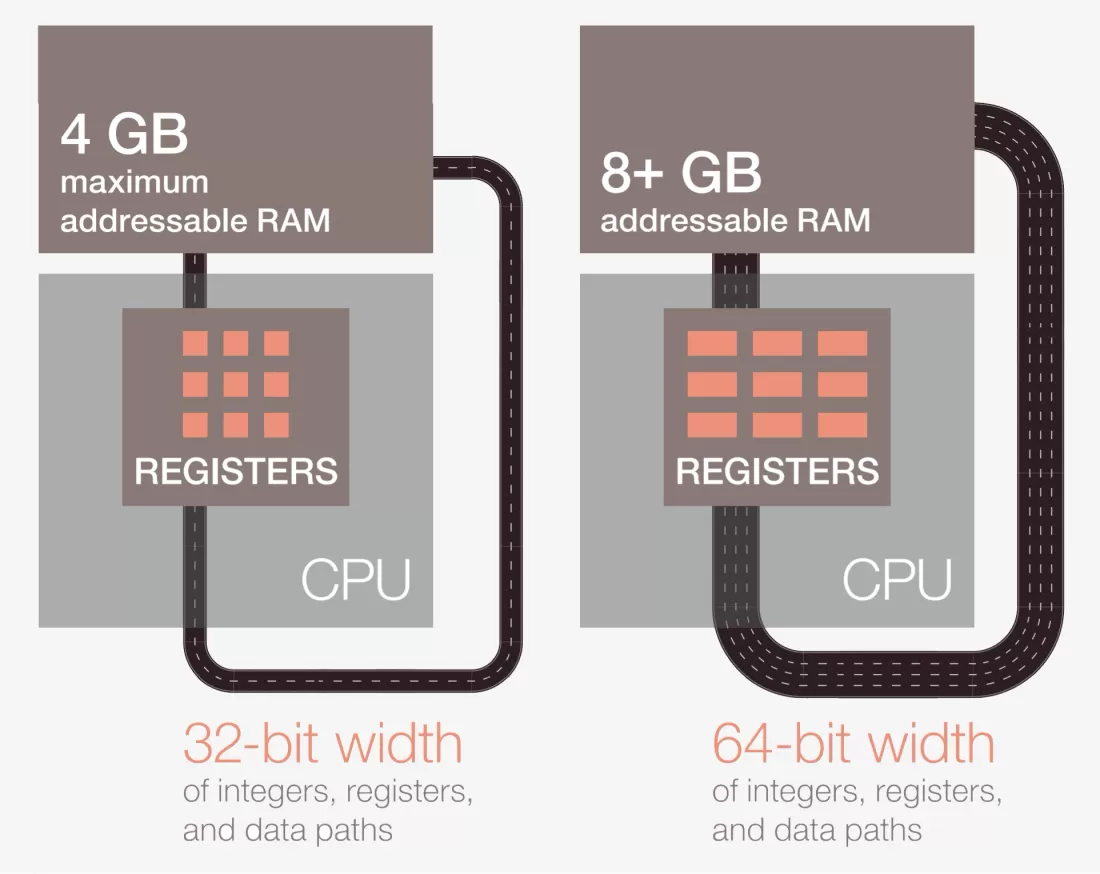

Một khi CPU hiểu dạng chỉ thị nó đang xử lý, quy trình vận hành chỉ thị sẽ được gom từ bộ nhớ hoặc thanh ghi trên chip CPU. Nếu anh em muốn cộng số A với số B, phép tính không thể thực hiện cho tới khi biết giá trị của số A và số B. Hầu hết chip CPU hiện đại đều hỗ trợ chiều rộng đường dẫn, kích thước số nguyên và độ rộng địa chỉ bộ nhớ 64-bit, tức là kích thước mỗi giá trị dữ liệu là 64 bits. Đó chính là lý do vì sao Windows XP 32-bit chỉ hỗ trợ vận hành tối đa 4GB RAM, nhưng khi cài bản 64-bit, anh em sẽ dùng được 8GB RAM trở lên.

Sau khi CPU có quy trình vận hành chỉ thị, nó sẽ đi tới bước thứ 3, là xử lý chỉ thị. Hoặc những tác vụ đó có thể là cộng các số, điều chỉnh giá trị logic của số, hoặc chỉ đơn giản là cho giá trị đó đi qua mà không biến đổi nó. Sau khi có kết quả, có thể CPU sẽ cần truy xuất bộ nhớ để lưu giá trị kết quả, hoặc CPU sẽ lưu chúng ngay trong thanh ghi trên chip. Sau khi giá trị được lưu, CPU sẽ cập nhật hiện trạng điều kiện và tiếp tục xử lý chỉ thị kế tiếp.

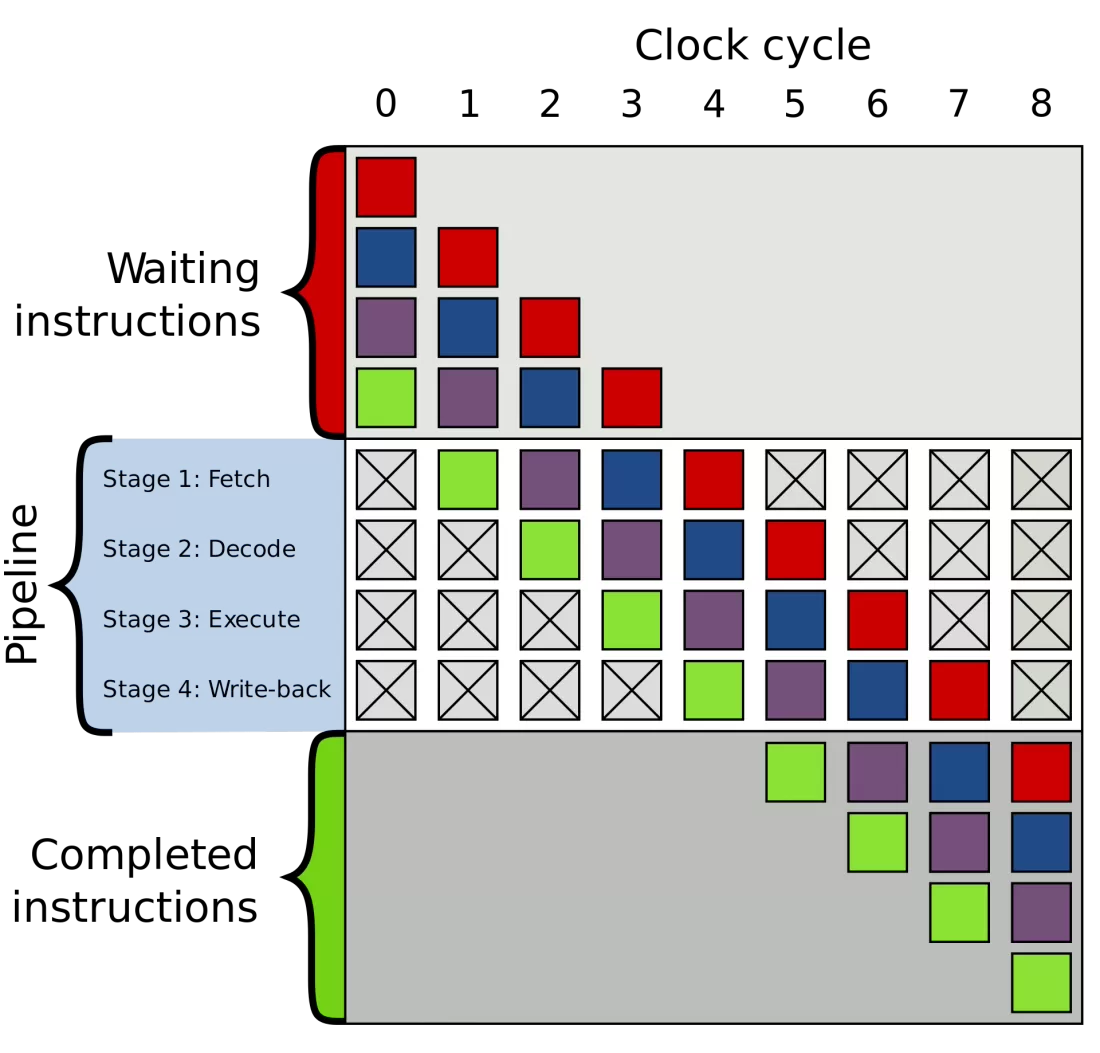

Giải thích kiểu đó là đơn giản nhất. Hầu hết những chip vi xử lý hiện đại đều sẽ chia 3 bước kể trên thành cỡ 20 bước nhỏ hơn để cải thiện hiệu năng xử lý. Điều này có nghĩa là, cứ mỗi chu kỳ xung nhịp, CPU sẽ thực hiện nhiều chỉ thị cùng lúc, nhưng phải đủ 20 hoặc nhiều hơn chu kỳ xung nhịp, mỗi chỉ thị mới hoàn tất. Mô hình xử lý này được gọi là pipeline, tượng hình cái đường ống. Anh em khi bơm nước sẽ mất một khoảng thời gian để đường ống dẫn nước từ đầu vào tới đầu ra, nhưng một khi đã đến đầu ra, dòng chảy sẽ ổn định.

Out-of-Order Execution và kiến trúc superscalar

Toàn bộ quá trình chỉ thị đi qua CPU để xử lý là một quy trình được tính toán sắp đặt cẩn trọng, nhưng không phải chỉ thị nào cũng được xử lý xong trong cùng một khoảng thời gian. Lấy ví dụ, tính cộng thì rất nhanh, nhưng phép chia hoặc truy xuất dữ liệu từ bộ nhớ sẽ cần hàng trăm chu kỳ xung nhịp. Thay vì bắt CPU dừng vận hành toàn bộ để đợi một chỉ thị làm cho xong, hầu hết CPU hiện đại đều xử lý không lần lượt, out-of-order.

Xử lý không lần lượt có nghĩa, CPU sẽ xác định chỉ thị nào có ích nhất trong việc xử lý tác vụ ở một thời điểm nhất định, còn những chỉ thị chưa xử lý xong, chưa sẵn sàng giá trị thì để vào danh sách chờ. Nếu chỉ thị hiện tại chưa sẵn sàng giá trị, CPU có thể sẽ nhảy cóc những dòng code để xem có chỉ thị nào đã xử lý xong.

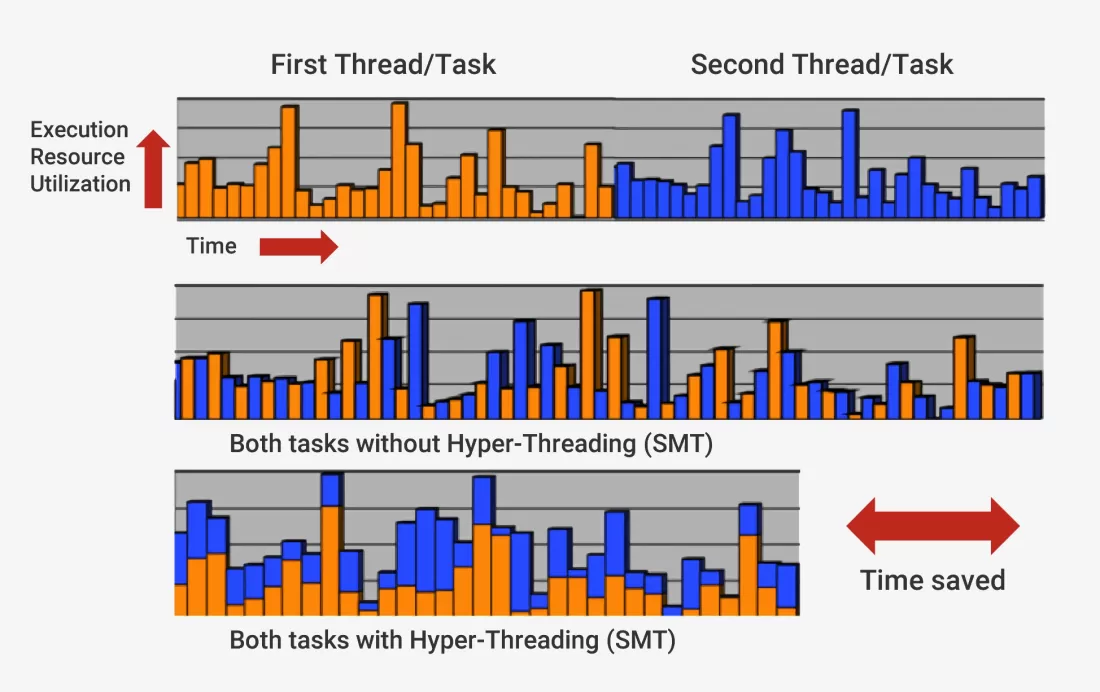

Kết hợp với out-of-order execution, là một kỹ thuật khác được các nhà thiết kế chip vi xử lý áp dụng: Kiến trúc superscalar. Với kiến trúc này, ở một thời điểm nhất định, CPU sẽ xử lý cùng lúc nhiều chỉ thị ở những bước trong pipeline xử lý. Để làm được điều này, CPU sẽ phải có vài bản sao của mỗi bước trong pipeline xử lý.

Nếu CPU nhìn thấy hai chỉ thị sẵn sàng được xử lý, và hai chỉ thị này không phụ thuộc vào giá trị của nhau, thay vì xếp hàng lần lượt, hai chỉ thị đó sẽ được xử lý song song cùng lúc. Một giải pháp quen thuộc của kiến trúc hyperscalar chính là SMT, viết tắt của Simultaneous Multithreading, hay còn gọi là siêu phân luồn. chip của Intel và AMD thường hỗ trợ SMT hai chiều, tức là 1 nhân 2 luồng xử lý, còn IBM đã tạo ra một con chip 1 nhân nhưng có tới 8 luồng xử lý.

Và để thực hiện xử lý song song hay siêu phân luồng, một chip CPU sẽ cần tới vài chi tiết khác bên cạnh nhân xử lý cơ bản.

Sẽ có hàng trăm module độc lập trong một chip CPU, mỗi module đảm trách một nhiệm vụ cụ thể. Nhưng chúng ta hãy giữ mọi thứ đơn giản. Hai module có ích nhất và có kích thước lớn nhất là bộ nhớ đệm và cụm dự báo nhánh. Những phần sẽ không được đề cập trong kiến trúc một chip CPU hiện đại bao gồm bộ đệm sắp xếp lại chỉ thị (Reorder Buffer), register alias table hay reservation station…

Bộ nhớ đệm: Tăng tốc truy xuất dữ liệu

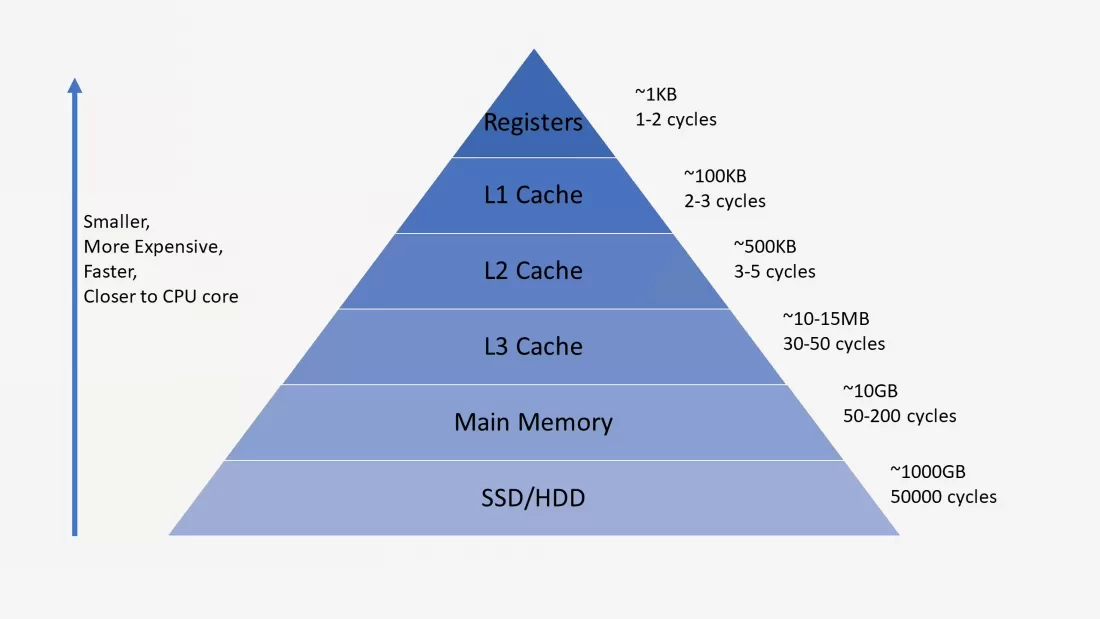

Bộ nhớ đệm có chức năng chẳng khác gì những cell ghi dữ liệu trong những bộ nhớ điện tĩnh như SSD của anh em, hay bộ nhớ truy xuất ngẫu nhiên RAM. Thứ tạo ra khác biệt của bộ nhớ đệm CPU là tốc độ truy xuất và độ trễ truy xuất dữ liệu. RAM giờ có thể đạt tốc độ hàng trăm GB mỗi giây, nhưng băng thông của CPU vẫn là quá lớn, vẫn có khả năng nghẽn cổ chai khi phải chờ đợi RAM truy xuất thông tin. Có thể mất hàng trăm chu kỳ xung nhịp để RAM đưa dữ liệu tới CPU, hoặc đối với SSD là hàng chục nghìn chu kỳ xung nhịp. Trong toàn bộ quá trình đó, CPU sẽ ngồi im không làm gì, vì không có giá trị dữ liệu để thực hiện chỉ thị và tác vụ. Không có bộ nhớ đệm, CPU sẽ dừng lại hoàn toàn, chỉ chờ HDD và SSD.

Những chip vi xử lý thường có ba cấp độ bộ nhớ đệm, xác lập thứ gọi là phân cấp bộ nhớ, như trong hình dưới đây. Bộ nhớ đệm Level 1, viết tắt là L1 thường có dung lượng nhỏ nhất và tốc độ nhanh nhất. Trung gian là cache L2, và L3 là bộ nhớ đệm dung lượng lớn nhất nhưng tốc độ chậm nhất. Trên cùng phân cấp bộ nhớ chính là những thanh ghi trên CPU, lưu trữ một giá trị đơn lẻ trong quá trình tính toán. Chính những thanh ghi này là thiết bị lưu trữ với tốc độ cao nhất trong hệ thống máy tính hay smartphone của anh em, và tốc độ của chúng thường gấp 3 lần tốc độ của bộ nhớ đệm L1.

Khi compiler biến những dòng code viết bằng ngôn ngữ lập trình cấp cao trở thành những dòng code ở mức assembly, nó cũng sẽ xác định cách phù hợp nhất để tối ưu những thanh ghi trên CPU.

Khi CPU xin dữ liệu từ bộ nhớ, đầu tiên nó sẽ kiểm tra xem dữ liệu đó có nằm trong bộ nhớ đệm L1 hay không. Nếu có, thì truy xuất rất nhanh chỉ trong vài chu kỳ xung nhịp. Còn nếu không, CPU sẽ tìm tiếp ở bộ nhớ đệm L2, và nếu không có thì tìm tiếp ở cache L3. Những lớp bộ nhớ đệm này được sắp xếp theo cách dễ tiếp cận nhất đối với các nhân xử lý logic.

Nhân xử lý sẽ đơn giản xin dữ liệu từ một địa chỉ bộ nhớ cụ thể, rồi chỗ nào lưu trữ giá trị dữ liệu ấy sẽ phản hồi. Và khi cả thanh ghi, L1, L2 và L3 không có dữ liệu nhân CPU cần, chip sẽ tìm kiếm giá trị này ở RAM.

Trên một chip CPU phổ biến anh em hay dùng, thường sẽ có hai cụm bộ nhớ đệm L1, một dành cho dữ liệu, cái còn lại dành cho chỉ thị. Thường dung lượng bộ nhớ đệm L1 chỉ chừng 100 kB. Rồi mỗi nhân CPU sẽ có một bộ nhớ đệm L2, thỉnh thoảng sẽ thấy hai nhân dùng chung một cụm L2 cache như thế này, với dung lượng thường chỉ khoảng vài trăm kB. Cuối cùng là một cụm bộ nhớ đệm L3 dành cho tất cả mọi nhân CPU dùng chung, dung lượng vài chục MB.

Khi chip CPU xử lý các tác vụ, các giá trị chỉ thị và dữ liệu được nhân xử lý logic sử dụng và truy xuất nhiều nhất sẽ được bỏ vào bộ nhớ đệm. Điều này giúp tăng đáng kể tốc độ xử lý, vì CPU không phải truy xuất liên tục bộ nhớ RAM để tìm thứ nó cần. Riêng cách hệ thống bộ nhớ đệm được thiết kế và vận hành ra sao cũng lại là một phần vô cùng quan trọng trong quá trình thiết kế và sản xuất chip CPU. Nó sẽ được đề cập kỹ hơn trong hai phần tiếp theo của loạt bài này.

Một xu hướng mới, đó là bên cạnh ba cấp độ bộ nhớ đệm trong phân cấp bộ nhớ máy tính L1, L2 và L3 vẫn là tiêu chuẩn, đã bắt đầu có những giải pháp bộ nhớ đệm xếp chồng lên nhân xử lý logic của CPU, giúp tăng đáng kể hiệu năng xử lý trong một số tình huống. 3D-Vcache của AMD là một ví dụ điển hình.

Dự báo nhánh, và thực hành suy đoán

Bên cạnh bộ nhớ đệm, khối kiến trúc bán dẫn quan trọng khác của những chip CPU hiện đại chính là branch predictor, bộ dự đoán nhánh chính xác. Các lệnh nhánh tương tự như các câu lệnh "nếu" đối với chip xử lý. Một tập lệnh sẽ thực thi nếu điều kiện là đúng và một tập lệnh khác sẽ thực thi nếu điều kiện là sai.

Ví dụ, anh em có thể muốn so sánh hai số và nếu chúng bằng nhau, hãy thực thi một hàm và nếu chúng khác nhau, hãy thực thi một hàm khác. Các lệnh nhánh này cực kỳ phổ biến và có thể chiếm khoảng 20% tổng số lệnh trong một chương trình.

Nhìn bề ngoài, các lệnh nhánh này có vẻ không phải là vấn đề, nhưng thực tế chúng có thể rất khó để bộ xử lý thực hiện đúng. Vì tại bất kỳ thời điểm nào, CPU có thể đang trong quá trình thực thi 10 hoặc 20 lệnh cùng một lúc, nên điều rất quan trọng là phải biết lệnh nào cần thực thi. Có thể mất 5 chu kỳ để xác định xem lệnh hiện tại có phải là nhánh hay không và thêm 10 chu kỳ nữa để xác định xem điều kiện có đúng hay không. Trong thời gian đó, bộ xử lý có thể đã bắt đầu thực thi hàng chục lệnh bổ sung mà thậm chí không biết liệu đó có phải là lệnh chính xác để thực thi hay không.

Để giải quyết vấn đề này, tất cả các CPU hiện đại đều sử dụng một kỹ thuật gọi là suy đoán. Điều này có nghĩa là CPU theo dõi các lệnh rẽ nhánh và dự đoán xem nhánh đó liệu có được thực hiện hay không. Nếu dự đoán đúng, bộ xử lý đã bắt đầu thực hiện các lệnh tiếp theo, dẫn đến việc tăng hiệu suất nhờ giảm thời gian chờ. Nếu dự đoán không đúng, bộ xử lý sẽ dừng thực hiện, loại bỏ tất cả các lệnh được thực hiện không đúng và khởi động lại từ điểm chính xác.

Các bộ dự đoán rẽ nhánh này chính xác là một dạng machine learning sơ khai, vì chúng thích ứng với hành vi rẽ nhánh theo thời gian. Nếu một bộ dự đoán đưa ra quá nhiều dự đoán không chính xác, nó sẽ điều chỉnh để cải thiện độ chính xác. Nhiều thập kỷ nghiên cứu về các kỹ thuật dự đoán rẽ nhánh đã dẫn đến độ chính xác vượt quá 90% trong các bộ xử lý hiện đại.

Mặc dù suy đoán cải thiện đáng kể hiệu suất bằng cách cho phép bộ xử lý thực hiện các lệnh đã sẵn sàng thay vì chờ các lệnh bị đình trệ, nhưng nó cũng có nguy cơ gây ra các lỗ hổng bảo mật. Lỗ hổng khét tiếng, được đặt tên là Spectre khai thác các lỗi thực hiện suy đoán trong dự đoán rẽ nhánh. Kẻ tấn công có thể sử dụng mã được tạo đặc biệt để đánh lừa bộ xử lý thực hiện suy đoán các lệnh làm rò rỉ dữ liệu bộ nhớ nhạy cảm. Kết quả là, một số khía cạnh của suy đoán đã phải được thiết kế lại để ngăn chặn rò rỉ dữ liệu, dẫn đến việc CPU bị giảm hiệu năng và tốc độ xử lý.

Kiến trúc của bộ xử lý hiện đại đã có rất nhiều những tiến bộ đáng kể trong vài thập kỷ qua. Những cải tiến và thiết kế thông minh đã mang lại hiệu suất cao hơn và sử dụng phần cứng cơ bản tốt hơn. Tuy nhiên, các nhà sản xuất CPU rất kín tiếng về các công nghệ cụ thể bên trong bộ xử lý của họ, vì vậy không thể biết chính xác những gì diễn ra bên trong.

Mặc dù vậy, các nguyên tắc cơ bản về cách bộ xử lý hoạt động vẫn nhất quán trên tất cả các thiết kế. Intel có thể thêm công thức bí mật của họ để tăng tỷ lệ truy cập bộ nhớ đệm hoặc AMD có thể thêm một bộ dự đoán nhánh nâng cao, nhưng cả hai đều thực hiện cùng một nhiệm vụ.

Theo Techspot