2024 hứa hẹn sẽ là một năm có nhiều cuộc cạnh tranh dữ dội trong mảng chip máy tính. Cụ thể nhất sẽ là kiến trúc Zen 5 của AMD và Meteor Lake từ Intel.

Có thể nói cuộc sống ngày nay của chúng ta đã thay đổi rất nhiều so với vài chục năm trước, nhất là khi điện toán ngày càng phổ biến hơn trong đời sống mỗi người. Với Internet of Things (IoT), mọi thứ đều kết nối và trong bất kỳ thiết bị cá nhân nào cũng cần 1 con chip để xử lý. Có thể đó là 1 điện thoại thông minh, laptop hay tablet hoặc 1 hệ thống máy chủ (server) hay 1 thiết bị đeo (wearable). Những con chip xử lý nằm trong chúng là thành phần cơ bản nhất mà mỗi người dùng, hay nói đúng hơn là mỗi thiết bị đều cần có.

Nhưng câu chuyện của chúng ta hôm nay sẽ không phải là một con chip "vạn năng" có thể làm được mọi thứ trên trời dưới đất - hoặc ít nhất là chúng ta sẽ không đi quá xa những gì mà chính nhà sản xuất công bố. Nội dung này sẽ tập trung vào những hệ thống PC "truyền thống" mà 2 đối thủ chính là AMD và Intel đã "so găng" trong suốt hàng chục năm qua. Tất nhiên thị trường PC ngày nay đã có nhiều thay đổi, chúng ta có Apple Silicon và Qualcomm cùng đang "mấp mé ngoài sân khấu", nhưng 2 nhân vật chính của buổi diễn này vẫn đang là 2 đại gia x86. Vậy Intel đang nắm quân bài gì trong tay và Meteor Lake (MTL) có điểm gì đặc biệt trước "phong ba bão tố" thị trường PC?

Một điều có thể thấy rõ là MTL sẽ được ra mắt trong một hoàn cảnh hết sức đặc biệt với Intel. Sau quá nhiều năm "ngủ quên", hình ảnh và vị thế của Intel đang trở nên yếu hơn bao giờ hết. Kiến trúc Zen của AMD đang mặc sức làm mưa làm gió trên thị trường, còn các con chip Mx của Apple liên tục "dồn" Intel vô chân tường dù cho khác kiến trúc. Riêng Qualcomm tuy chưa có sản phẩm chính thức nhưng mối đe doạ không hề nhỏ, trước mắt có thể là Snapdragon X Elite.

4 trọng điểm của Meteor Lake

Mặc dù một loạt Rocket Lake, Tiger Lake, Alder Lake, Raptor Lake (Intel có vẻ "nghiện" Lake) cùng được tung ra trong mấy năm qua song chúng hầu hết chỉ mang tính "chống đỡ" chứ không thực sự có nhiều cải thiện về kiến trúc. Intel chủ yếu tập trung vào việc đẩy xung nhịp lên mức tối đa và kéo dài thời gian turbo lâu nhất có thể. Cách làm này tuy vẫn giúp làm tăng hiệu năng nhưng điểm trừ là nó tốn quá nhiều điện và toả ra quá nhiều nhiệt, nên không thể xem là một cải thiện thực sự về kiến trúc.

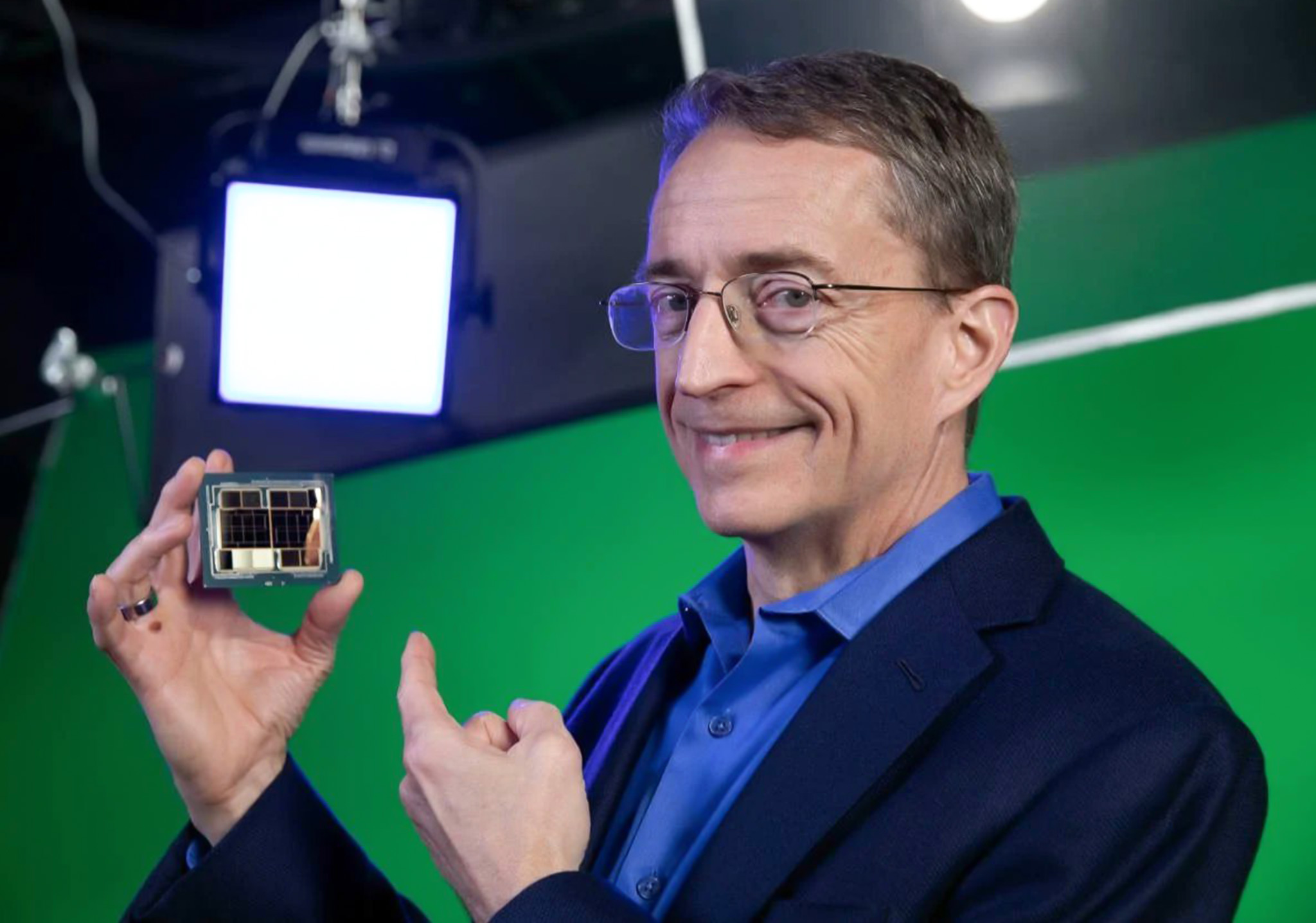

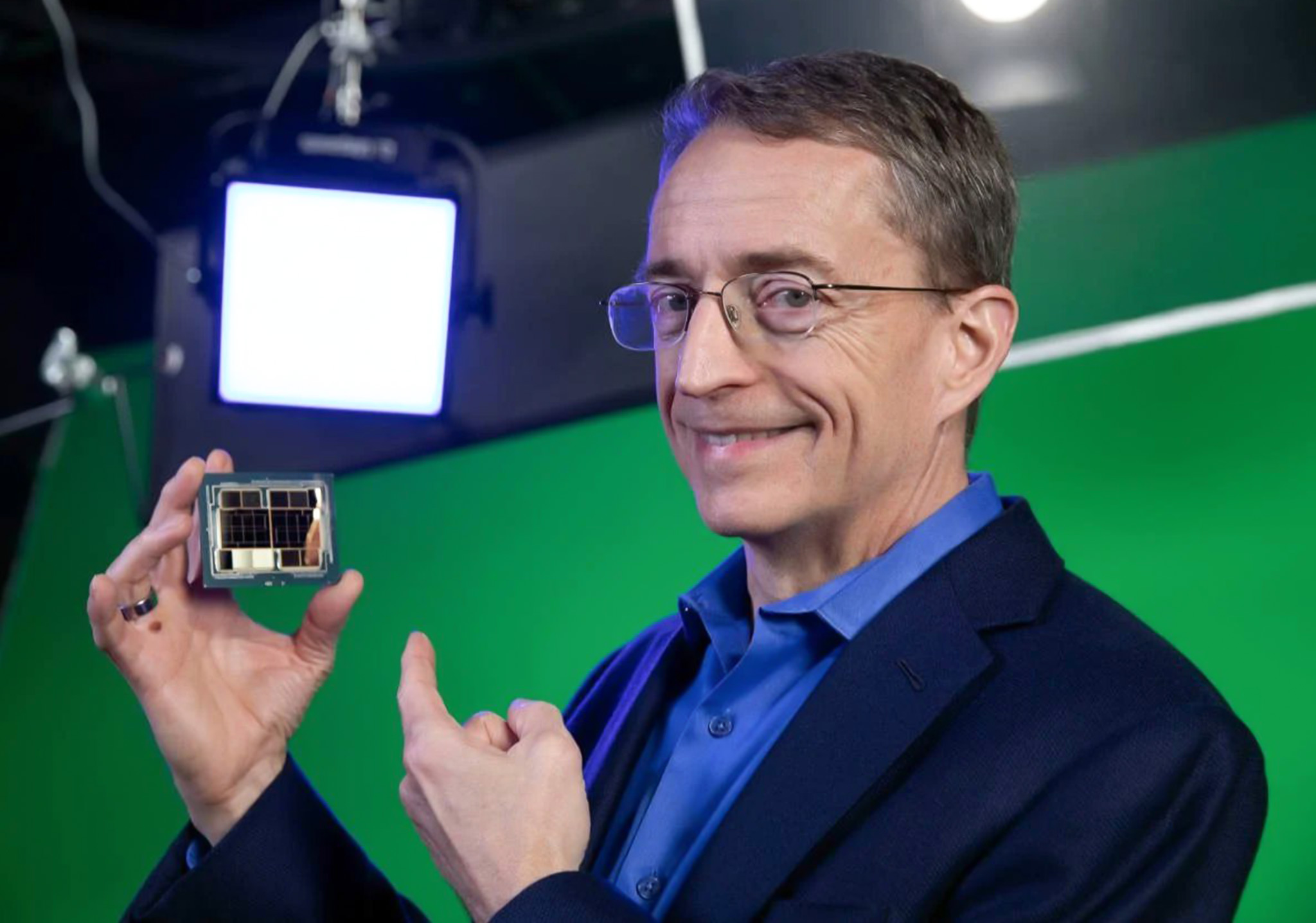

Một điểm ngoài lề khác tuy không phải điểm nhấn của ngày hôm nay nhưng có ý nghĩa khá quan trọng với MTL - CEO hiện tại của Intel là Patrick Paul Gelsinger, vốn là một nhân vật "đúng chất" kỹ sư và vi xử lý (tương tự Lisa Su bên AMD). Trước đó Intel được lãnh đạo bởi Brian Krzanich, người không có mấy kinh nghiệm về vi xử lý và có những quyết định đầu tư "ngoài luồng". Các sản phẩm CPU của Intel trong giai đoạn Krzanich thực sự không có nhiều ấn tượng trong khi sản phẩm của Lisa Su ngày càng sắc nét hơn. Còn MTL được Gelsinger chính tay "cầm trịch", nên thành bại của MTL có thể nói sẽ quyết định cả vị thế của Gelsinger ở Intel sau này...

Patrick Paul Gelsinger, CEO Intel đương nhiệm.

Nhưng "có thực mới vực được đạo", phải có nguyên liệu tốt thì Gelsinger mới có thể làm ra một sản phẩm tốt, và đây là những thứ mà MTL được "vũ trang" cho một thị trường PC đầy sóng gió:

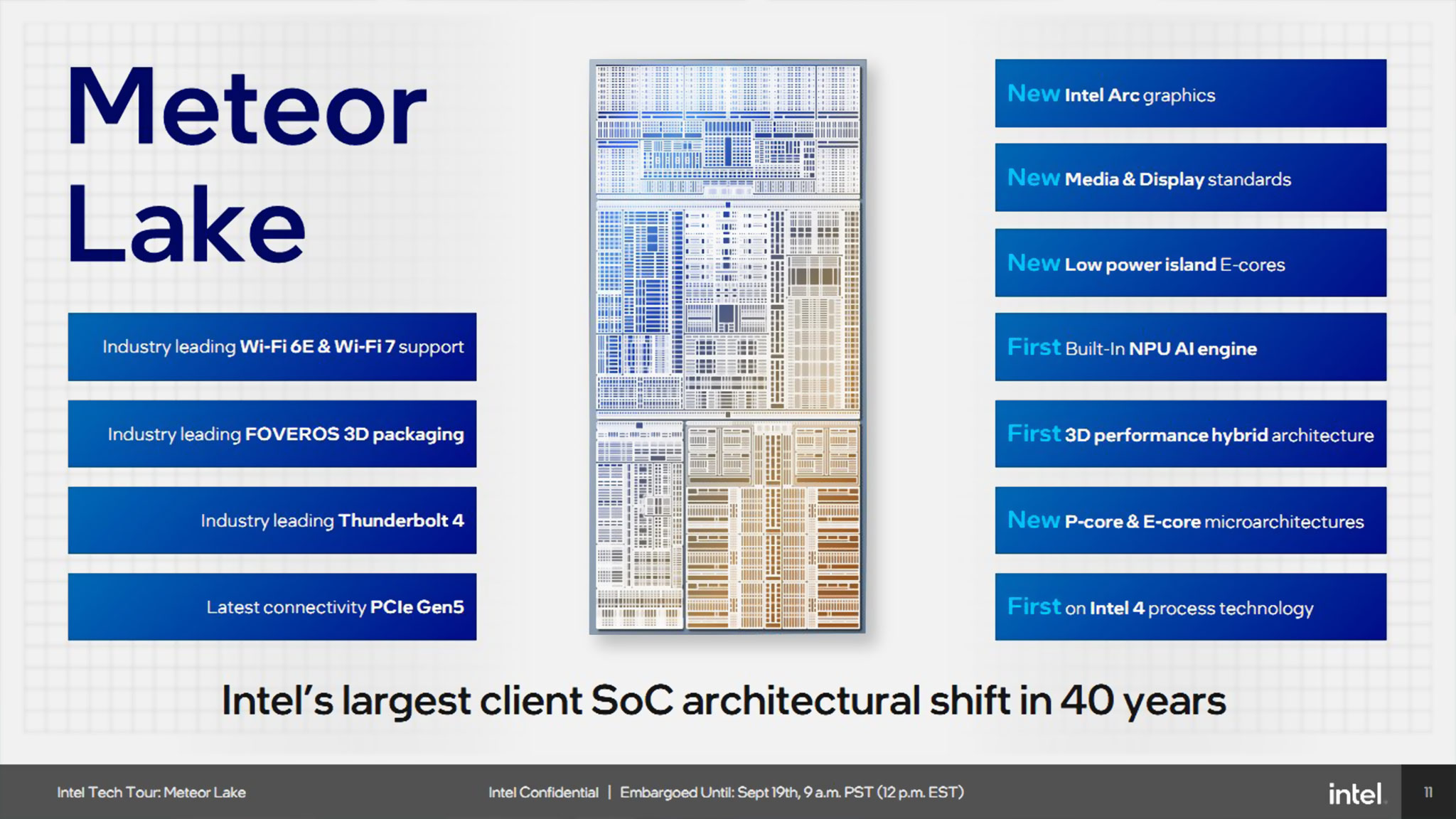

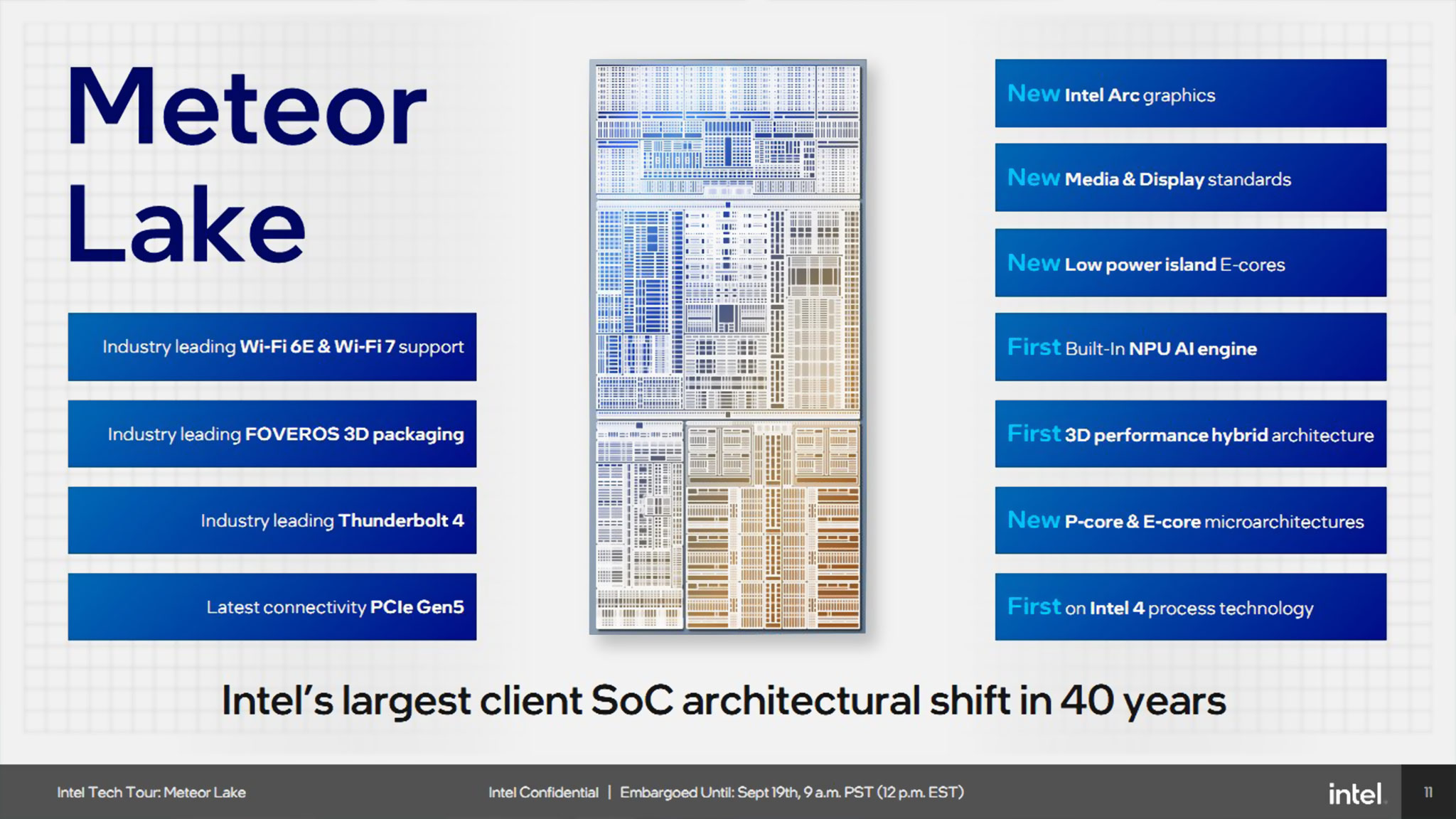

Các tính năng chính của Meteor Lake.

Mặc dù kiến trúc (arch) là thứ quan trọng nhất khi nói về một con chip, công nghệ bán dẫn để làm ra nó vẫn là thứ có ảnh hưởng hiển hiện và rõ ràng nhất. Trong những năm trở lại đây, Intel đã không còn dẫn đầu về tiến trình bán dẫn như đã từng. Quá trình đầu tư mạnh mẽ và quyết liệt của TSMC hay Samsung đều đẩy Intel tụt lại phía sau. Có thể nói các sản phẩm "Lake" trước đấy của Intel cũng sẽ không bị đánh giá thấp nếu chúng không "bám trụ" vào công nghệ 14++++ hay 10++ nm.

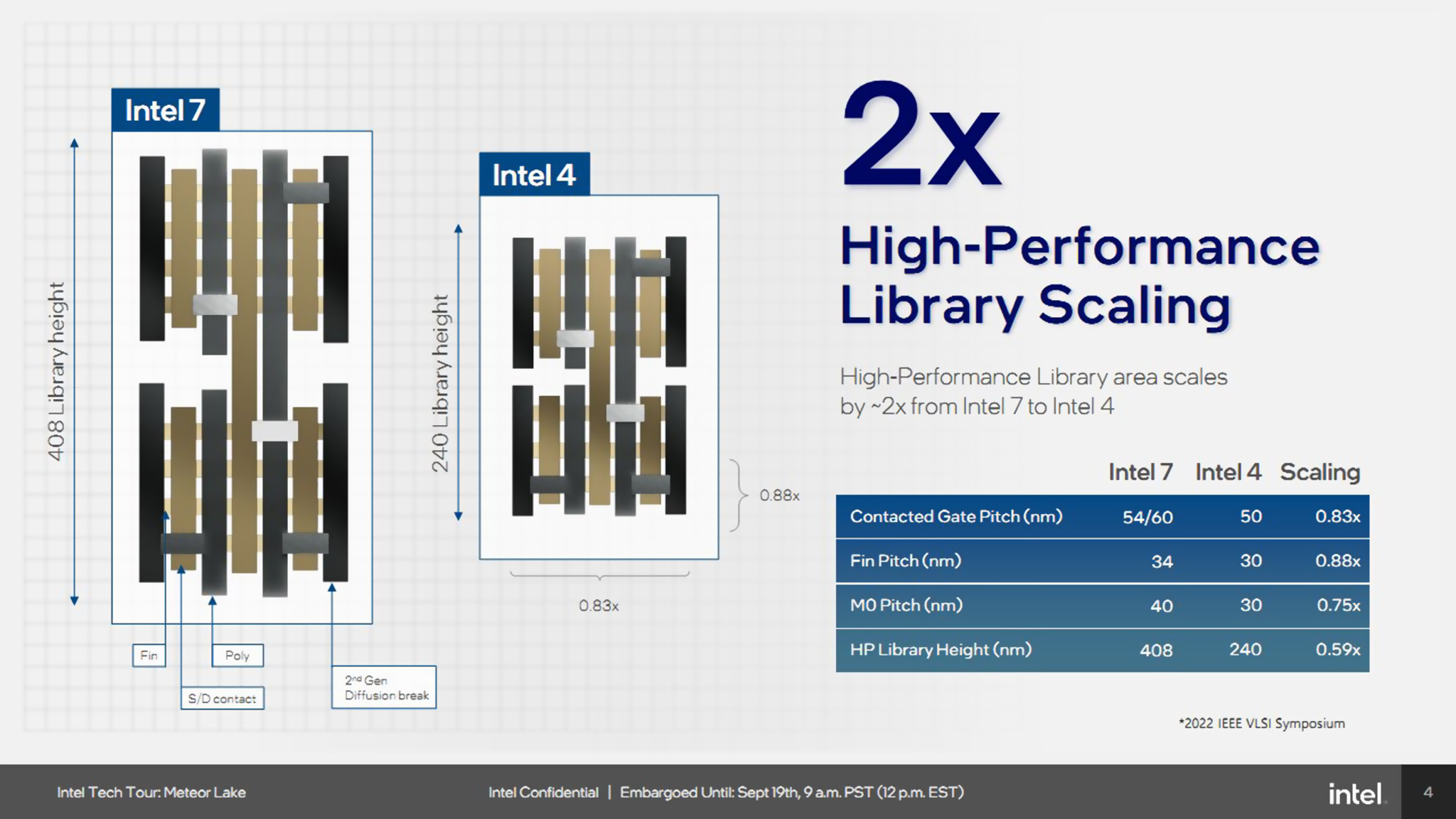

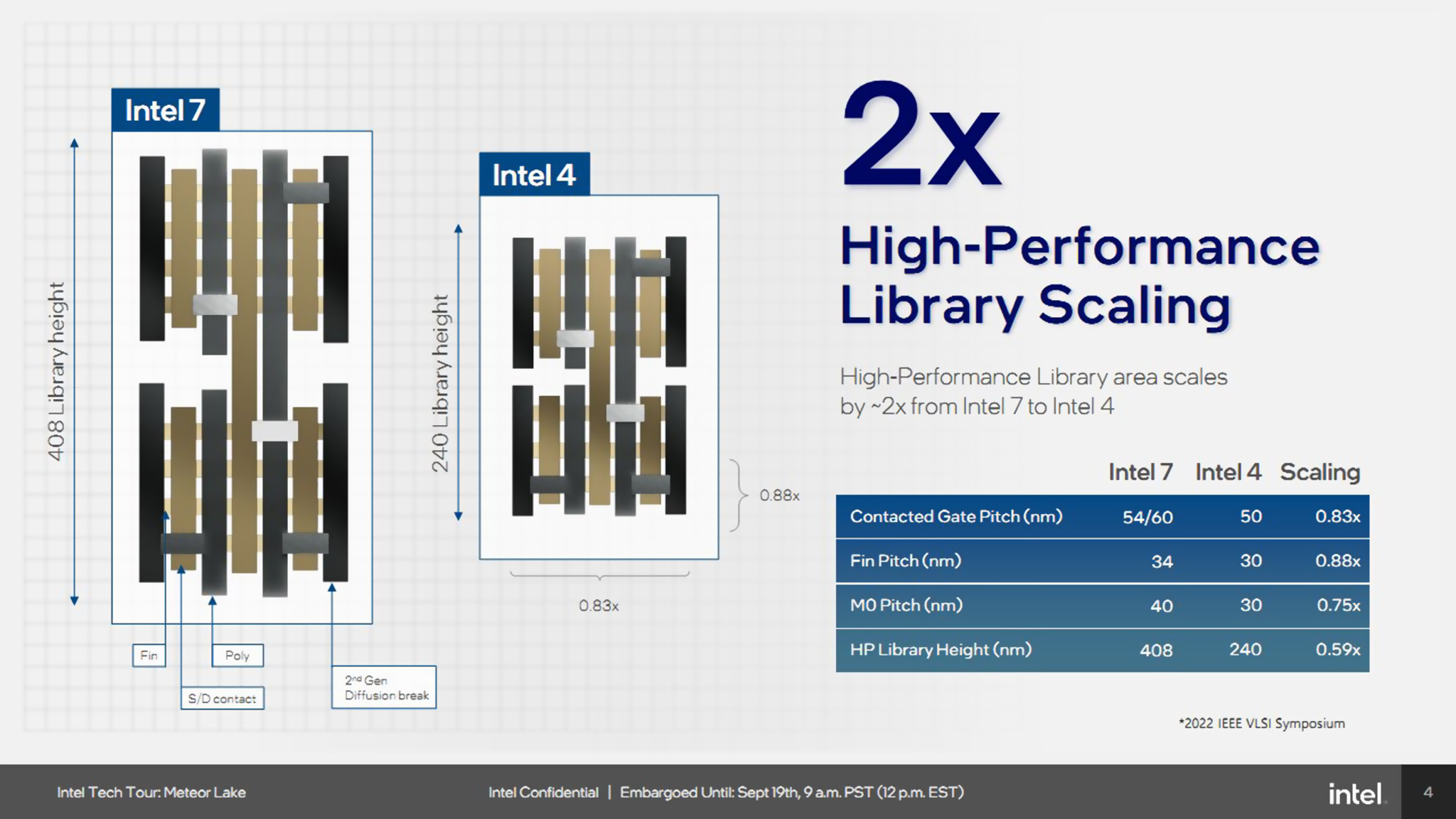

So sánh công nghệ Intel 4 vs. Intel 7

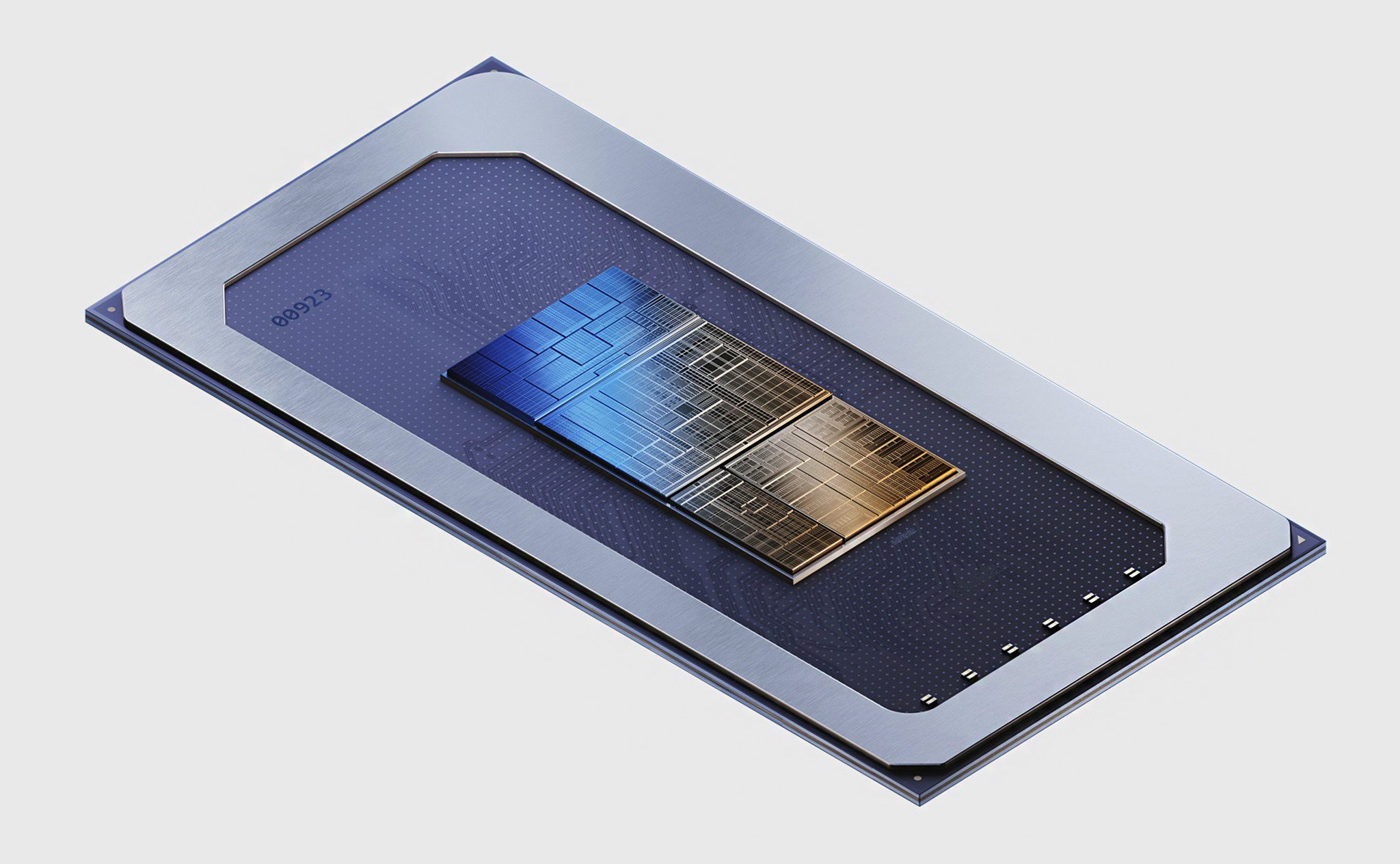

Do vậy việc sử dụng tiến trình Intel 4 (7 nm) sẽ là một thay đổi quan trọng của MTL, ít nhất so với các sản phẩm "Lake" trước đó. Một chi tiết thú vị là không phải toàn bộ con chip sẽ dùng chung công nghệ Intel 4 - die đồ hoạ sẽ được gia công trên tiến trình TSMC 5N (5 nm) còn die SoC là trên TSMC 6N (6 nm). Và đây cũng là con chip đầu tiên chuyển từ thiết kế đơn chip (monolithic) sang đa chip (chiplet/tile) của Intel, giống cách AMD đang làm với Zen.

Việc sử dụng thiết kế chiplet cũng đồng nghĩa với việc Intel buộc phải áp dụng một kỹ thuật đóng gói chip mới là Foveros. Về bản chất, Foveros là cách để các die chip "nói chuyện" với nhau, tương tự kỹ thuật interposer mà AMD hoặc các khách hàng khác của TSMC đang sử dụng dựa trên các TSV (through-silicon-via). Thực chất chúng ta không rõ liệu Foveros có thực sự tốt hơn interposer không nhưng Intel tự hào cho biết khi hoạt động ở tần số 2 GHz, mỗi bit dữ liệu truyền qua Foveros chỉ tốn có 0.15 - 0.3 pJ (10^-12 Joule) năng lượng.

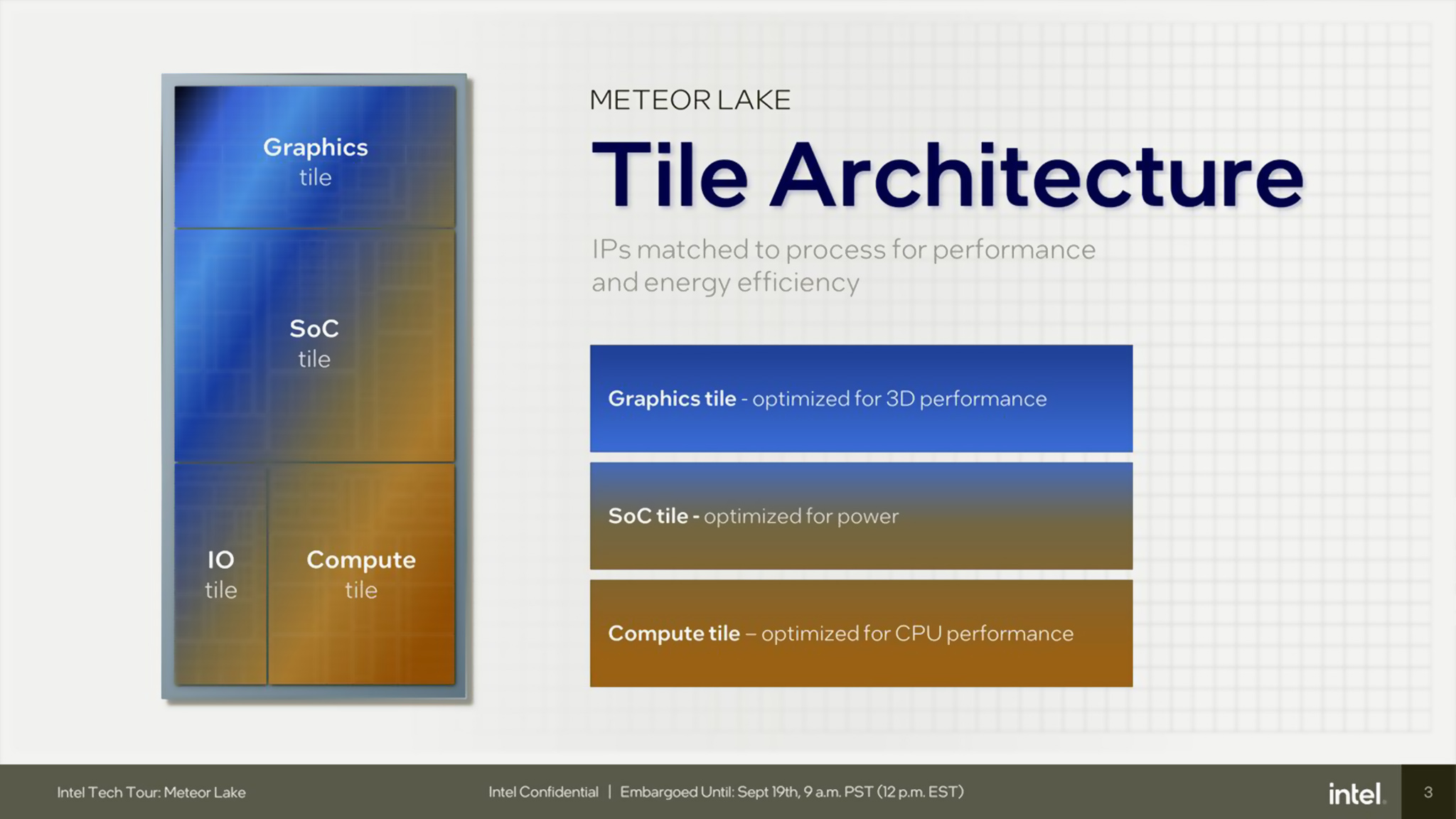

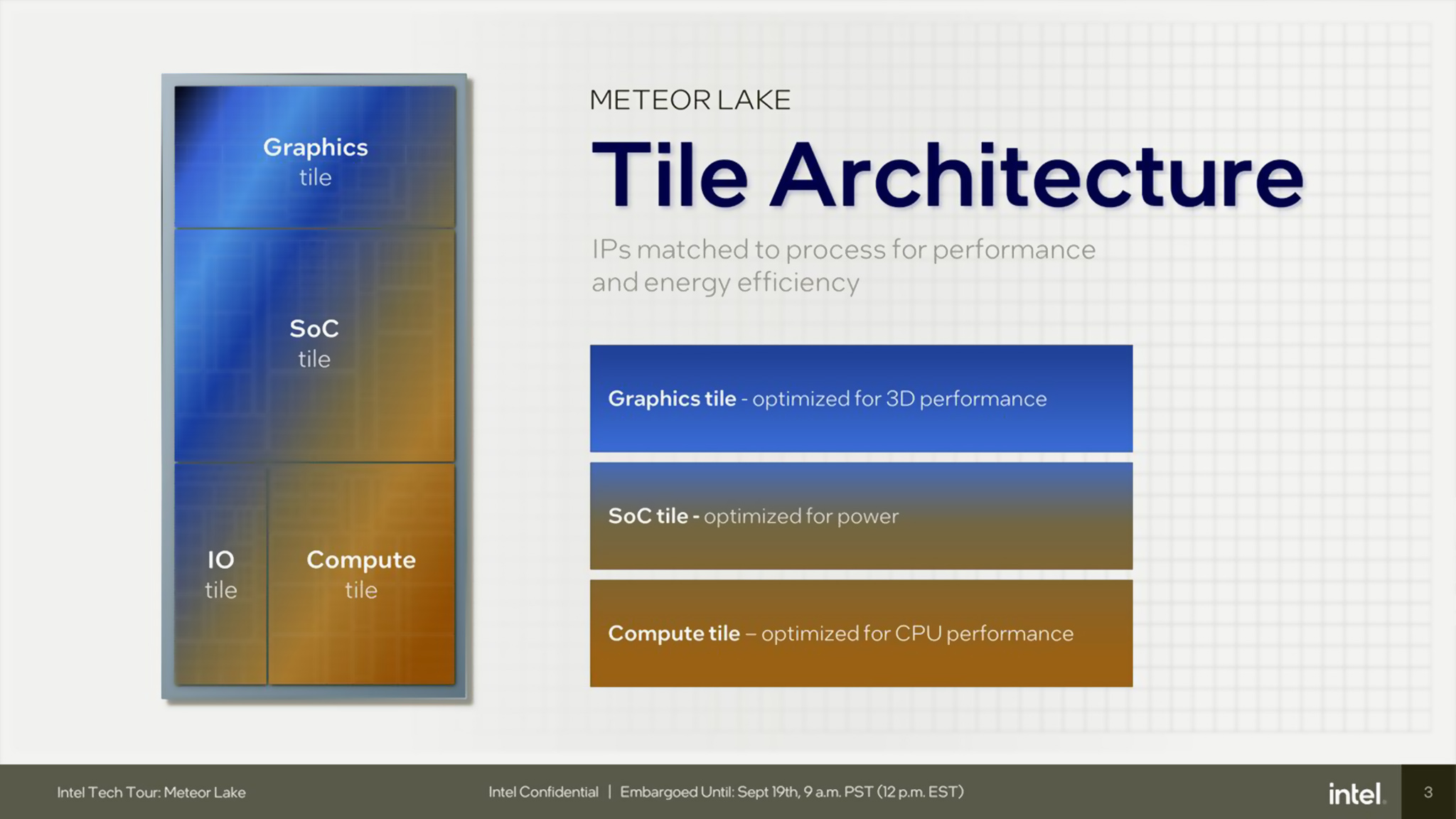

Và vì MTL là một thiết kế chiplet (tile), các thành phần chức năng sẽ không nằm trên cùng 1 die chip nữa mà được "chia hộ khẩu" ra thành 4 chuyên khu: die điện toán (compute), die đồ hoạ (graphics), die nhập xuất (IO) và die "tá lả" (SoC).

Có thể nói việc chuyển qua chiplet giống AMD tuy sẽ mang tiếng "copy" nhưng dù sao đây cũng là một bước đi đúng đắn cho Intel. Với từng die tách biệt thế này, mỗi chuyên khu của MTL có thể hoạt động độc lập không ảnh hưởng tới các chuyên khu còn lại và nhờ thế mà hiệu quả sử dụng điện sẽ cao hơn. Die điện toán có thể hoạt động ở công suất lớn còn die đồ hoạ và SoC có thể chủ động ngắt bớt điện đi. Thêm vào đó mỗi die dùng tiến trình bán dẫn riêng sẽ cho phép Intel lựa chọn tiến trình phù hợp nhất cho mỗi chuyên khu chứ không chỉ mỗi hiệu suất cao (HP) hoặc tiết kiệm điện (LP) như trước nữa.

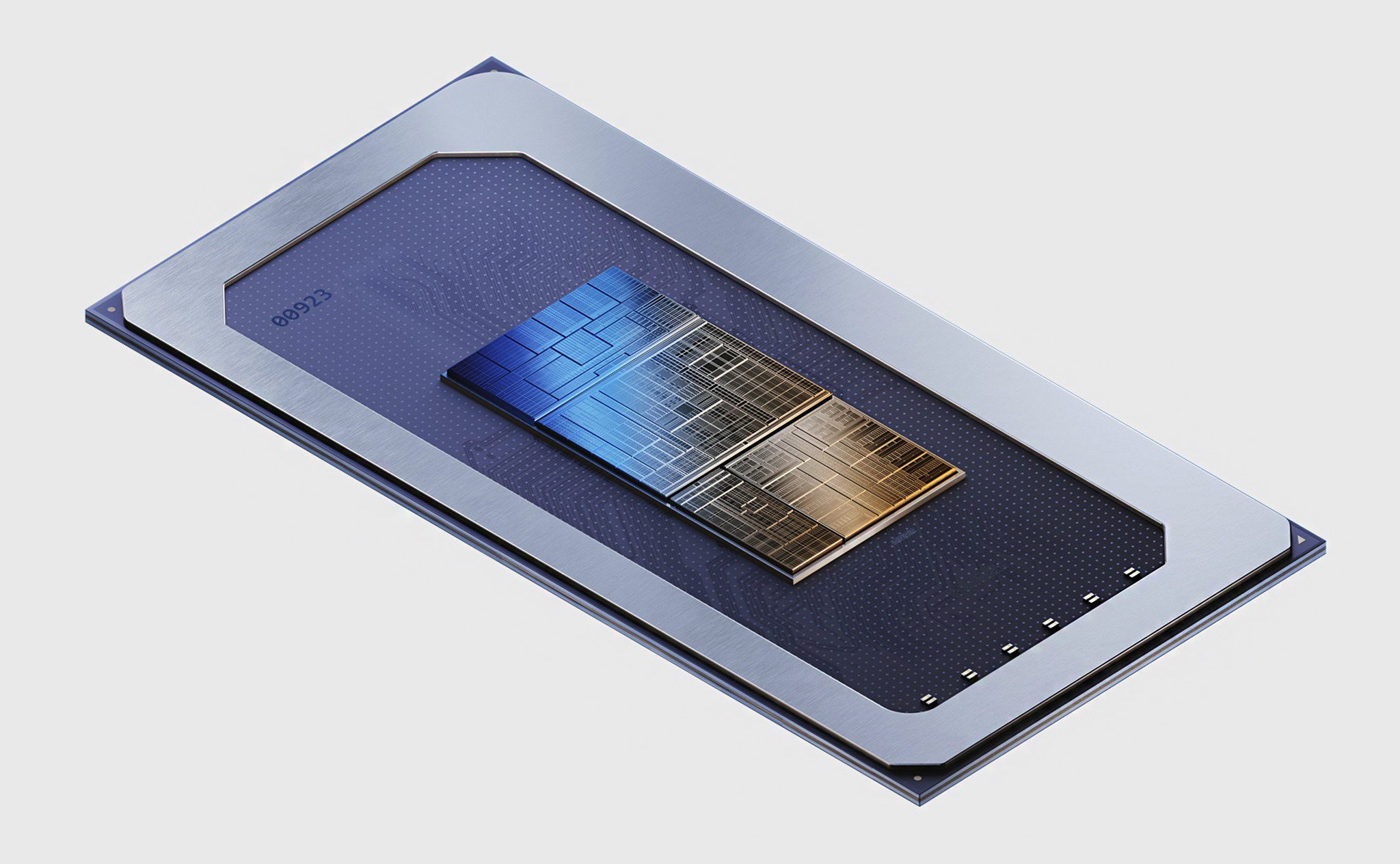

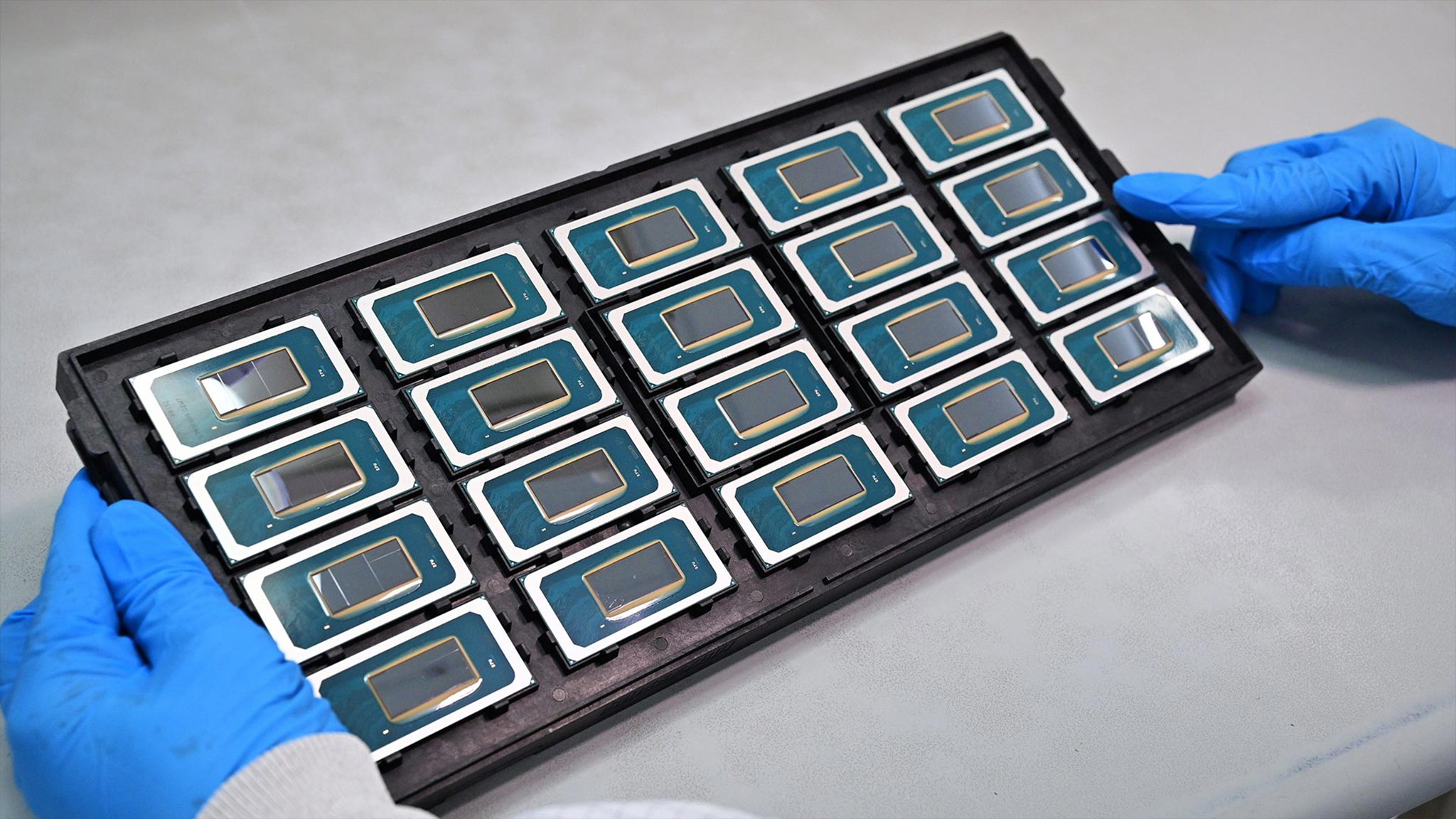

Con chip Meteor Lake được cấu tạo 4 từ die riêng lẻ liên kết với nhau bằng công nghệ Foveros.

Về mặt chuyên môn, lần này chúng ta chỉ điểm qua những ý chính trong kiến trúc MTL. Vì Intel đặt rất nhiều tâm huyết vô "canh bạc" lần này, do vậy có rất nhiều thứ để nói và khuôn khổ bài viết này không kham được hết tất cả. Chúng ta sẽ có những bài chuyên sâu hơn vào từng thành phần con chip sau này.

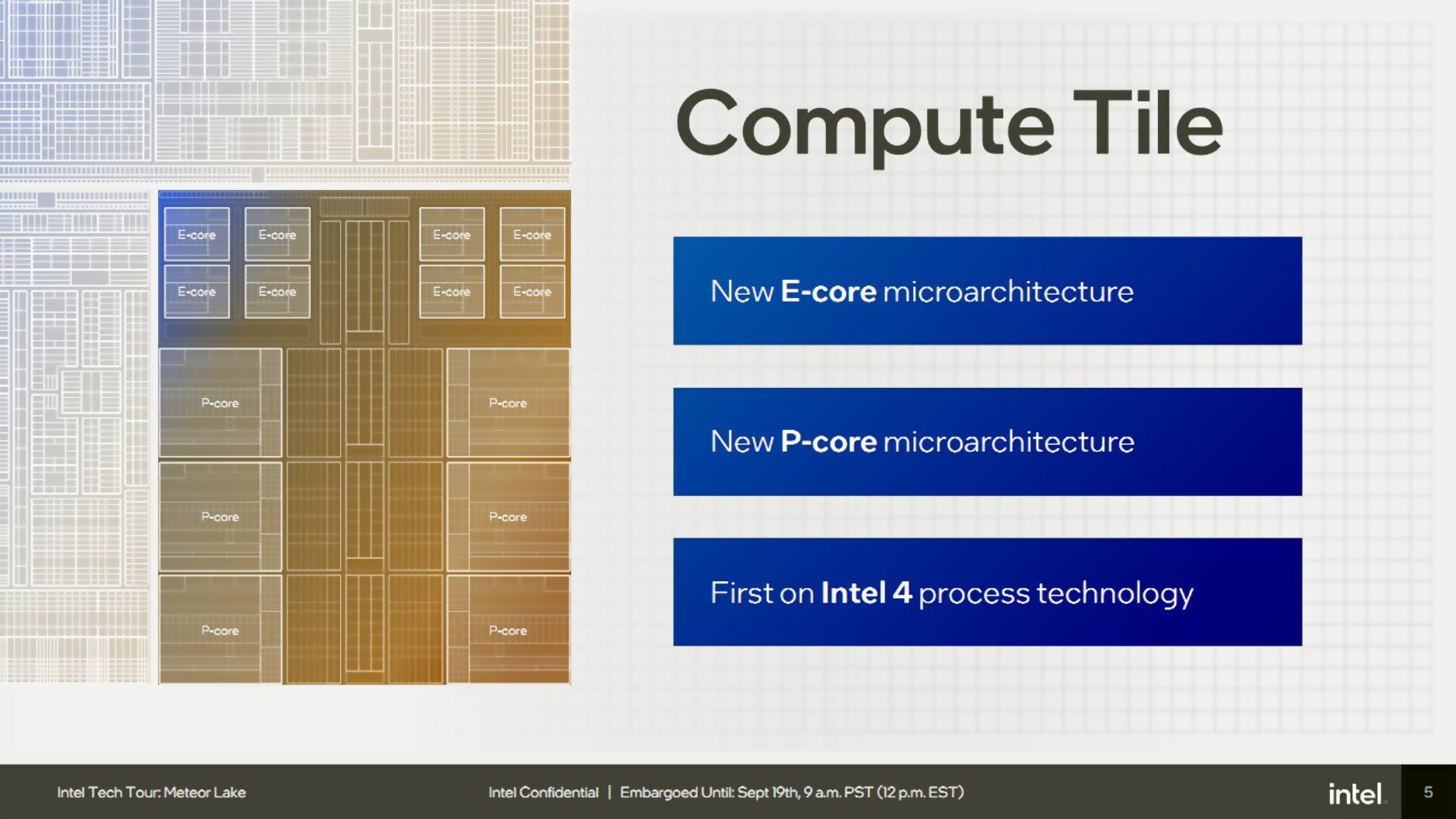

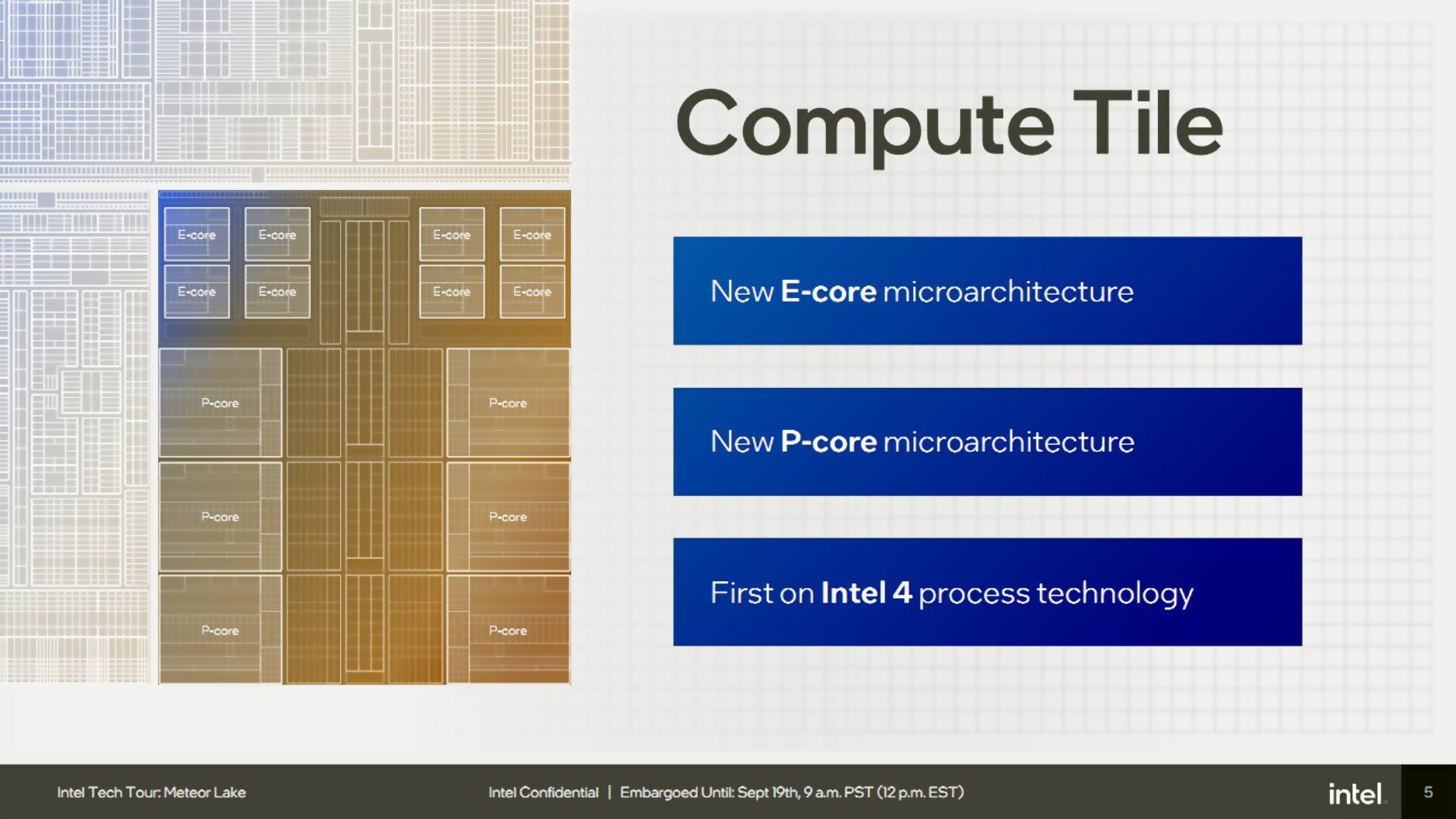

Cấu trúc die điện toán của Meteor Lake

Trước hết khi nói tới die điện toán của MTL sẽ là 2 loại nhân P-core Redwood và E-core Crestmont. Hiện tại Intel không nói rõ chúng khác thế nào với các nhân Golden Cove (P) và Gracemont (E) trừ việc sẽ tốt hơn và có mức IPC cao hơn thế hệ cũ. Một chi tiết thú vị là dù MTL sẽ có NPU (nhân AI) riêng nằm trong die SoC, nhưng các nhân Crestmont (E) vẫn còn chứa các tập lệnh VNNI (Vector Neural Network Instructions) chuyên dụng cho AI, tương tự như nhân Gracemont (E) trước đó. Chi tiết này có thể thấy việc xử lý AI của Intel sẽ không hoàn toàn dựa vô NPU mà sẽ dàn trải trên nhiều thành phần.

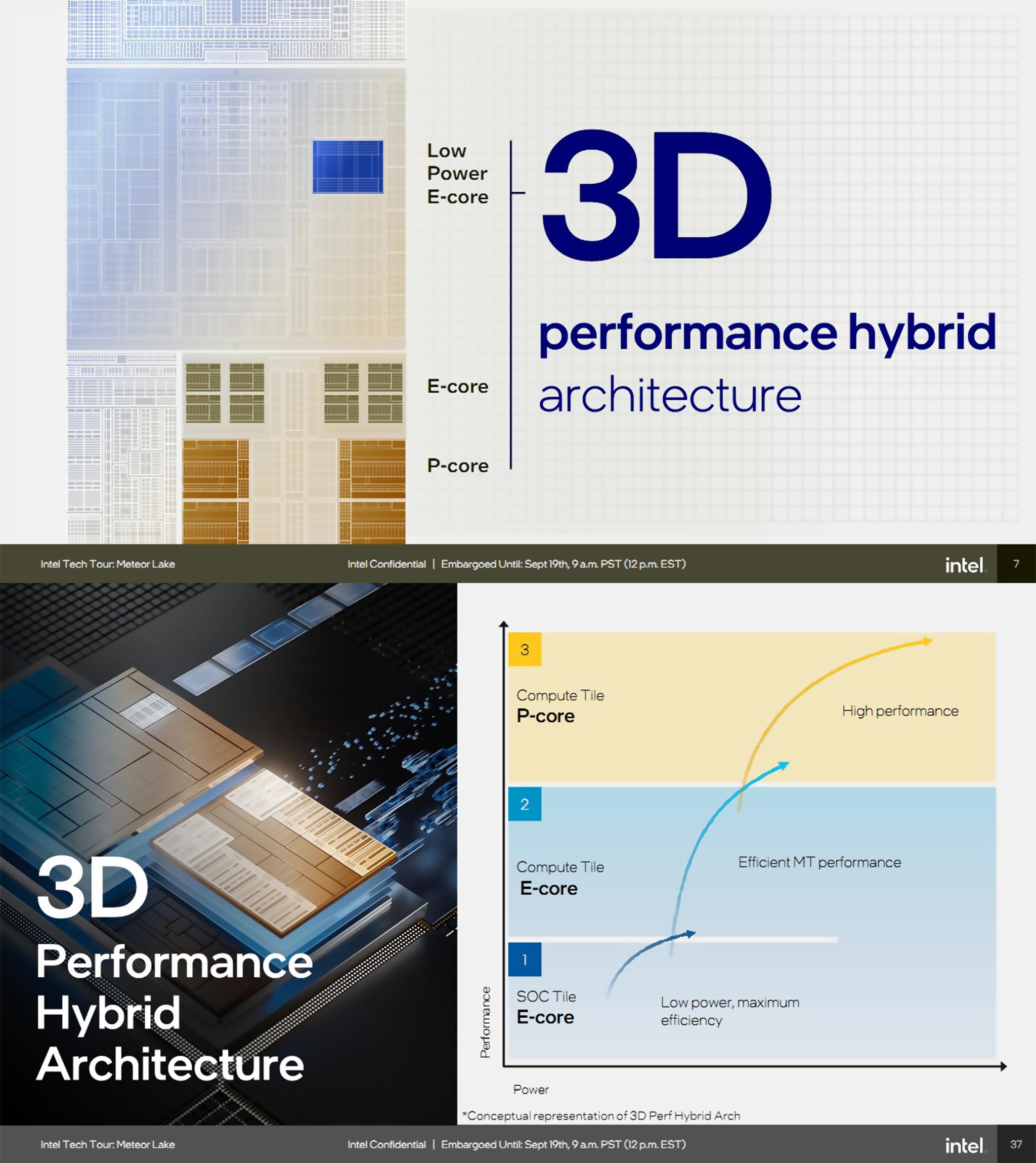

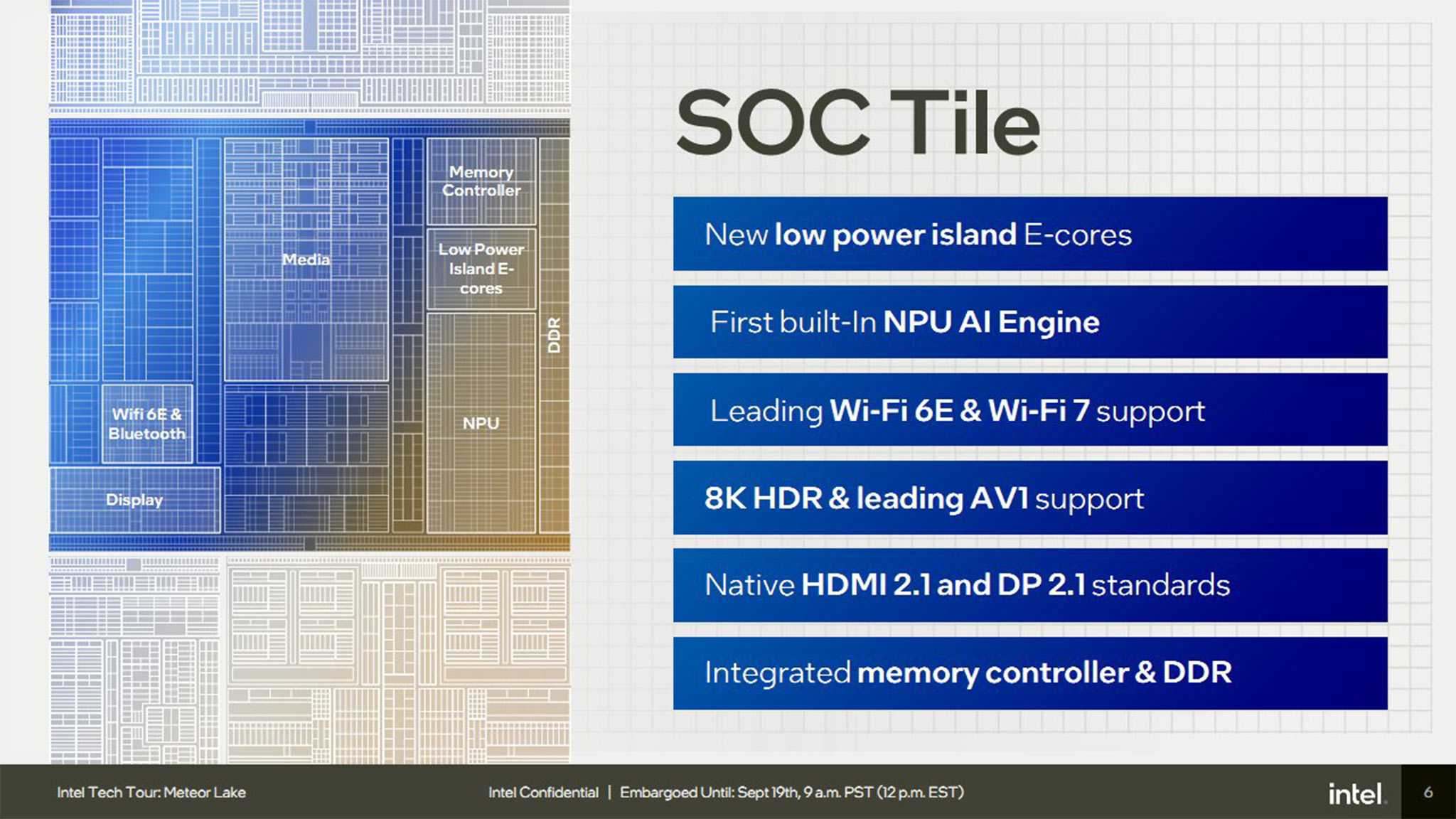

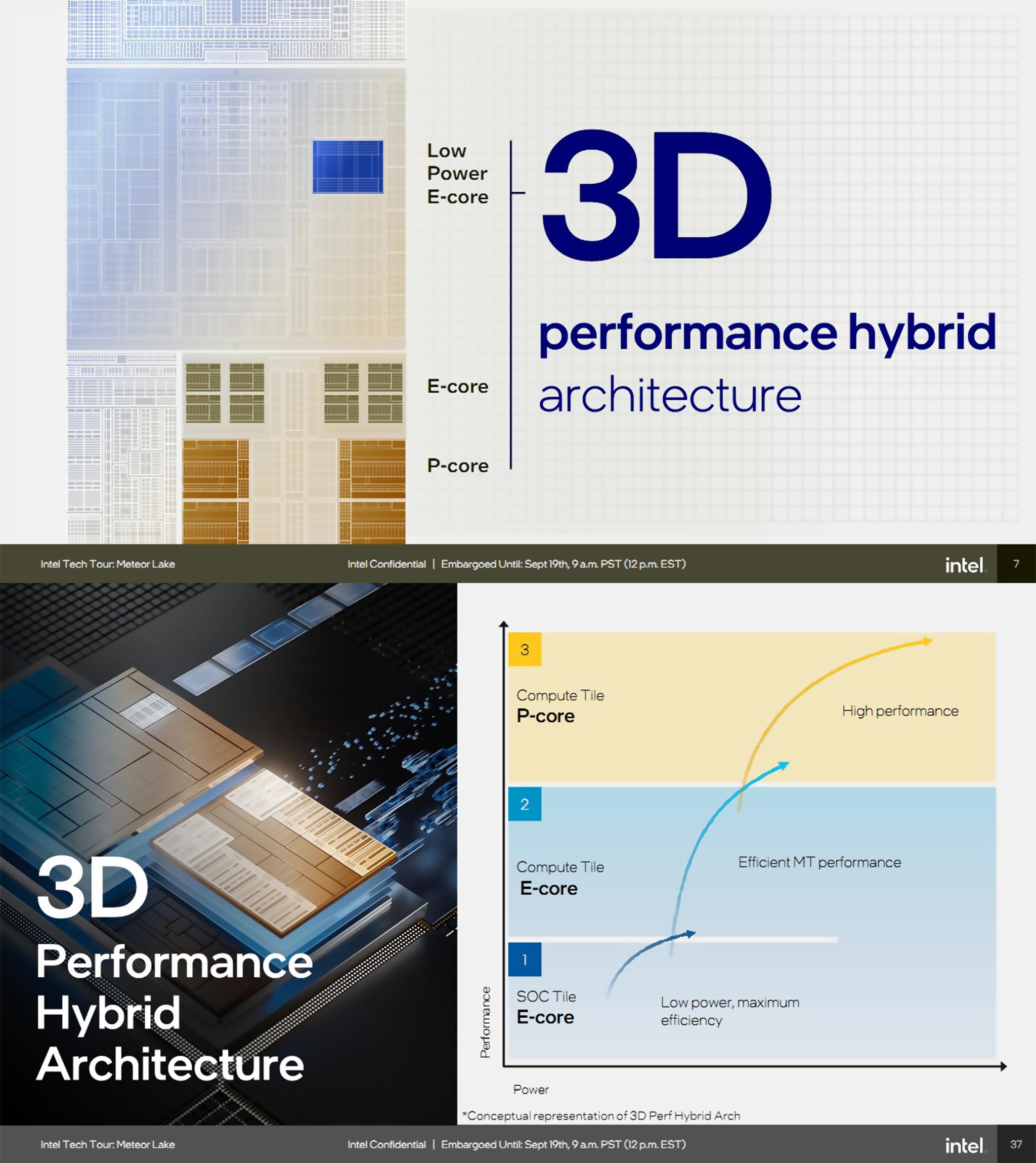

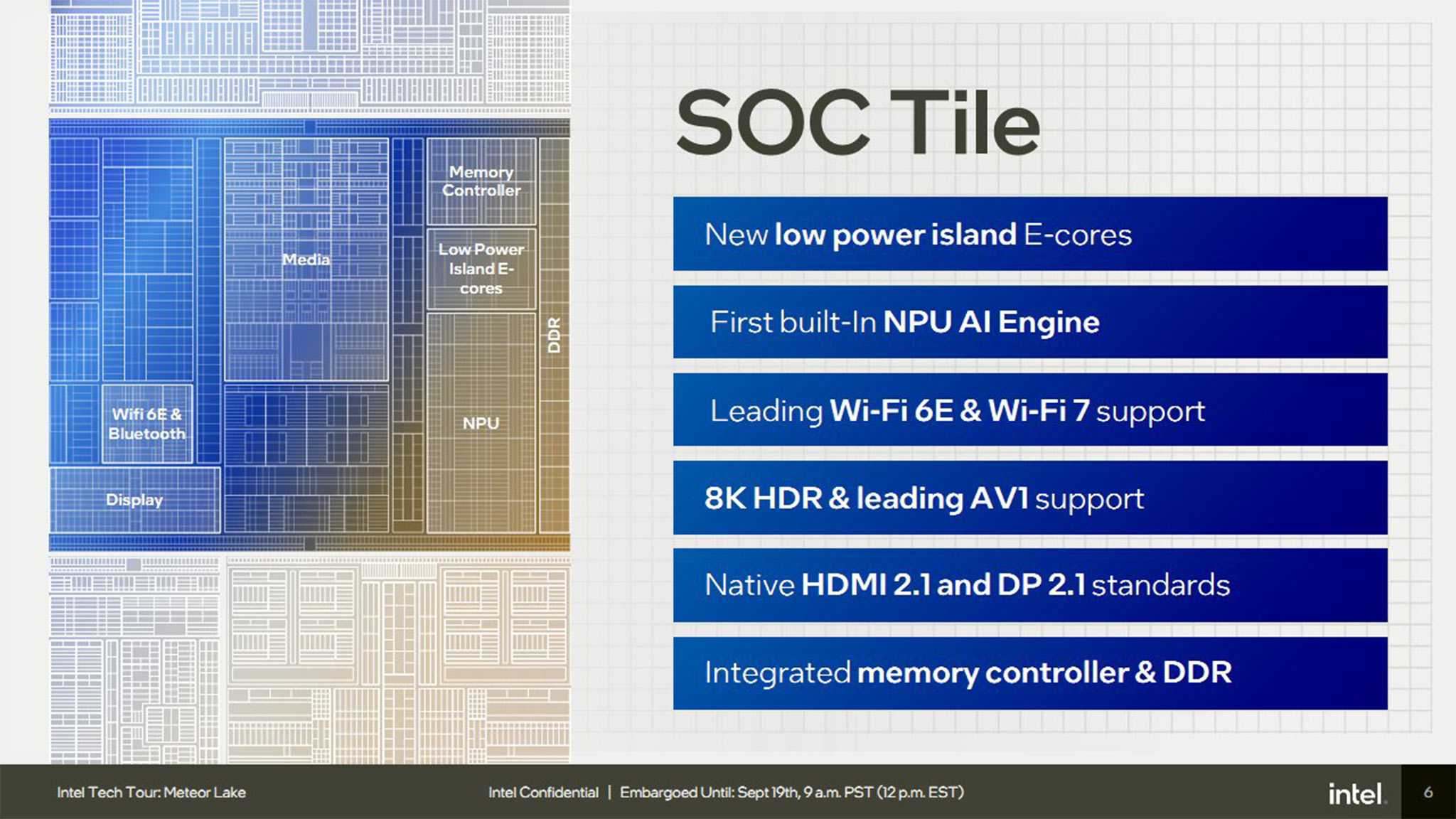

Nhưng không chỉ trang bị nhân E trên mỗi die điện toán, với MTL, Intel còn "chừa chỗ" cho một đám E-core nằm riêng trên die SoC với tên gọi Low Power Island. Tuy cùng kiến trúc Crestmont song 2 đám E-core này có khác biệt - die điện toán dùng tiến trình Intel 4 còn die SoC dùng TSMC 6N. Về mặt lý thuyết TSMC 6N là tiến trình tiết kiệm điện còn Intel 4 là hiệu suất cao. Chưa rõ 2 đám nhân E sẽ hoạt động thế nào nhưng ta có thể đoán nhân E "ngoài đảo" sẽ có xung và mức hao điện thấp hơn nhân E "trong nhà".

Vị trí "đảo" E-core trên SoC và 3 chế độ làm việc của CPU Meteor Lake

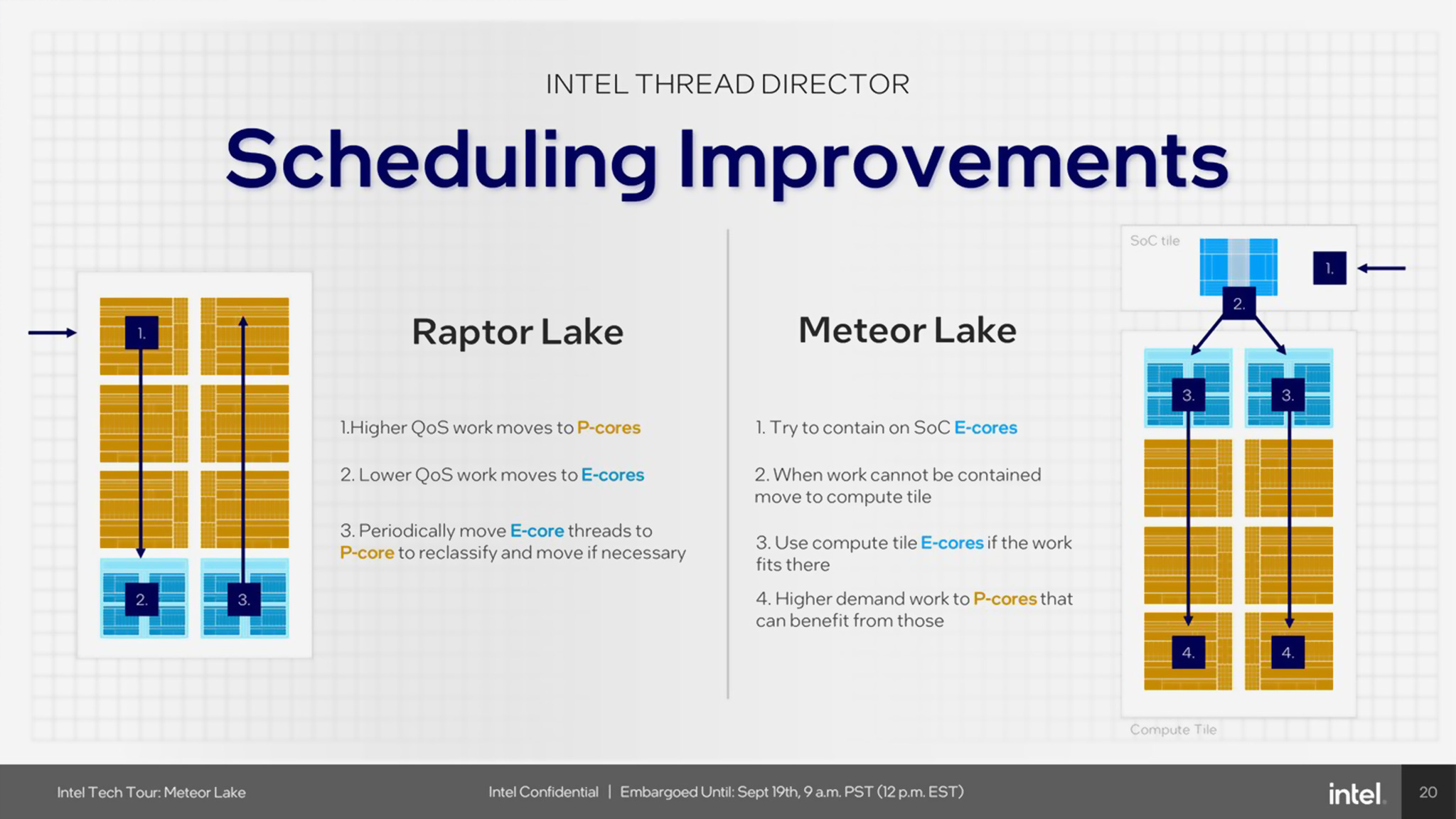

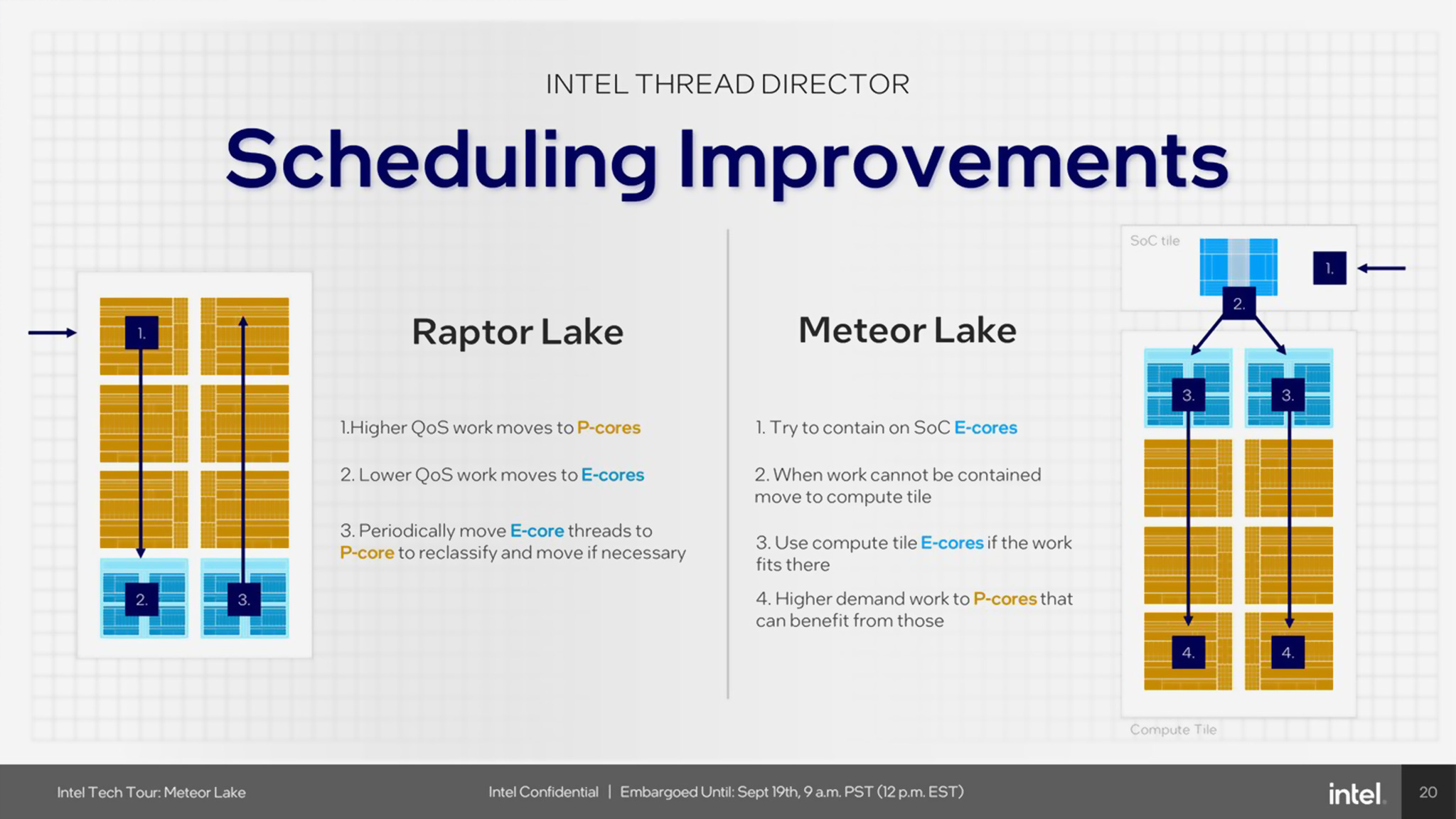

Một vấn đề quan trọng khác khi áp dụng cùng lúc 2 kiến trúc khác nhau trên cùng die điện toán chính là làm sao để phân chia công việc? Bắt đầu từ thế hệ chip kiến trúc hiệu năng lai đầu tiên, Intel đã bổ sung thêm một thành phần chuyên môn có tên Thread Director (TD). Vai trò chính của TD là nhận các đầu việc mà hệ điều hành (OS) đưa xuống rồi "lựa cơm gắp mắm", giao việc đó cho nhân E hoặc P xử lý. Trên dòng chip cũ (Raptor Lake), cách TD làm việc sẽ là nhân P nhận trước các việc "nặng", rồi việc "nhẹ" chuyển qua nhân E, sau đó tuỳ tính chất phát sinh mà các nhân này sẽ hoán đổi công việc cho nhau (nhân E có thể "nghỉ việc" nếu không còn việc "nặng" để làm).

So sánh cách Thread Director làm việc trên Meteor Lake và thế hệ trước

Nhưng sang MTL, mọi thứ ngược lại. Trước tiên "người" nhận việc sẽ là các nhân E "ngoài đảo". Nếu các việc này không giải quyết được trên die SoC thì TD mới chuyển qua cho die điện toán phía sau. Tuy vậy, các nhân E "trong nhà" sẽ không được "ngồi chơi xơi nước" như thế hệ trước nữa mà phải "xắn tay vô làm". Trường hợp công việc quá nặng nhân E không kham nổi thì mới tới lượt nhân P "nhảy vào". Như vậy có thể thấy với MTL, Intel muốn đặt vấn đề hiệu quả tiêu thụ điện tới mức tối đa khi có tới 3 cấp độ (level) xử lý & tiêu thụ điện.

Thành thực mà nói, sức mạnh đồ hoạ của Intel trong bao nhiêu năm qua chưa hề được xem là mạnh. Mặc dù vài năm trở lại đây Intel đã có một đợt chuyển mình bằng cách dấn thân vô thị trường bằng dòng card đồ hoạ rời Arc, đó vẫn là một con đường gian nan và vất vả khi không chỉ các đối tác phần cứng (AIB) lẫn phần mềm (game developer) đều đã quá quen thuộc với AMD hoặc NVIDIA. Và liệu Intel có ra mắt sản phẩm đồ hoạ rời nào nữa không thì đó vẫn là một dấu hỏi lớn sau khi Gelsinger lên nắm quyền.

Tất nhiên nhân đồ hoạ trên MTL vẫn là đồ hoạ tích hợp chứ không phải đồ hoạ rời, nên chắc chắn là hiệu năng game của nó vẫn còn thấ, tuy nhiên không có nghĩa không có gì để cải thiện ở đây.

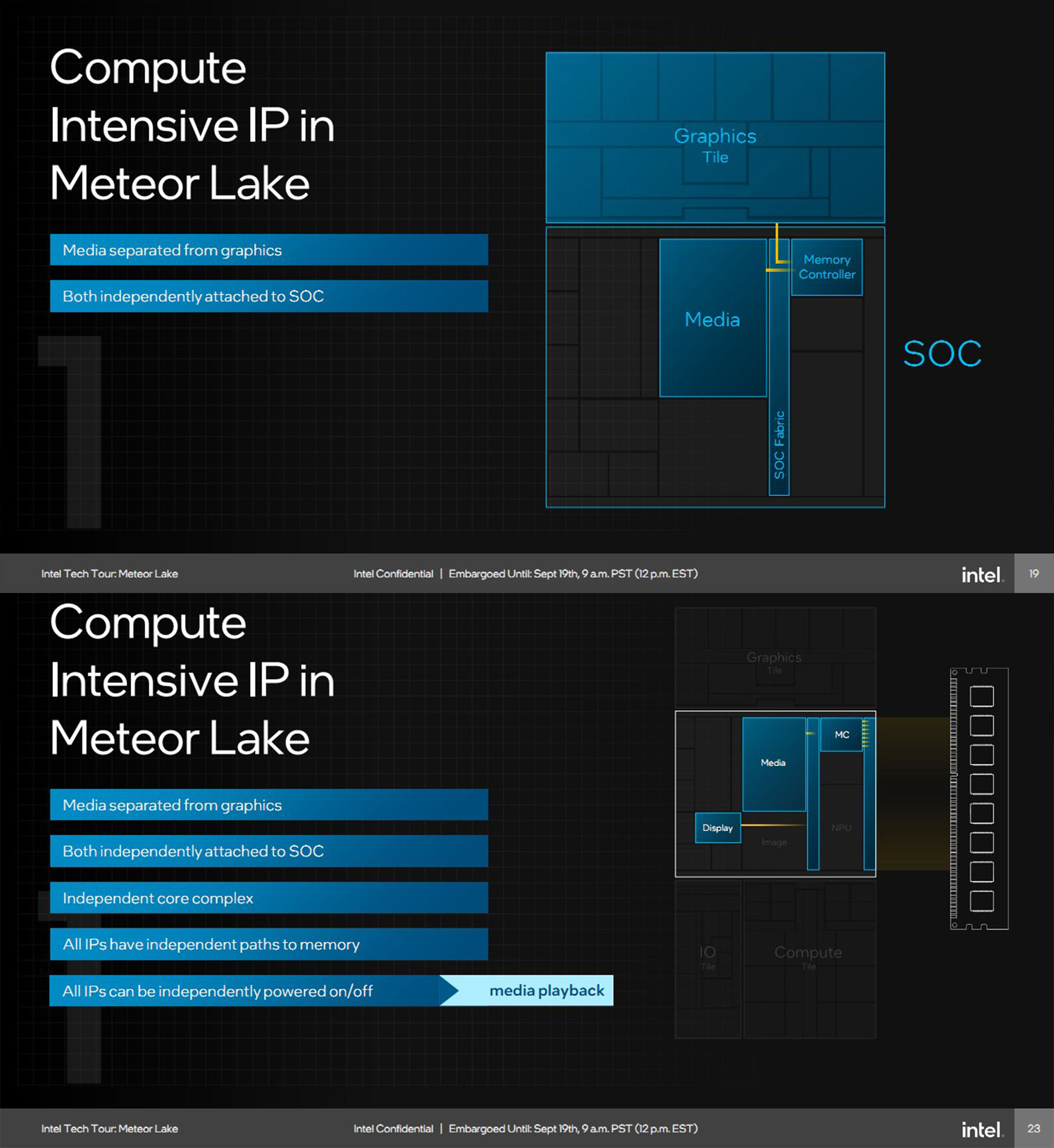

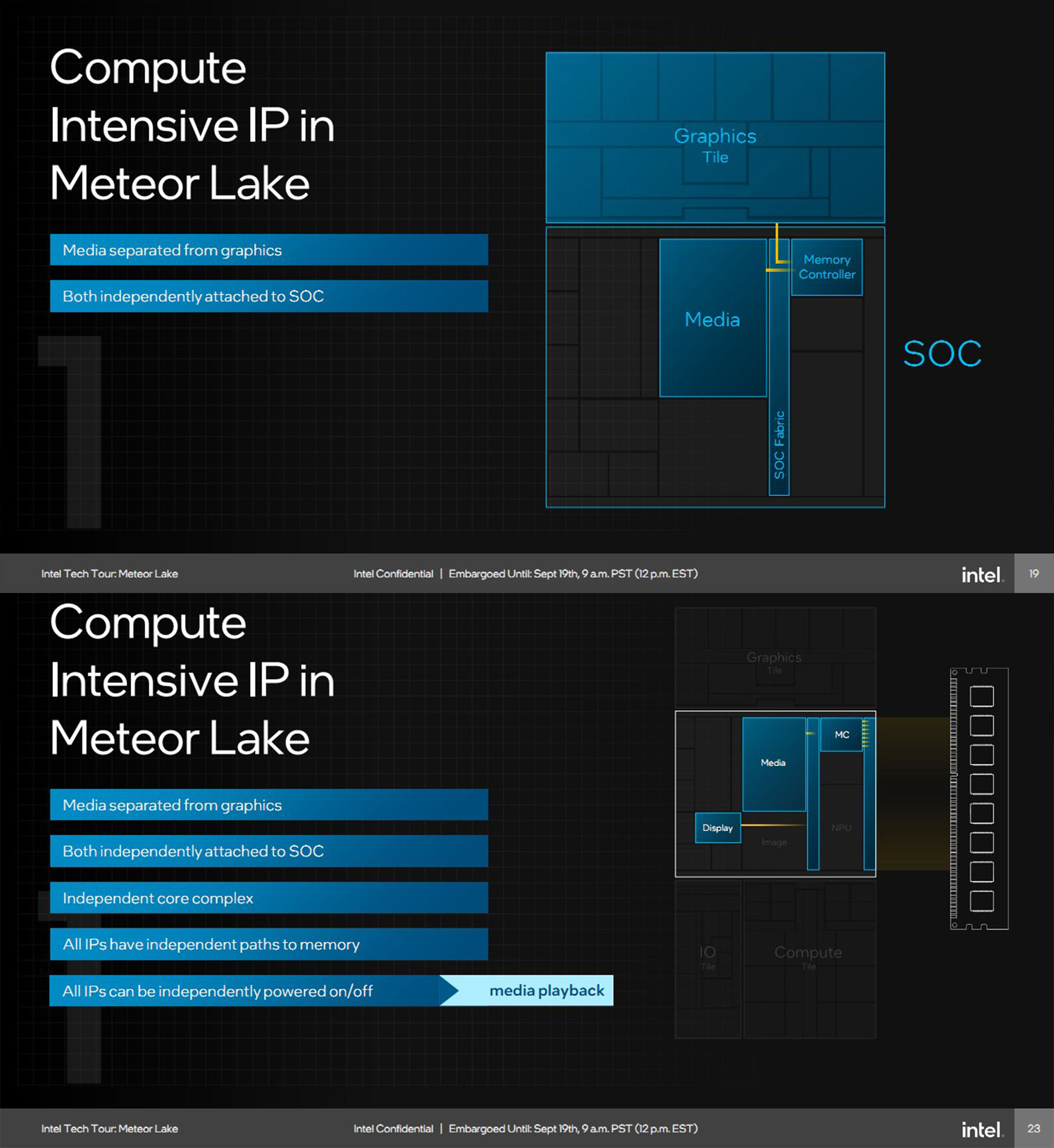

Nếu nói cho đúng, die SoC mới là die quan trọng nhất khi thiết kế MTL chứ không phải điện toán hay đồ hoạ. Trong quá trình phát triển chip, các kỹ sư Intel nhận ra việc xử lý các lệnh pipeline 3D thực chất khác hẳn việc xử lý media (phim ảnh), display (hiển thị màn hình)... Nhưng ở các thế hệ chip trước, các đơn vị media hay display đều nằm chung với các nhân đồ hoạ. Cách thiết kế này gây ra một sự lãng phí là kể cả khi nhân đồ hoạ không vận hành thì nó vẫn phải được "bật" để có điện cho các đơn vị media/display làm việc.

Các thành phần xử lý media và display đều tách khỏi GPU trên Meteor Lake

Vì thế khi chuyển qua MTL, các kỹ sư Intel đã "tách hộ khẩu" phần xử lý media/display từ die đồ hoạ sang die SoC. Bước đi này biến die SoC thành die thực hiện nhiều chức năng nhất con chip và nó cũng là die lớn nhất trong toàn bộ 4 die MTL.

Tuy không phải là die cho hiệu suất điện toán cao nhất, nhưng SoC lại là die nắm giữ nhiều vai trò nhất trên MTL. Ngoài "đảo" E-core để làm thay die điện toán hay các đơn vị media/display tiết kiệm điện thay cho die đồ hoạ, die SoC còn chứa cả nhân NPU dành cho AI, trình điều khiển bộ nhớ làm việc với RAM, cũng như cả thành phần thu phát sóng Wi-Fi lẫn Bluetooth cho toàn con chip.

SoC là nơi chứa nhiều thành phần nhất trên Meteor Lake

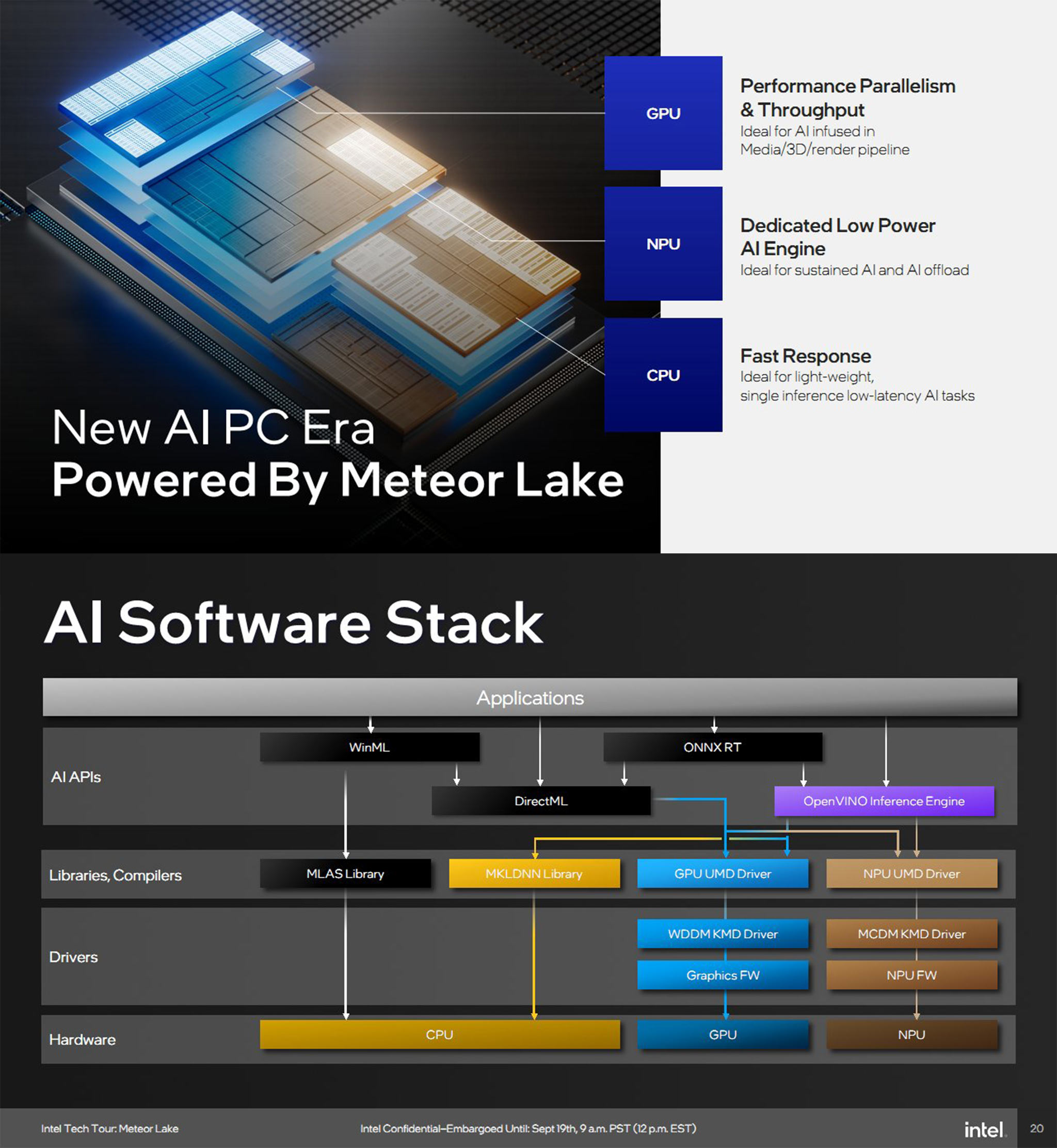

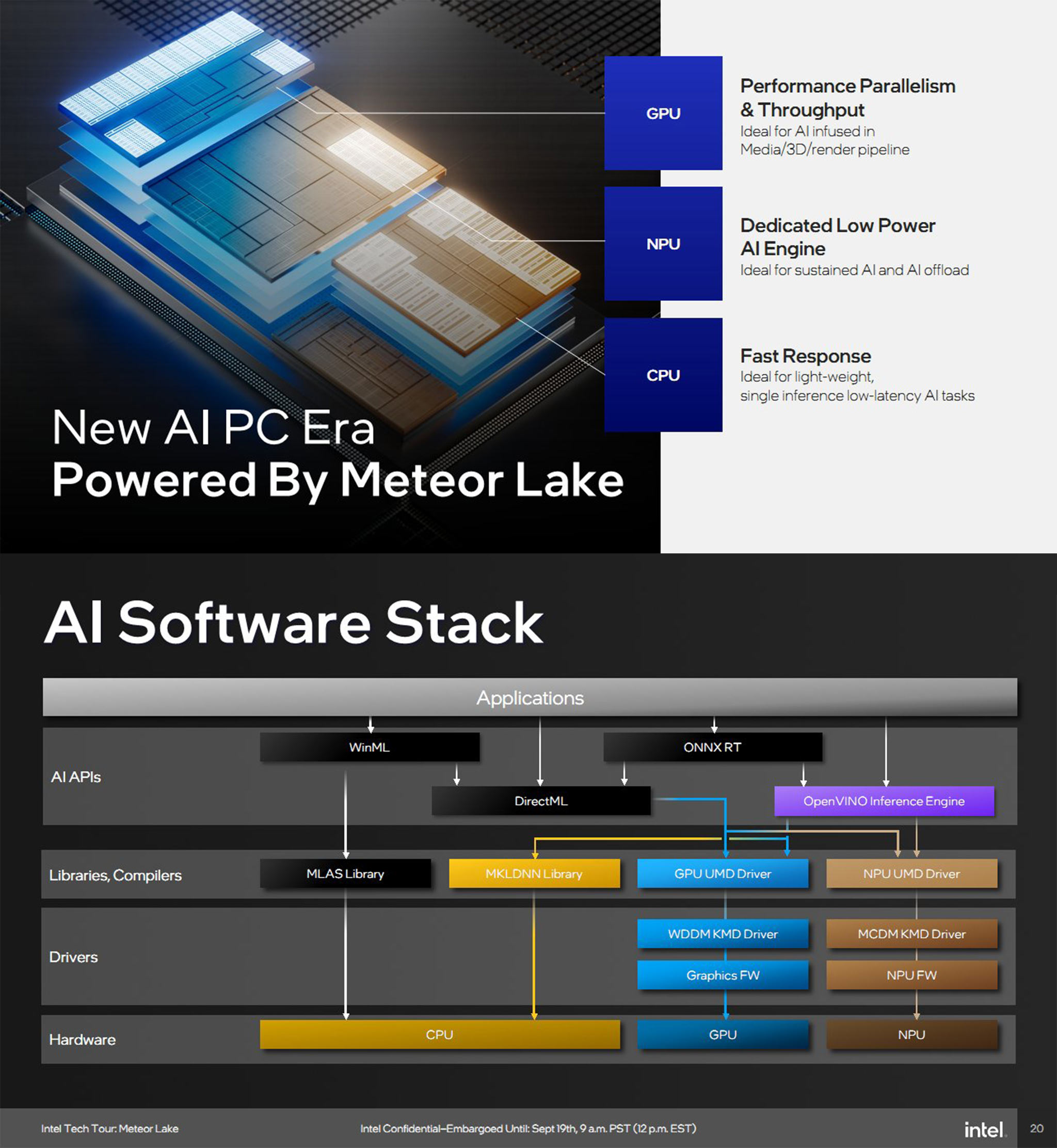

Hiện tại, câu chuyện về AI của Intel có khá nhiều thứ để bàn. Nhưng trong khuôn khổ bài này, chúng ta chỉ tóm gọn rằng AI của Intel sẽ không đơn thuần là một thành phần cố định. Kiến trúc AI của Intel được định đoạt nhiều bởi các API, trình biên dịch, thư viện phần mềm, driver, phần cứng. Vì vậy, bất kể là CPU, GPU hay NPU đều có thể chạy AI miễn là có hệ sinh thái ứng dụng dành cho chúng.

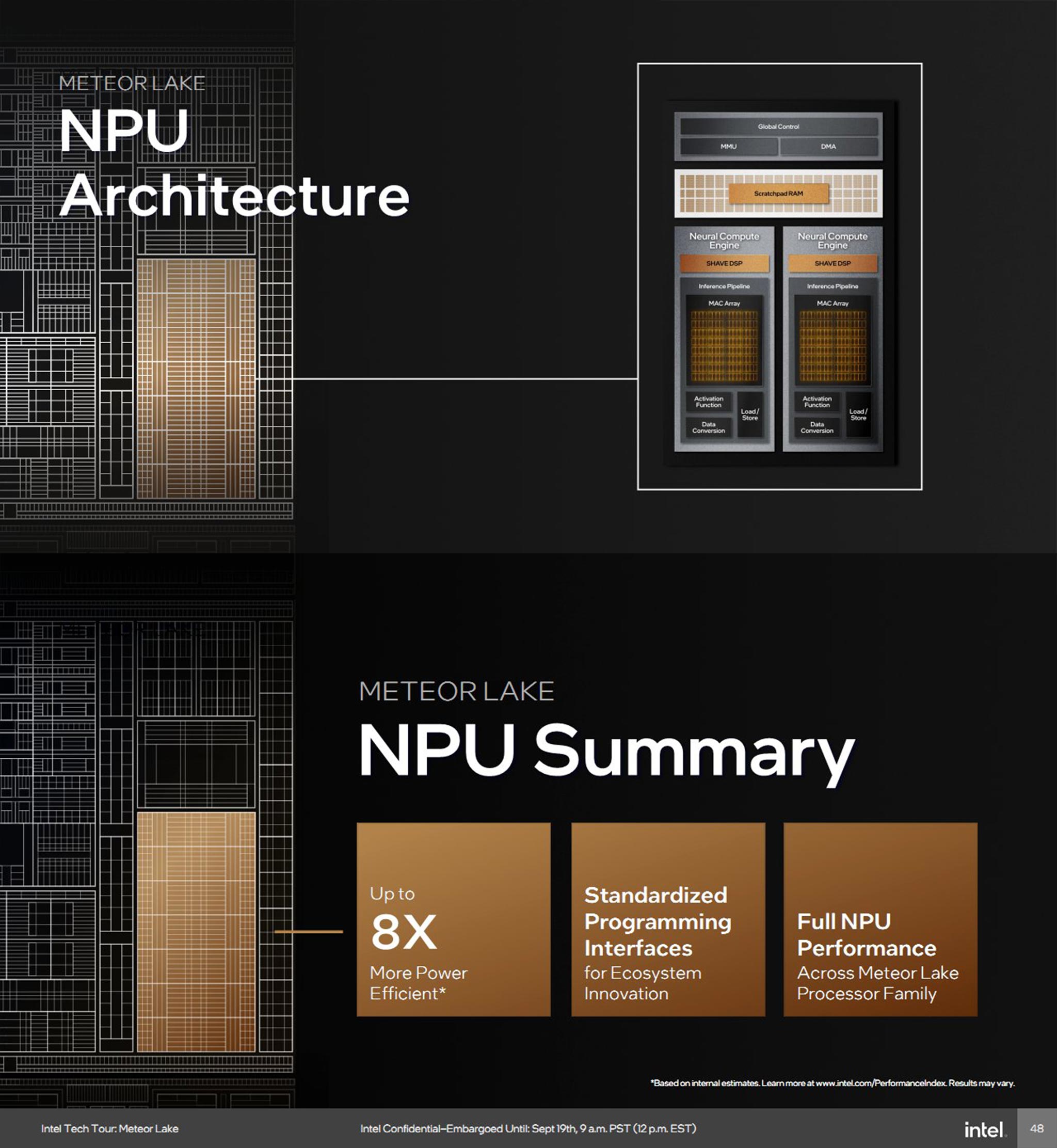

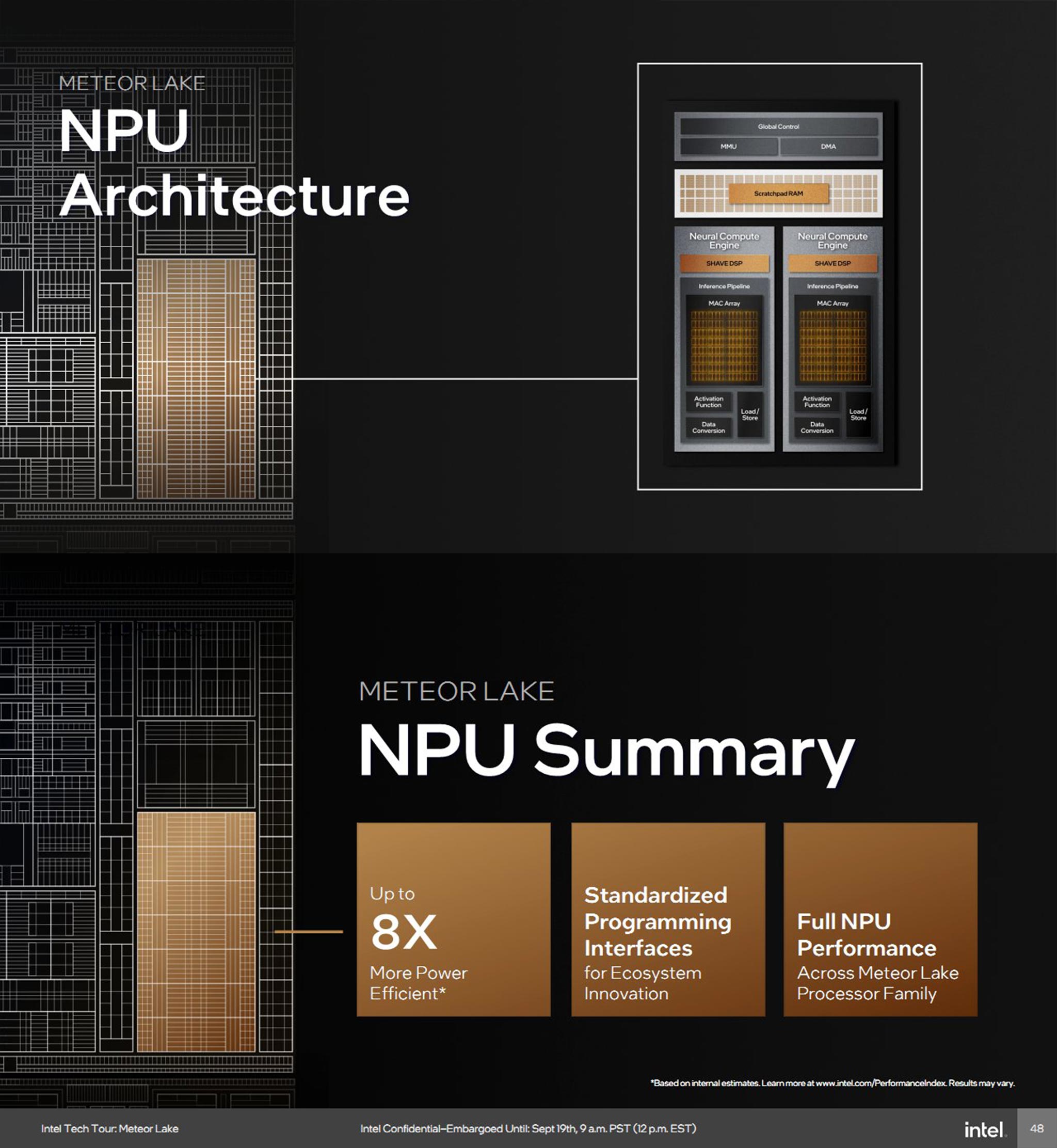

Riêng về NPU của Intel, nó được thiết kế để xử lý những ứng dụng AI được chuẩn hoá theo OpenVINO. Khối NPU này gồm 2 neural engine có cấu hình và giao diện tương tự các bộ DSP chủ yếu xử lý các dữ liệu điện toán dạng INT8 hoặc FP16. Intel cho biết các NPU có hiệu quả tiêu thụ điện gấp 8 lần song không nói rõ khi so sánh với cái gì, nhưng ta có thể đoán đó là khi xử lý AI trên CPU.

Không tự dưng mà Intel nói MTL là cuộc cách mạng kiến trúc lớn nhất của hãng trong 40 năm qua. Đó là vì MTL không chỉ thuần tuý là sự cải thiện hiệu năng so với thế hệ trước, mà nó còn là sự thay đổi cơ bản nhận thức về CPU nói riêng hoặc chip nói chung. Nếu như trước đây các cải thiện về kiến trúc chip chỉ tập trung vào CPU thì nay mọi thứ đã khác.

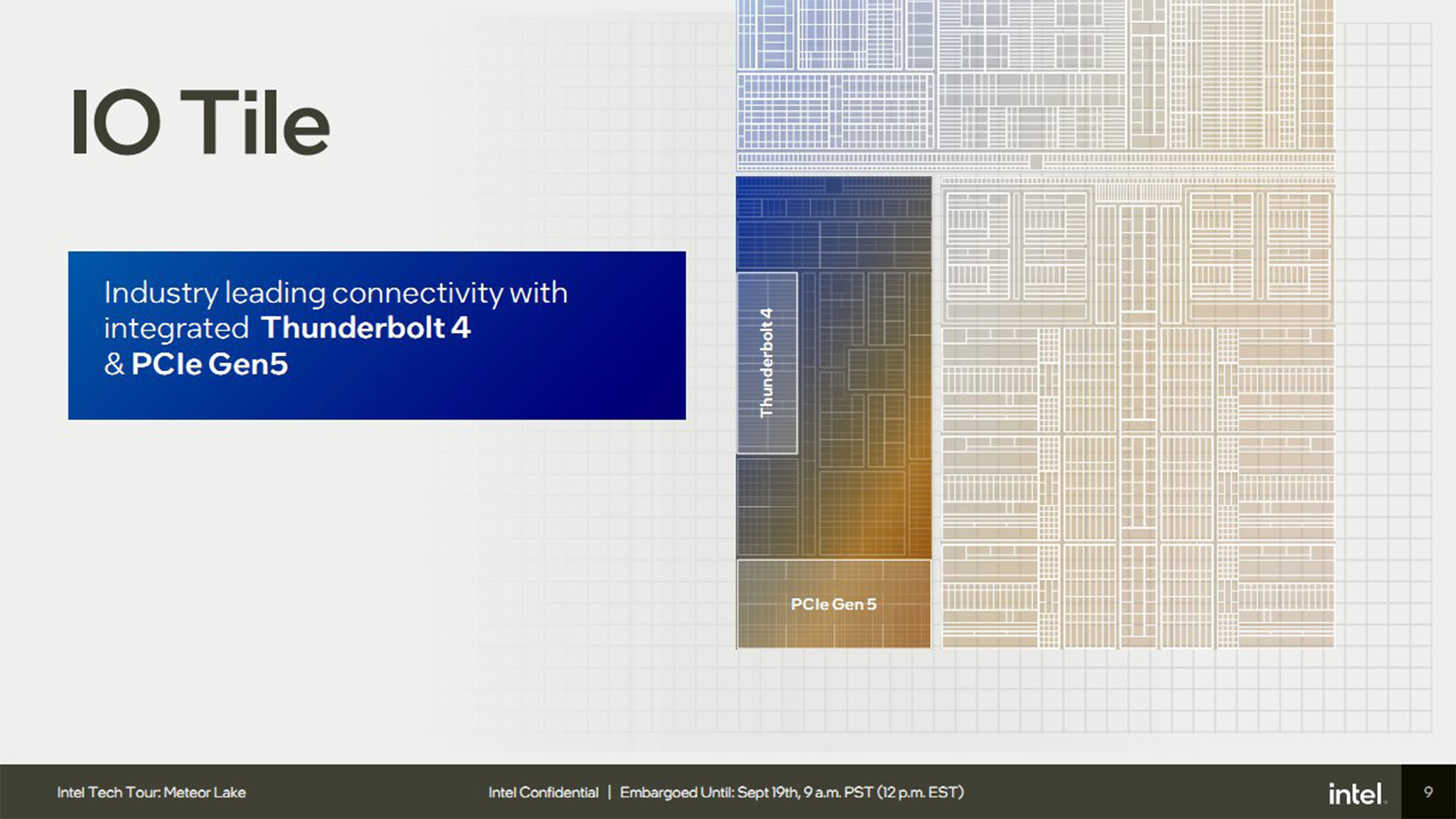

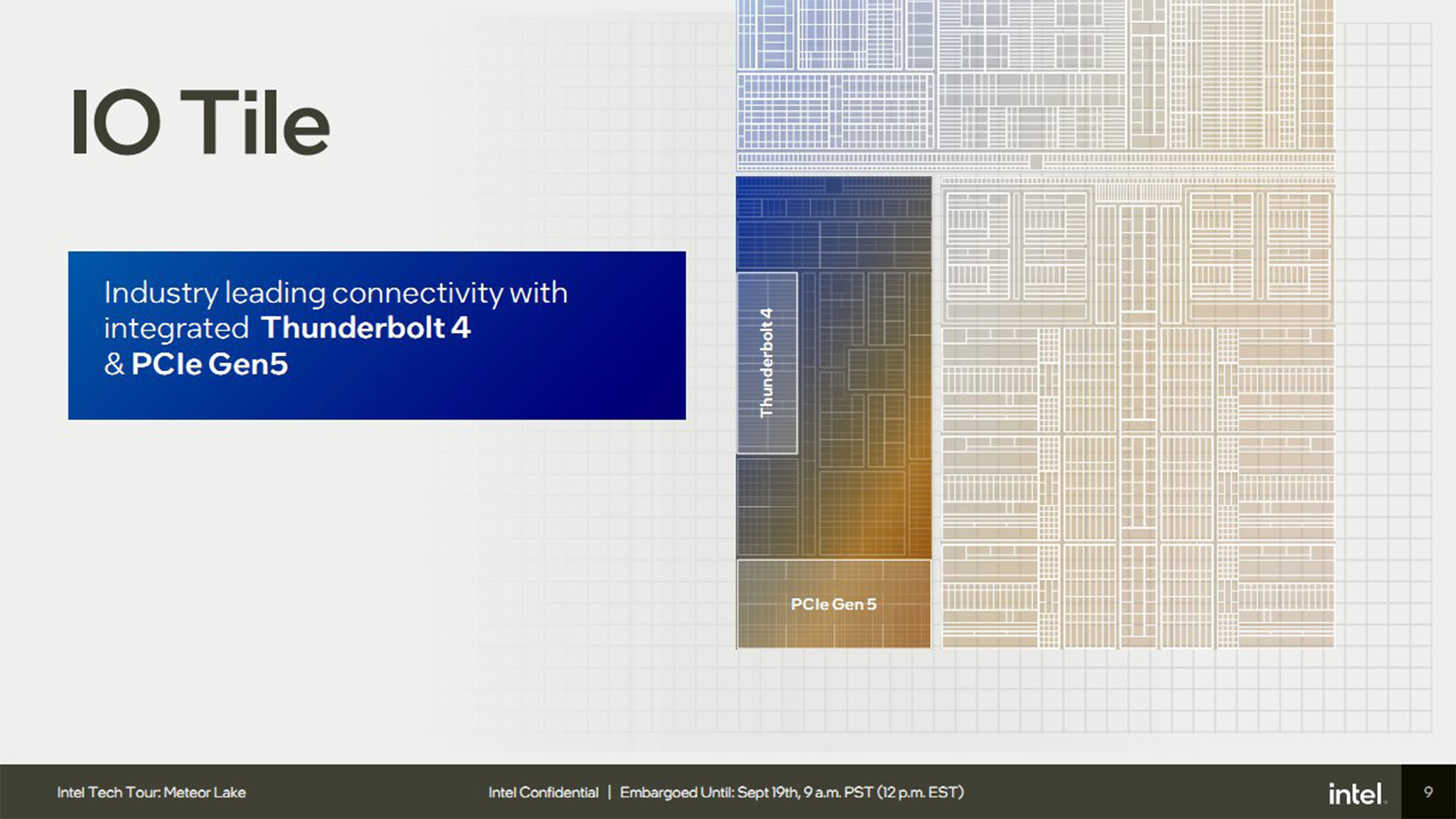

Vị trí và chức năng die IO trên Meteor Lake

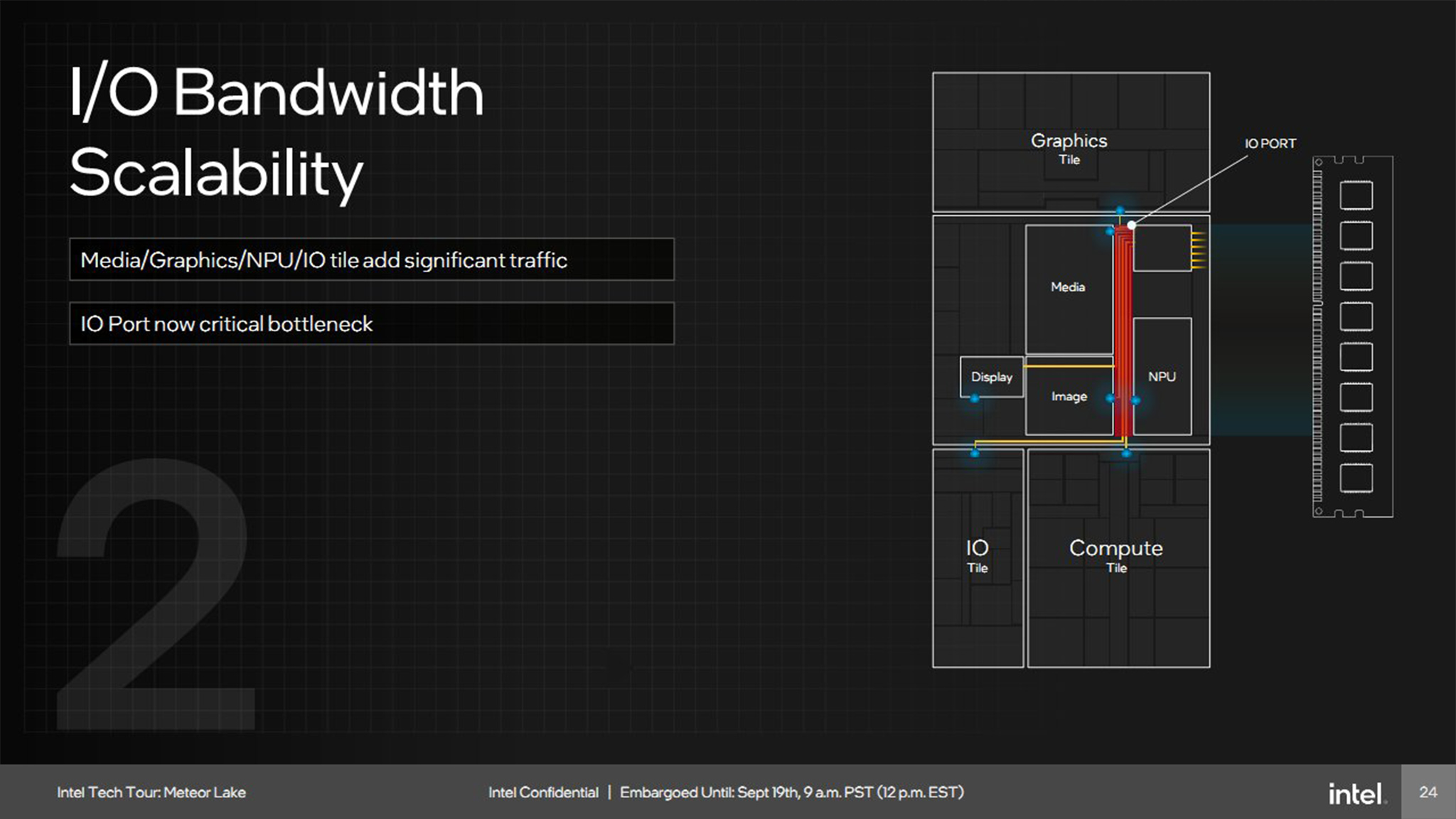

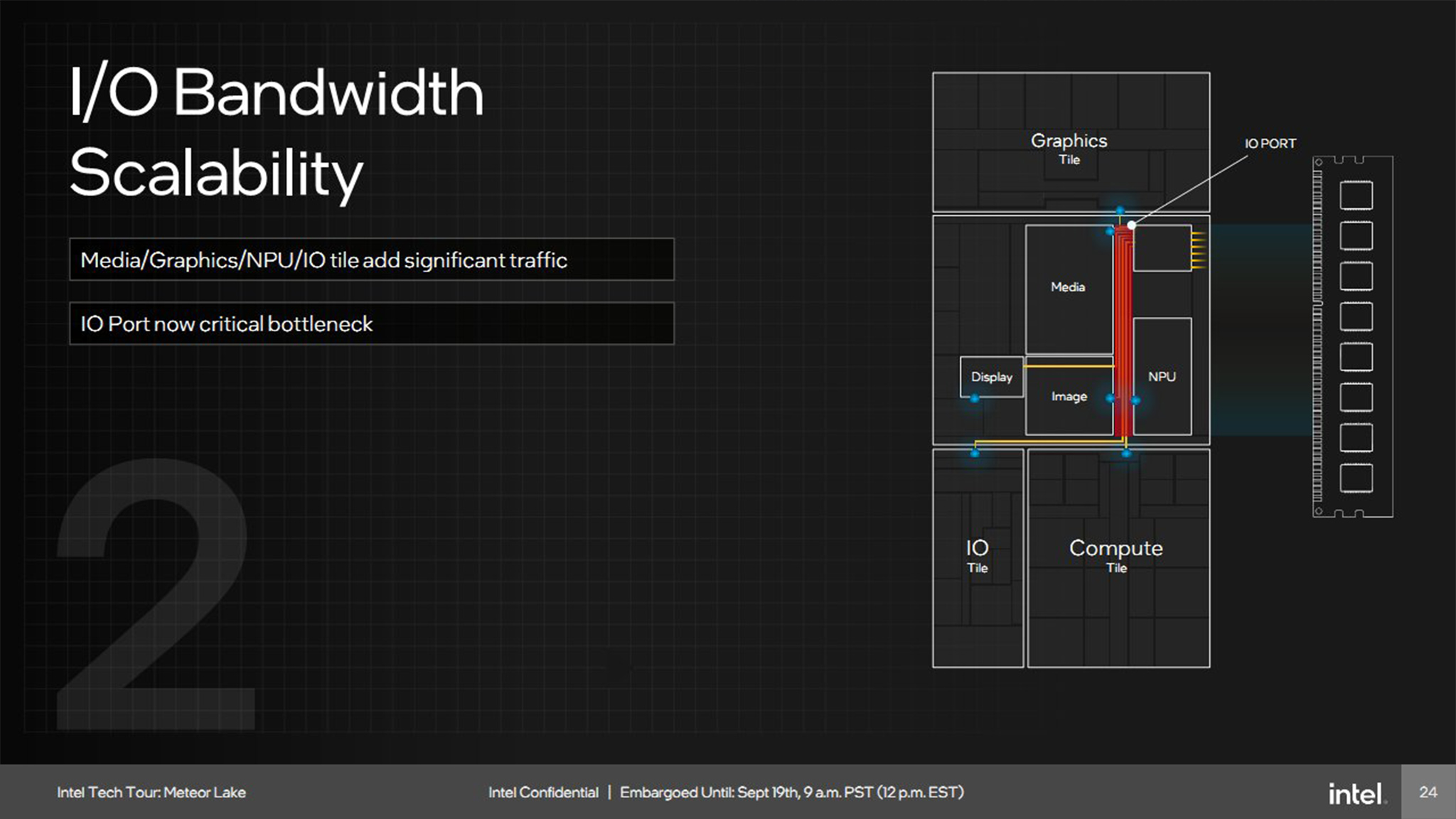

Trong thế giới điện toán đa hình dạng như ngày nay, vai trò của CPU đã bớt đi ít nhiều. Thay vào đó chúng ta có GPU, có AI, có các đơn vị chức năng cố định như media encoder/decoder... Nhưng tất cả cùng có điểm chung là cần nhiều băng thông dữ liệu. Nếu cách thức chuyển giao dữ liệu không có gì thay đổi thì hiện tượng nghẽn cổ chai sẽ xảy ra thường xuyên, bất kể là CPU có mạnh tới cỡ nào.

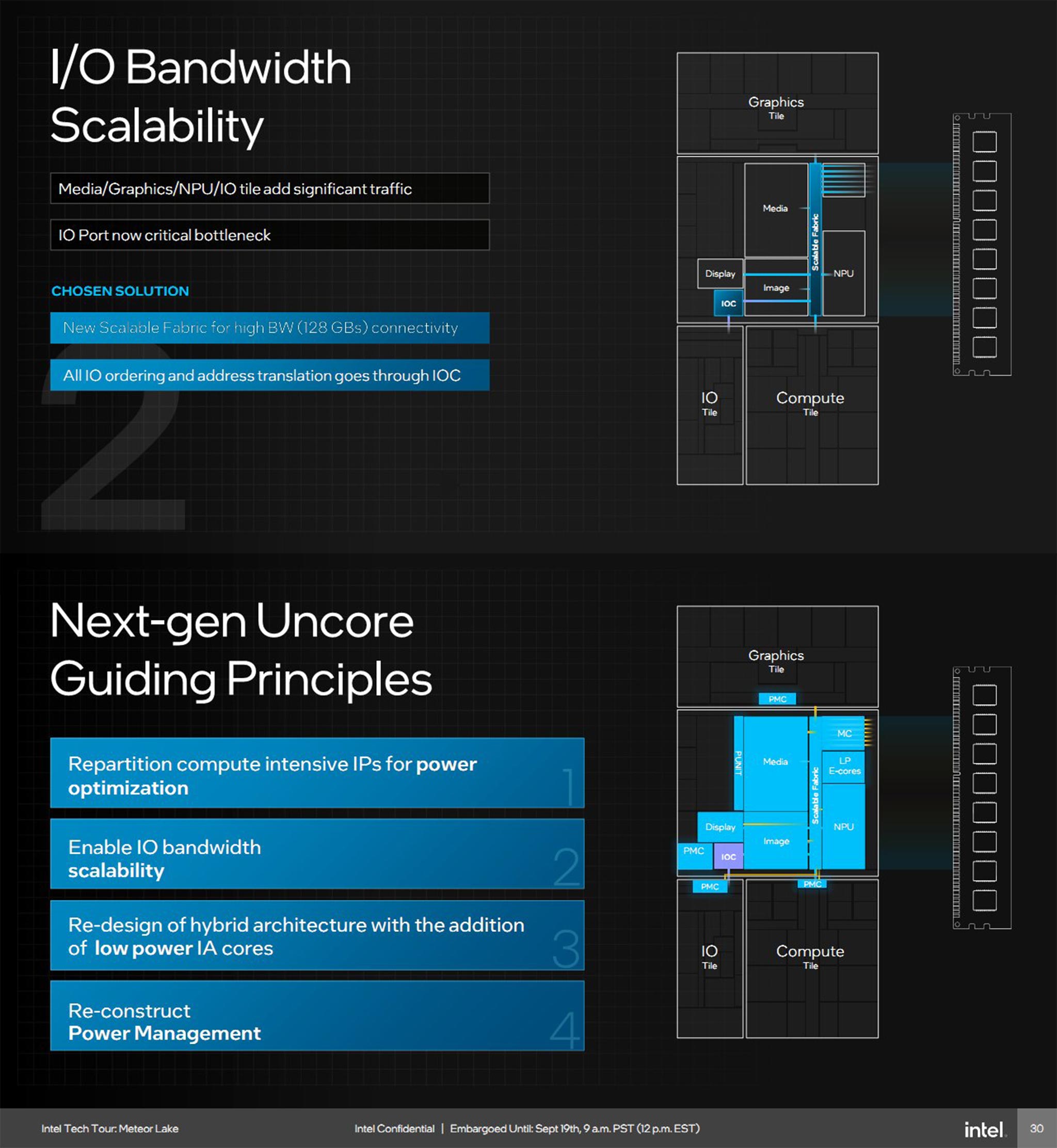

Với rất nhiều thành phần mới, nhu cầu trao đổi dữ liệu tăng lên đáng kể

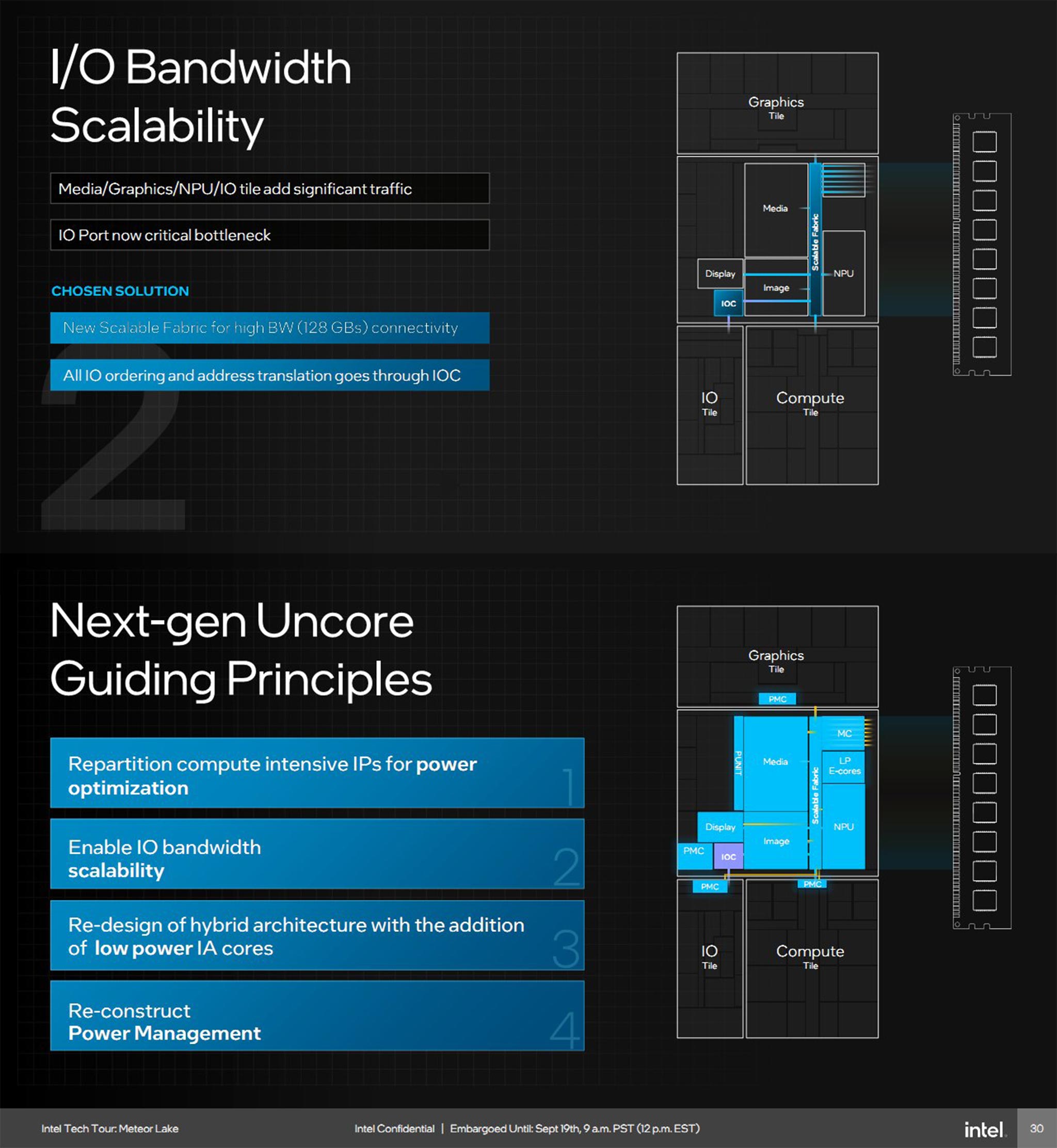

Vì thế mà trên MTL, die IO sẽ không làm việc trực tiếp với die CPU như các thế hệ trước. Thay vào đó, die SoC mới là "đạo diễn" chính. Thực tế là mọi lệnh nhập xuất (input output) dữ liệu đều được bộ phận IOC thực hiện và bộ phận này nằm trên die SoC. Dữ liệu sau khi được IOC nhận sẽ được đưa vào kênh Scalable Fabric. Từ đây, chúng có thể toả đi đến mọi nơi như "đảo" E-core, NPU, Media, CPU, GPU...

Die SoC đóng vai trò quan trọng trong việc trao đổi dữ liệu trên Meteor Lake

Nhìn chung, Scalable Fabric cũng gần tương tự như Infinity Fabric bên AMD, khi việc nhân xử lý ngày càng nhiều thì nhu cầu trao đổi dữ liệu cũng ngày một lớn. Việc làm ra một nhân xử lý đồ sộ nhưng không thể đáp ứng đủ dữ liệu cho nó cũng khiến cho kiến trúc bị "đói ăn" và không phát huy được hết sức mạnh của nó.

Có thể nói là còn quá sớm để biết được liệu MTL trên thực tế sẽ thế nào, có mỹ mãn như những lời có cánh của Intel hay không. Nhưng việc đổi ngôi CEO có tác động không nhỏ tới việc các sản phẩm của hãng này sẽ ra thế nào. Kể từ khi Gelsinger lên nắm quyền thay Krzanich, đại gia x86 đã có nhiều thay đổi cơ bản. Trong đó Intel dần cắt bớt những mảng kinh doanh mang tính... "linh tinh".

Có câu "bỏ trứng vào nhiều rổ", song khi không có cái rổ nào "đàng hoàng" thì điều cần làm là tập trung vào những sản phẩm cốt lõi của chính mình. Lẽ tất nhiên sẽ cần có thời gian để mọi thứ trở về quỹ đạo ban đầu của nó. Điều rõ ràng là Intel đã không còn đứng đầu về bán dẫn như bao năm trước, vậy nên để có thể theo kịp các đối thủ sẽ không phải chuyện trong một hai ngày. Sau một loạt các "Lake" (hay "Too Little Too Late"?) ngày càng nóng và tốn điện hơn, giờ có lẽ là lúc để một sản phẩm đáng được chờ đợi ra đời.

Trên thực tế, chẳng ai biết MTL có phải là con chip PC di động mạnh nhất khi ra mắt (vào giữa tháng 12 này), nhưng những thay đổi mà Intel đặt ra, ít nhất về mặt tầm nhìn vi xử lý, cho thấy hãng này đã "bắt kịp" xu thế với những công ty công nghệ khác. Với việc đặt trọng tâm con chip nằm ở die SoC thay cho CPU, nó cho thấy Intel đã thực sự "thức tỉnh" và khi người khổng lồ tỉnh giấc thì sẽ có rất nhiều điều xảy ra...

Có thể nói cuộc sống ngày nay của chúng ta đã thay đổi rất nhiều so với vài chục năm trước, nhất là khi điện toán ngày càng phổ biến hơn trong đời sống mỗi người. Với Internet of Things (IoT), mọi thứ đều kết nối và trong bất kỳ thiết bị cá nhân nào cũng cần 1 con chip để xử lý. Có thể đó là 1 điện thoại thông minh, laptop hay tablet hoặc 1 hệ thống máy chủ (server) hay 1 thiết bị đeo (wearable). Những con chip xử lý nằm trong chúng là thành phần cơ bản nhất mà mỗi người dùng, hay nói đúng hơn là mỗi thiết bị đều cần có.

Nhưng câu chuyện của chúng ta hôm nay sẽ không phải là một con chip "vạn năng" có thể làm được mọi thứ trên trời dưới đất - hoặc ít nhất là chúng ta sẽ không đi quá xa những gì mà chính nhà sản xuất công bố. Nội dung này sẽ tập trung vào những hệ thống PC "truyền thống" mà 2 đối thủ chính là AMD và Intel đã "so găng" trong suốt hàng chục năm qua. Tất nhiên thị trường PC ngày nay đã có nhiều thay đổi, chúng ta có Apple Silicon và Qualcomm cùng đang "mấp mé ngoài sân khấu", nhưng 2 nhân vật chính của buổi diễn này vẫn đang là 2 đại gia x86. Vậy Intel đang nắm quân bài gì trong tay và Meteor Lake (MTL) có điểm gì đặc biệt trước "phong ba bão tố" thị trường PC?

Một điều có thể thấy rõ là MTL sẽ được ra mắt trong một hoàn cảnh hết sức đặc biệt với Intel. Sau quá nhiều năm "ngủ quên", hình ảnh và vị thế của Intel đang trở nên yếu hơn bao giờ hết. Kiến trúc Zen của AMD đang mặc sức làm mưa làm gió trên thị trường, còn các con chip Mx của Apple liên tục "dồn" Intel vô chân tường dù cho khác kiến trúc. Riêng Qualcomm tuy chưa có sản phẩm chính thức nhưng mối đe doạ không hề nhỏ, trước mắt có thể là Snapdragon X Elite.

4 trọng điểm của Meteor Lake

Mặc dù một loạt Rocket Lake, Tiger Lake, Alder Lake, Raptor Lake (Intel có vẻ "nghiện" Lake) cùng được tung ra trong mấy năm qua song chúng hầu hết chỉ mang tính "chống đỡ" chứ không thực sự có nhiều cải thiện về kiến trúc. Intel chủ yếu tập trung vào việc đẩy xung nhịp lên mức tối đa và kéo dài thời gian turbo lâu nhất có thể. Cách làm này tuy vẫn giúp làm tăng hiệu năng nhưng điểm trừ là nó tốn quá nhiều điện và toả ra quá nhiều nhiệt, nên không thể xem là một cải thiện thực sự về kiến trúc.

Một điểm ngoài lề khác tuy không phải điểm nhấn của ngày hôm nay nhưng có ý nghĩa khá quan trọng với MTL - CEO hiện tại của Intel là Patrick Paul Gelsinger, vốn là một nhân vật "đúng chất" kỹ sư và vi xử lý (tương tự Lisa Su bên AMD). Trước đó Intel được lãnh đạo bởi Brian Krzanich, người không có mấy kinh nghiệm về vi xử lý và có những quyết định đầu tư "ngoài luồng". Các sản phẩm CPU của Intel trong giai đoạn Krzanich thực sự không có nhiều ấn tượng trong khi sản phẩm của Lisa Su ngày càng sắc nét hơn. Còn MTL được Gelsinger chính tay "cầm trịch", nên thành bại của MTL có thể nói sẽ quyết định cả vị thế của Gelsinger ở Intel sau này...

Patrick Paul Gelsinger, CEO Intel đương nhiệm.

Nhưng "có thực mới vực được đạo", phải có nguyên liệu tốt thì Gelsinger mới có thể làm ra một sản phẩm tốt, và đây là những thứ mà MTL được "vũ trang" cho một thị trường PC đầy sóng gió:

- Mẫu chip tiến trình Intel 4 đầu tiên

- Mẫu chip dạng chiplet/tile đầu tiên của Intel

- Sử dụng công nghệ đóng gói Foveros để liên kết các die chiplet khác nhau vào cùng 1 con chip

- Kiến trúc nhân P-core (Redwood) và E-core (Crestmont) hoàn toàn mới

- Nhân đồ hoạ Intel Arc mới

- Mẫu chip Intel đầu tiên có nhân AI (NPU)

- Kiến trúc 3D kết hợp với một cụm E-core độc lập nằm trong nhân SoC (low power island)

- Thiết kế xử lý Media, Display... được chuyển sang nhân SoC thay vì đồ hoạ

- Hỗ trợ chuẩn Wi-Fi 6E & 7, Thunderbolt 4 và PCI Express 5 mới nhất

Các tính năng chính của Meteor Lake.

Mặc dù kiến trúc (arch) là thứ quan trọng nhất khi nói về một con chip, công nghệ bán dẫn để làm ra nó vẫn là thứ có ảnh hưởng hiển hiện và rõ ràng nhất. Trong những năm trở lại đây, Intel đã không còn dẫn đầu về tiến trình bán dẫn như đã từng. Quá trình đầu tư mạnh mẽ và quyết liệt của TSMC hay Samsung đều đẩy Intel tụt lại phía sau. Có thể nói các sản phẩm "Lake" trước đấy của Intel cũng sẽ không bị đánh giá thấp nếu chúng không "bám trụ" vào công nghệ 14++++ hay 10++ nm.

So sánh công nghệ Intel 4 vs. Intel 7

Do vậy việc sử dụng tiến trình Intel 4 (7 nm) sẽ là một thay đổi quan trọng của MTL, ít nhất so với các sản phẩm "Lake" trước đó. Một chi tiết thú vị là không phải toàn bộ con chip sẽ dùng chung công nghệ Intel 4 - die đồ hoạ sẽ được gia công trên tiến trình TSMC 5N (5 nm) còn die SoC là trên TSMC 6N (6 nm). Và đây cũng là con chip đầu tiên chuyển từ thiết kế đơn chip (monolithic) sang đa chip (chiplet/tile) của Intel, giống cách AMD đang làm với Zen.

Việc sử dụng thiết kế chiplet cũng đồng nghĩa với việc Intel buộc phải áp dụng một kỹ thuật đóng gói chip mới là Foveros. Về bản chất, Foveros là cách để các die chip "nói chuyện" với nhau, tương tự kỹ thuật interposer mà AMD hoặc các khách hàng khác của TSMC đang sử dụng dựa trên các TSV (through-silicon-via). Thực chất chúng ta không rõ liệu Foveros có thực sự tốt hơn interposer không nhưng Intel tự hào cho biết khi hoạt động ở tần số 2 GHz, mỗi bit dữ liệu truyền qua Foveros chỉ tốn có 0.15 - 0.3 pJ (10^-12 Joule) năng lượng.

Và vì MTL là một thiết kế chiplet (tile), các thành phần chức năng sẽ không nằm trên cùng 1 die chip nữa mà được "chia hộ khẩu" ra thành 4 chuyên khu: die điện toán (compute), die đồ hoạ (graphics), die nhập xuất (IO) và die "tá lả" (SoC).

Có thể nói việc chuyển qua chiplet giống AMD tuy sẽ mang tiếng "copy" nhưng dù sao đây cũng là một bước đi đúng đắn cho Intel. Với từng die tách biệt thế này, mỗi chuyên khu của MTL có thể hoạt động độc lập không ảnh hưởng tới các chuyên khu còn lại và nhờ thế mà hiệu quả sử dụng điện sẽ cao hơn. Die điện toán có thể hoạt động ở công suất lớn còn die đồ hoạ và SoC có thể chủ động ngắt bớt điện đi. Thêm vào đó mỗi die dùng tiến trình bán dẫn riêng sẽ cho phép Intel lựa chọn tiến trình phù hợp nhất cho mỗi chuyên khu chứ không chỉ mỗi hiệu suất cao (HP) hoặc tiết kiệm điện (LP) như trước nữa.

Con chip Meteor Lake được cấu tạo 4 từ die riêng lẻ liên kết với nhau bằng công nghệ Foveros.

Về mặt chuyên môn, lần này chúng ta chỉ điểm qua những ý chính trong kiến trúc MTL. Vì Intel đặt rất nhiều tâm huyết vô "canh bạc" lần này, do vậy có rất nhiều thứ để nói và khuôn khổ bài viết này không kham được hết tất cả. Chúng ta sẽ có những bài chuyên sâu hơn vào từng thành phần con chip sau này.

Cấu trúc die điện toán của Meteor Lake

Trước hết khi nói tới die điện toán của MTL sẽ là 2 loại nhân P-core Redwood và E-core Crestmont. Hiện tại Intel không nói rõ chúng khác thế nào với các nhân Golden Cove (P) và Gracemont (E) trừ việc sẽ tốt hơn và có mức IPC cao hơn thế hệ cũ. Một chi tiết thú vị là dù MTL sẽ có NPU (nhân AI) riêng nằm trong die SoC, nhưng các nhân Crestmont (E) vẫn còn chứa các tập lệnh VNNI (Vector Neural Network Instructions) chuyên dụng cho AI, tương tự như nhân Gracemont (E) trước đó. Chi tiết này có thể thấy việc xử lý AI của Intel sẽ không hoàn toàn dựa vô NPU mà sẽ dàn trải trên nhiều thành phần.

Nhưng không chỉ trang bị nhân E trên mỗi die điện toán, với MTL, Intel còn "chừa chỗ" cho một đám E-core nằm riêng trên die SoC với tên gọi Low Power Island. Tuy cùng kiến trúc Crestmont song 2 đám E-core này có khác biệt - die điện toán dùng tiến trình Intel 4 còn die SoC dùng TSMC 6N. Về mặt lý thuyết TSMC 6N là tiến trình tiết kiệm điện còn Intel 4 là hiệu suất cao. Chưa rõ 2 đám nhân E sẽ hoạt động thế nào nhưng ta có thể đoán nhân E "ngoài đảo" sẽ có xung và mức hao điện thấp hơn nhân E "trong nhà".

Vị trí "đảo" E-core trên SoC và 3 chế độ làm việc của CPU Meteor Lake

Một vấn đề quan trọng khác khi áp dụng cùng lúc 2 kiến trúc khác nhau trên cùng die điện toán chính là làm sao để phân chia công việc? Bắt đầu từ thế hệ chip kiến trúc hiệu năng lai đầu tiên, Intel đã bổ sung thêm một thành phần chuyên môn có tên Thread Director (TD). Vai trò chính của TD là nhận các đầu việc mà hệ điều hành (OS) đưa xuống rồi "lựa cơm gắp mắm", giao việc đó cho nhân E hoặc P xử lý. Trên dòng chip cũ (Raptor Lake), cách TD làm việc sẽ là nhân P nhận trước các việc "nặng", rồi việc "nhẹ" chuyển qua nhân E, sau đó tuỳ tính chất phát sinh mà các nhân này sẽ hoán đổi công việc cho nhau (nhân E có thể "nghỉ việc" nếu không còn việc "nặng" để làm).

So sánh cách Thread Director làm việc trên Meteor Lake và thế hệ trước

Nhưng sang MTL, mọi thứ ngược lại. Trước tiên "người" nhận việc sẽ là các nhân E "ngoài đảo". Nếu các việc này không giải quyết được trên die SoC thì TD mới chuyển qua cho die điện toán phía sau. Tuy vậy, các nhân E "trong nhà" sẽ không được "ngồi chơi xơi nước" như thế hệ trước nữa mà phải "xắn tay vô làm". Trường hợp công việc quá nặng nhân E không kham nổi thì mới tới lượt nhân P "nhảy vào". Như vậy có thể thấy với MTL, Intel muốn đặt vấn đề hiệu quả tiêu thụ điện tới mức tối đa khi có tới 3 cấp độ (level) xử lý & tiêu thụ điện.

Thành thực mà nói, sức mạnh đồ hoạ của Intel trong bao nhiêu năm qua chưa hề được xem là mạnh. Mặc dù vài năm trở lại đây Intel đã có một đợt chuyển mình bằng cách dấn thân vô thị trường bằng dòng card đồ hoạ rời Arc, đó vẫn là một con đường gian nan và vất vả khi không chỉ các đối tác phần cứng (AIB) lẫn phần mềm (game developer) đều đã quá quen thuộc với AMD hoặc NVIDIA. Và liệu Intel có ra mắt sản phẩm đồ hoạ rời nào nữa không thì đó vẫn là một dấu hỏi lớn sau khi Gelsinger lên nắm quyền.

Tất nhiên nhân đồ hoạ trên MTL vẫn là đồ hoạ tích hợp chứ không phải đồ hoạ rời, nên chắc chắn là hiệu năng game của nó vẫn còn thấ, tuy nhiên không có nghĩa không có gì để cải thiện ở đây.

Nếu nói cho đúng, die SoC mới là die quan trọng nhất khi thiết kế MTL chứ không phải điện toán hay đồ hoạ. Trong quá trình phát triển chip, các kỹ sư Intel nhận ra việc xử lý các lệnh pipeline 3D thực chất khác hẳn việc xử lý media (phim ảnh), display (hiển thị màn hình)... Nhưng ở các thế hệ chip trước, các đơn vị media hay display đều nằm chung với các nhân đồ hoạ. Cách thiết kế này gây ra một sự lãng phí là kể cả khi nhân đồ hoạ không vận hành thì nó vẫn phải được "bật" để có điện cho các đơn vị media/display làm việc.

Các thành phần xử lý media và display đều tách khỏi GPU trên Meteor Lake

Vì thế khi chuyển qua MTL, các kỹ sư Intel đã "tách hộ khẩu" phần xử lý media/display từ die đồ hoạ sang die SoC. Bước đi này biến die SoC thành die thực hiện nhiều chức năng nhất con chip và nó cũng là die lớn nhất trong toàn bộ 4 die MTL.

Tuy không phải là die cho hiệu suất điện toán cao nhất, nhưng SoC lại là die nắm giữ nhiều vai trò nhất trên MTL. Ngoài "đảo" E-core để làm thay die điện toán hay các đơn vị media/display tiết kiệm điện thay cho die đồ hoạ, die SoC còn chứa cả nhân NPU dành cho AI, trình điều khiển bộ nhớ làm việc với RAM, cũng như cả thành phần thu phát sóng Wi-Fi lẫn Bluetooth cho toàn con chip.

SoC là nơi chứa nhiều thành phần nhất trên Meteor Lake

Hiện tại, câu chuyện về AI của Intel có khá nhiều thứ để bàn. Nhưng trong khuôn khổ bài này, chúng ta chỉ tóm gọn rằng AI của Intel sẽ không đơn thuần là một thành phần cố định. Kiến trúc AI của Intel được định đoạt nhiều bởi các API, trình biên dịch, thư viện phần mềm, driver, phần cứng. Vì vậy, bất kể là CPU, GPU hay NPU đều có thể chạy AI miễn là có hệ sinh thái ứng dụng dành cho chúng.

Riêng về NPU của Intel, nó được thiết kế để xử lý những ứng dụng AI được chuẩn hoá theo OpenVINO. Khối NPU này gồm 2 neural engine có cấu hình và giao diện tương tự các bộ DSP chủ yếu xử lý các dữ liệu điện toán dạng INT8 hoặc FP16. Intel cho biết các NPU có hiệu quả tiêu thụ điện gấp 8 lần song không nói rõ khi so sánh với cái gì, nhưng ta có thể đoán đó là khi xử lý AI trên CPU.

Không tự dưng mà Intel nói MTL là cuộc cách mạng kiến trúc lớn nhất của hãng trong 40 năm qua. Đó là vì MTL không chỉ thuần tuý là sự cải thiện hiệu năng so với thế hệ trước, mà nó còn là sự thay đổi cơ bản nhận thức về CPU nói riêng hoặc chip nói chung. Nếu như trước đây các cải thiện về kiến trúc chip chỉ tập trung vào CPU thì nay mọi thứ đã khác.

Vị trí và chức năng die IO trên Meteor Lake

Trong thế giới điện toán đa hình dạng như ngày nay, vai trò của CPU đã bớt đi ít nhiều. Thay vào đó chúng ta có GPU, có AI, có các đơn vị chức năng cố định như media encoder/decoder... Nhưng tất cả cùng có điểm chung là cần nhiều băng thông dữ liệu. Nếu cách thức chuyển giao dữ liệu không có gì thay đổi thì hiện tượng nghẽn cổ chai sẽ xảy ra thường xuyên, bất kể là CPU có mạnh tới cỡ nào.

Với rất nhiều thành phần mới, nhu cầu trao đổi dữ liệu tăng lên đáng kể

Vì thế mà trên MTL, die IO sẽ không làm việc trực tiếp với die CPU như các thế hệ trước. Thay vào đó, die SoC mới là "đạo diễn" chính. Thực tế là mọi lệnh nhập xuất (input output) dữ liệu đều được bộ phận IOC thực hiện và bộ phận này nằm trên die SoC. Dữ liệu sau khi được IOC nhận sẽ được đưa vào kênh Scalable Fabric. Từ đây, chúng có thể toả đi đến mọi nơi như "đảo" E-core, NPU, Media, CPU, GPU...

Die SoC đóng vai trò quan trọng trong việc trao đổi dữ liệu trên Meteor Lake

Nhìn chung, Scalable Fabric cũng gần tương tự như Infinity Fabric bên AMD, khi việc nhân xử lý ngày càng nhiều thì nhu cầu trao đổi dữ liệu cũng ngày một lớn. Việc làm ra một nhân xử lý đồ sộ nhưng không thể đáp ứng đủ dữ liệu cho nó cũng khiến cho kiến trúc bị "đói ăn" và không phát huy được hết sức mạnh của nó.

Có thể nói là còn quá sớm để biết được liệu MTL trên thực tế sẽ thế nào, có mỹ mãn như những lời có cánh của Intel hay không. Nhưng việc đổi ngôi CEO có tác động không nhỏ tới việc các sản phẩm của hãng này sẽ ra thế nào. Kể từ khi Gelsinger lên nắm quyền thay Krzanich, đại gia x86 đã có nhiều thay đổi cơ bản. Trong đó Intel dần cắt bớt những mảng kinh doanh mang tính... "linh tinh".

Có câu "bỏ trứng vào nhiều rổ", song khi không có cái rổ nào "đàng hoàng" thì điều cần làm là tập trung vào những sản phẩm cốt lõi của chính mình. Lẽ tất nhiên sẽ cần có thời gian để mọi thứ trở về quỹ đạo ban đầu của nó. Điều rõ ràng là Intel đã không còn đứng đầu về bán dẫn như bao năm trước, vậy nên để có thể theo kịp các đối thủ sẽ không phải chuyện trong một hai ngày. Sau một loạt các "Lake" (hay "Too Little Too Late"?) ngày càng nóng và tốn điện hơn, giờ có lẽ là lúc để một sản phẩm đáng được chờ đợi ra đời.

Trên thực tế, chẳng ai biết MTL có phải là con chip PC di động mạnh nhất khi ra mắt (vào giữa tháng 12 này), nhưng những thay đổi mà Intel đặt ra, ít nhất về mặt tầm nhìn vi xử lý, cho thấy hãng này đã "bắt kịp" xu thế với những công ty công nghệ khác. Với việc đặt trọng tâm con chip nằm ở die SoC thay cho CPU, nó cho thấy Intel đã thực sự "thức tỉnh" và khi người khổng lồ tỉnh giấc thì sẽ có rất nhiều điều xảy ra...

Biết là Ecore yếu, nhưng mà con CPU có 32 Ecore thì cũng rất ra gì và này nọ 😃

Chứ mấy con CPU ba rọi 8 nạc 16 mỡ như hiện nay thì mình xin kiếu, vì làm server thì không cần Pcore, còn chơi game thì cứ con Ryzen 5800x3d hoặc 7800x3d mà táng.

Cải tiến nhất là GPU Arc đi kèm, còn hiệu năng này nọ ko ăn thua gì.

Vẫn chạy sau AMD khá nhiều. Mà là AMD đời trước, sang năm dòng AMD 8000 ra mắt nó lại vả cho sấp mặt.

Tương tự honda hay toyota bên xe cộ