Planar MOSFET chính là MOSFET nhưng ở hình thái cơ bản nhất (dạng phẳng 2D - planar). Nó là hình dạng chung của hầu hết MOSFET được sản xuất trên các tiến trình bán dẫn trước 14 nm. Tên gọi planar chỉ bắt đầu sau khi các nhà sản xuất bán dẫn nghĩ tới một loại MOSFET có cấu trúc không phải... planar (kiểu như không ai cần gọi chi tiết là Exciter 135 cc nếu Exciter 150/155 cc chưa ra đời). Cấu trúc của planar thì chúng ta đã nêu ở bài viết lần trước (anh em coi ở ngay bên dưới) nên không cần nhắc lại nữa.

Nhưng trước khi đi sâu vào FinFET và GAAFET, anh em cần hiểu tại sao các NSX bán dẫn lại cần tới chúng. Lý do vì đâu mà planar MOSFET đã "nuôi sống" cả ngành công nghiệp suốt hàng chục năm nhưng giờ họ lại chuyển sang thứ khác?

Hãy quay lại với nguồn gốc của MOSFET - chúng chính là các FET hay transistor hiệu ứng trường. Do yêu cầu của ngành bán dẫn, kích thước các transistor ngày càng nhỏ đi theo thời gian. Điều này dĩ nhiên dẫn tới các thành phần của transistor (gate, source/drain, channel) cũng phải "teo nhỏ" theo. Hệ quả tương ứng là hiệu ứng trường do gate sinh ra cũng bị giảm theo (cả về cường độ lẫn bán kính tác dụng). Khi hiệu ứng trường không còn đủ mạnh thì tác dụng làm thay đổi thuộc tính dẫn điện/ngắt điện của channel lân cận đó không còn được đảm bảo - tương đương với chức năng của transistor không còn đáng tin cậy.

Thêm vào đó, các transistor planar còn gặp thêm tình trạng ngắn-mạch (short circuit) nếu NSX tìm cách tăng hiệu ứng trường bằng cách tăng điện thế hoặc cường độ dòng điện trong mạch, nhất là hiện tượng chui hầm lượng tử (quantum channel). Những yếu tố này khiến cho việc thu nhỏ transistor planar ngày càng trở nên vô nghĩa.

Video so sánh MOSFET planar, FinFET và GAAFET.

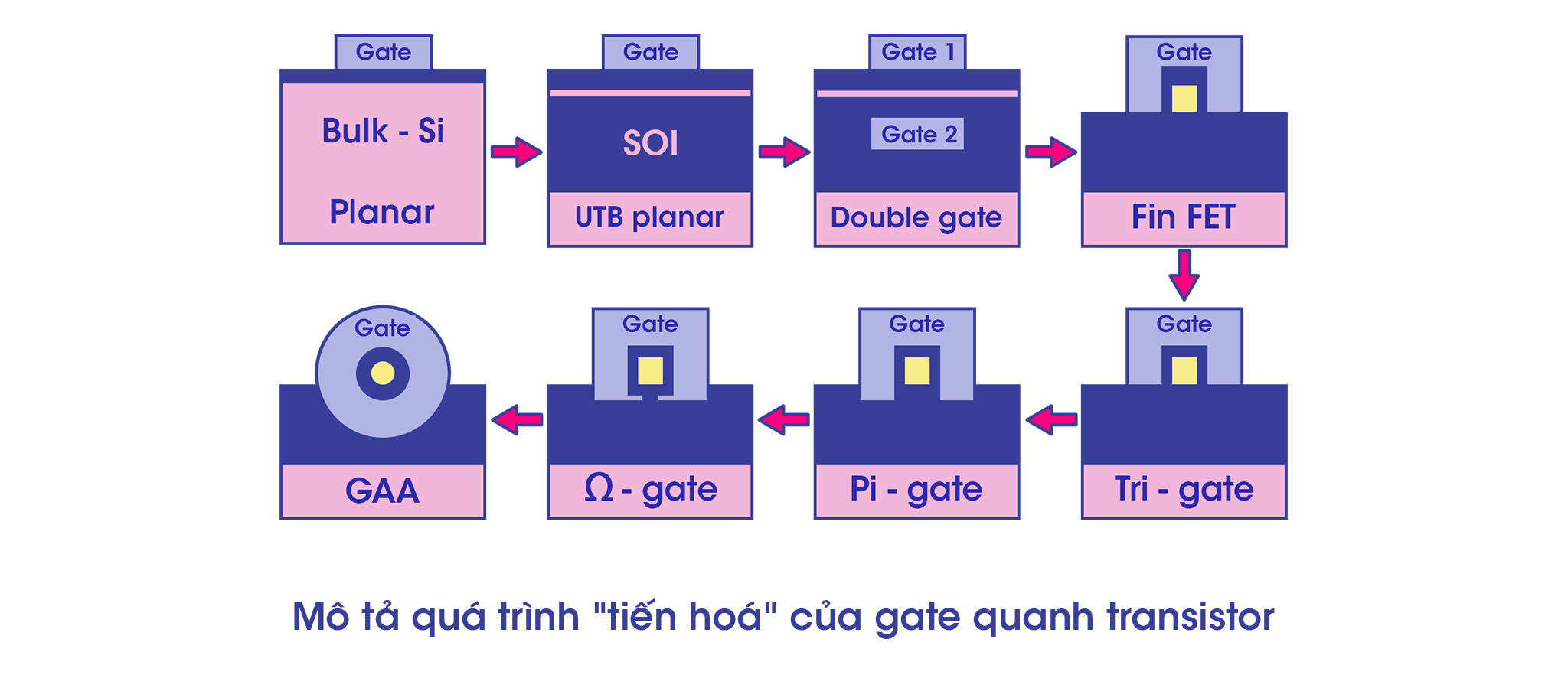

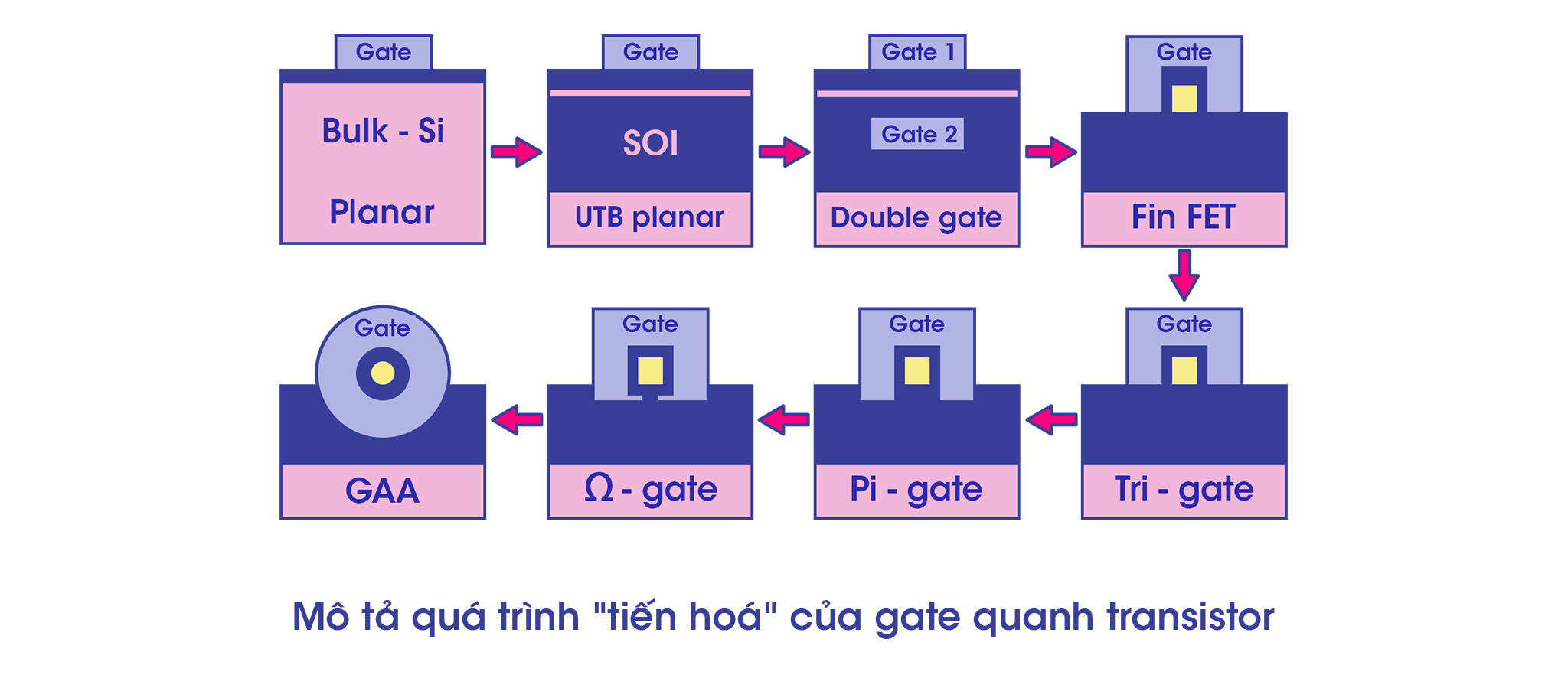

Để khắc phục những vấn đề trên, một số giải pháp được đưa ra. Ví như planar double-gate MOSFET khi có thêm một gate nằm ở phía đối diện. Ý tưởng này tuy hay khi gấp đôi được hiệu ứng trường nhưng lại khó cho sản xuất vì cần ghép chồng 2 wafer lên nhau và nằm sao để "canh chuẩn" cho 2 gate (kích thước vài chục nm) nằm đối xứng nhau là cực kỳ khó.

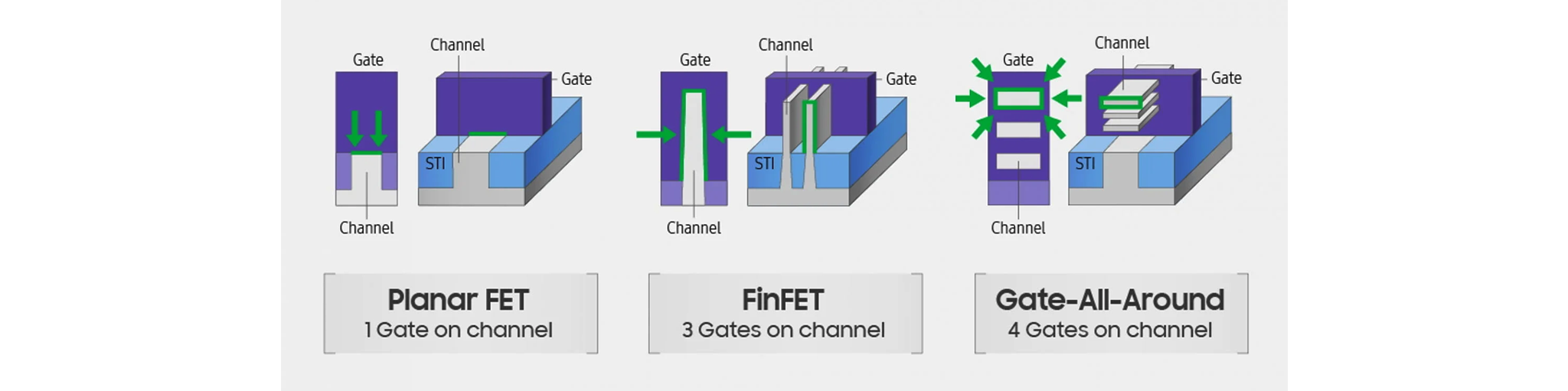

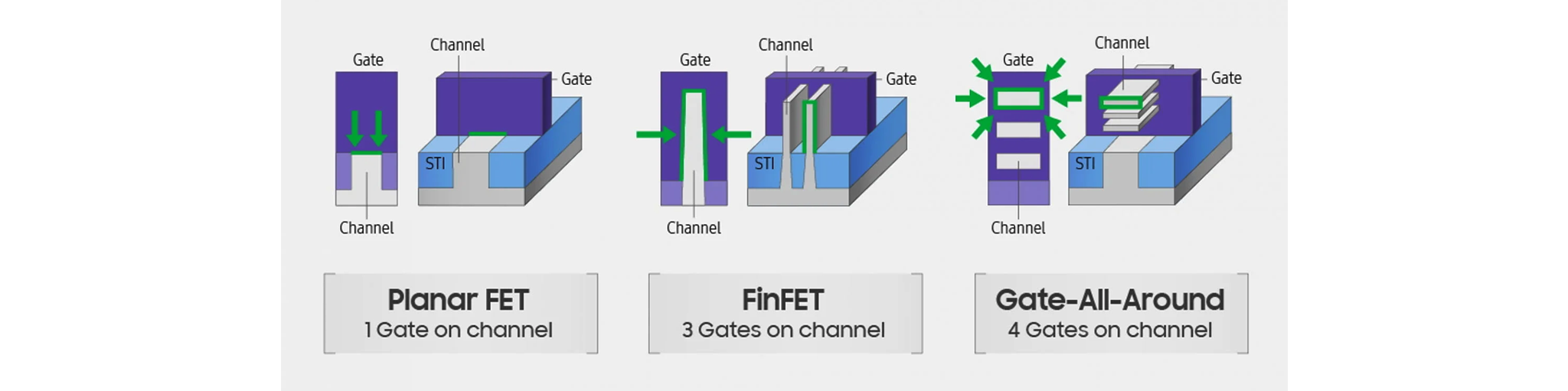

Nếu như đặt 2 gate ở "trên & dưới" channel khó quá, sao ta không đặt chúng ở bên "trái & phải"? Thế là FinFET ra đời! Thay cho việc gate "nằm đè" lên source/channel/drain như trước, nay bộ 3 này sẽ "đâm ngang" qua gate. Vì đặc trưng hình thái source/channel/drain lúc này mỏng như cái "vảy cá" (fin) nên từ đó chúng ta có cái tên FinFET (FET hình vảy). Một biến thể khác của FinFET là Tri-Gate trong đó bản thân transistor có nhiều fin hơn bình thường, mục đích cũng là để tăng hiệu quả của hiệu ứng trường hơn nữa.

Dĩ nhiên, nếu đã có thể bao bọc cả 3 phía source/channel/drain thì sao không làm triệt để hơn? Thế là chúng ta có thêm những kiểu gate mới như Pi-gate (hình chữ Pi), Omega-gate (hình chữ Omega) và Gate-all-around FET (gate bọc toàn bộ channel). Trong đó, GAAFET (nanowire hoặc nanosheet hoặc RibbonFET hoặc MBCFET) là loại cho hiệu ứng trường mạnh hơn tất cả. Một chi tiết có thể nêu thêm là GAAFET được đề xuất trước cả FinFET, nhưng nó chưa được đưa vô khai thác cho tới tận lúc này. Lý do là gì?

Có một thực tế là các thiết kế transistor đa gate đều không mới. Chúng đều đã được phát triển từ những năm cuối thập niên 80 hoặc đầu thập niên 90 của thế kỷ trước. Nhưng mãi tận vài chục năm sau chúng mới được đưa vào thương mại hoá. Là tại làm sao?

Trên lý thuyết, mọi hình thái transistor đều có thể sản xuất được ở bất kỳ tiến trình nào, dù là 180 nm hay 45 nm hay 14 nm hay 7 nm. Vấn đề nằm ở chỗ có những hình thái "dễ" và "khó" tạo ra hơn. Quay lại phần chế tạo transistor, có thể thấy về cơ bản, làm ra transistor cũng gần giống với xây nhà - trước hết là đóng cọc, làm móng, làm hầm, làm nền... rồi tới xây tường, đổ tấm, làm mái... Căn nhà càng phức tạp thì việc xây dựng sẽ lâu và mất nhiều thời gian, công đoạn hơn. Transistor cũng thế.

Nếu ở dạng planar phần source/channel/drain nằm hoàn toàn phía dưới gate thì sang FinFET, chúng "đứng" lên đâm xuyên qua gate. Riêng yếu tố này đã khiến cho quá trình cấy ion & ăn mòn vi mạch khác biệt đi thấy rõ. Tới GAAFET, sự phức tạp càng nhiều hơn nữa với phần sheet (source/channel/drain) chìm hẳn bên trong gate. Và không chỉ có 1 sheet mà là nhiều sheet nằm song song nhưng lại xen kẽ với gate. Có nghĩa NSX cứ phải hoàn thiện xong 1 sheet rồi họ phải làm thêm một lớp gate rồi lại làm tiếp 1 sheet mới. Nó gần tương tự như việc chúng ta xây một căn nhà cao tầng nhưng mỗi tầng phải hoàn thiện xong toàn bộ điện nước nội thất... rồi mới có thể đổ tấm để làm tới tầng kế tiếp. Không chỉ thế, bản thân từng sheet (kích thước chỉ vài ~ vài chục nm) cũng phải nằm chồng lên nhau, đặt ra yêu cầu chính xác tuyệt đối trên quy mô hàng triệu ~ hàng tỷ transistor đơn lẻ.

Video mô tả quá trình làm transistor FinFET, có thể thấy xuất hiện thêm nhiều công đoạn hơn so với video trước đó.

Với các đặc trưng trên, không khó để nhận ra nếu "nhu cầu" chưa thực sự cần thiết, các NSX bán dẫn sẽ không áp dụng ngay các thiết kế transistor có hình thái phức tạp trừ phi không còn lựa chọn nào khác. Lấy ví dụ Intel đưa vào áp dụng FinFET từ tiến trình 22 nm trở xuống nhưng TSMC và các hãng khác chỉ bắt đầu áp dụng FinFET từ 14/16 nm. Lý do chủ yếu vì các chip của Intel thường có xung nhịp rất cao (trên 3 GHz) nhưng các khách hàng của TSMC thường không cao đến vậy nên vẫn có thể sử dụng thiết kế planar.

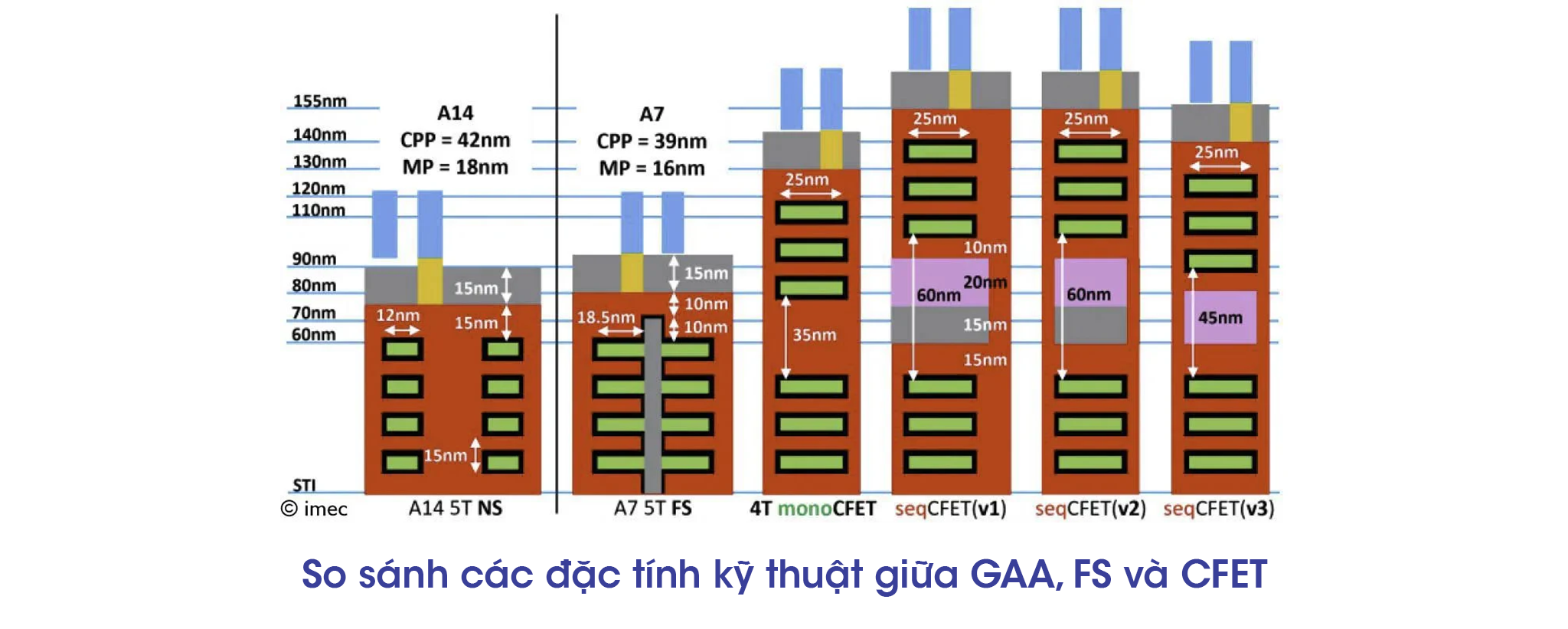

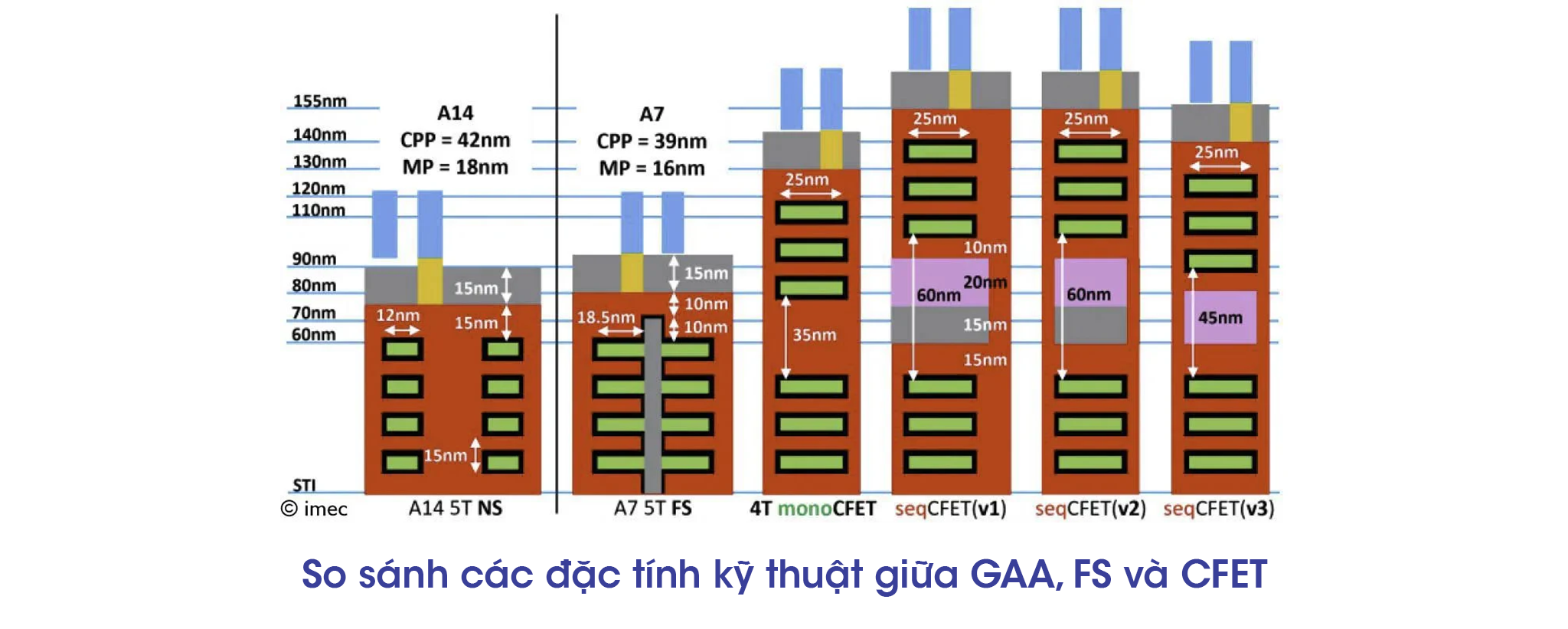

Đối với GAAFET, Samsung là hãng đầu tiên áp dụng từ tiến trình 3 nm (3GAP, 2023). TSMC với quan điểm của mình, chỉ triển khai GAAFET từ 2 nm trở đi (N2, 2024). Còn Intel cho biết sẽ áp dụng ngay ở node Intel 20A. Tất nhiên, con số nm hiện nay chỉ còn mang tính "tham khảo" (marketing) vì chúng chỉ có ý nghĩa trên thiết kế planar. Kể từ thiết kế FinFET thì nm chỉ còn ý biểu trưng cho một node có mật độ transistor cao/thấp hơn các tiến trình khác. Tương tự khi sang GAAFET, để biết tiến trình của hãng nào "tốt hơn" chúng ta cần xem chi tiết "cấu hình" từng bên chứ không dựa vô con số marketing được. 2024 sẽ là một năm rất thú vị cho ngành bán dẫn.

GAAFET dù tốt hơn bao nhiêu thì nó cũng sẽ rơi vào tình trạng như FinFET lẫn planar đã từng - không thể thu nhỏ mãi mà không gặp vấn đề. Vì thế từ trước khi GAAFET được đưa vô khai thác, các NSX đã bắt tay vô tìm kiếm các giải pháp có thể thay thế để làm ra những con chip tốt hơn.

GAAFET dù tốt hơn bao nhiêu thì nó cũng sẽ rơi vào tình trạng như FinFET lẫn planar đã từng - không thể thu nhỏ mãi mà không gặp vấn đề. Vì thế từ trước khi GAAFET được đưa vô khai thác, các NSX đã bắt tay vô tìm kiếm các giải pháp có thể thay thế để làm ra những con chip tốt hơn.

Tới đây, chúng ta không thực sự chắc chắn đâu sẽ là con đường để đi tiếp. Nhưng về căn bản, có 2 hướng có thể kể đến là (1) thay đổi hình thái transistor giống như quá khứ đã làm, (2) tìm kiếm loại vật liệu mới có các tính chất tốt hơn các vật liệu đang sử dụng.

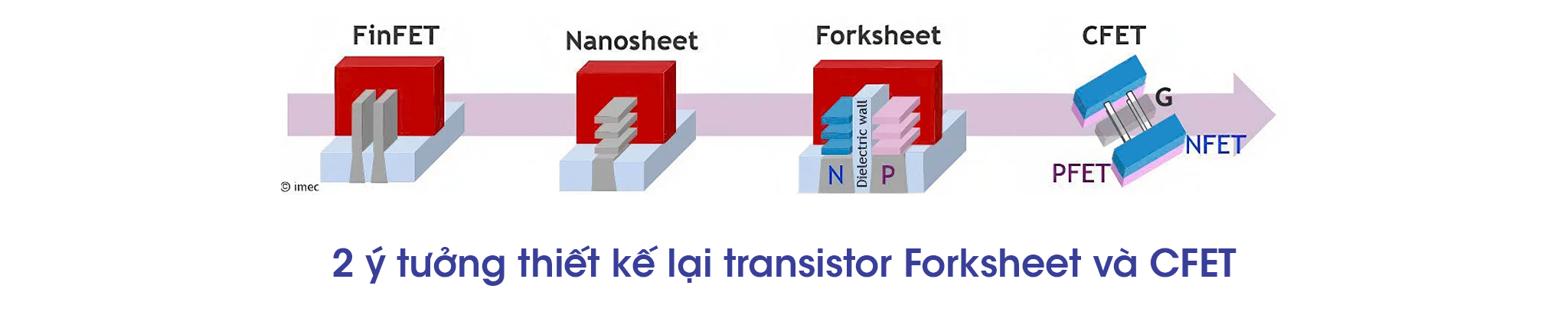

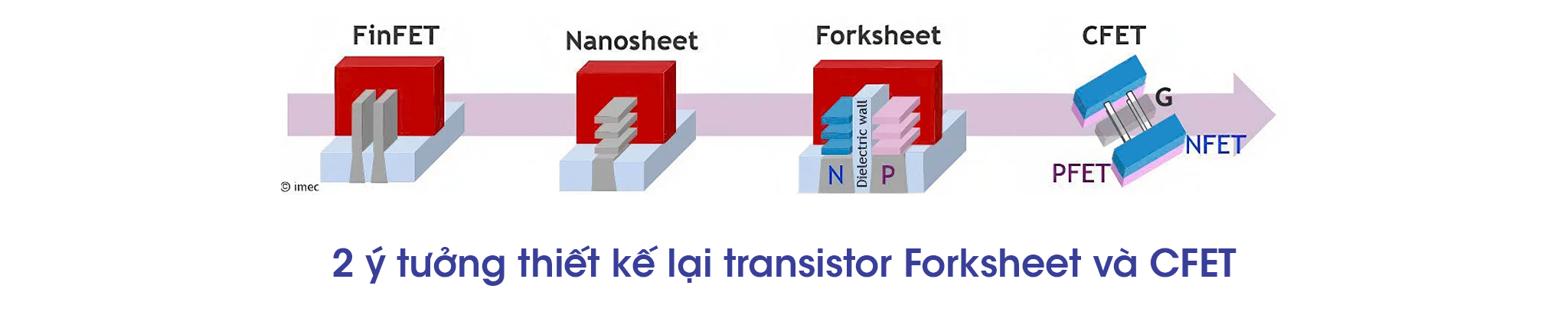

Với hướng đầu tiên, hiện nay đang có 2 đề xuất đến từ hãng IMEC (một công ty chuyên bán dẫn). 1 là thiết kế Forksheet (FS) và 1 là CFET (complementary FET). Cả 2 đề xuất này cùng dựa trên ý tưởng kết hợp transistor loại N và P lại làm một. Thực tế hiện nay transistor N và P vẫn được sản xuất độc lập, có nghĩa 1 tổ hợp N-P sẽ cần tới 2 transistor độc lập đứng kề nhau. Nếu có thể ghép cả 2 lại làm 1 transistor thì không gian chiếm dụng sẽ giảm đi đáng kể. Tất nhiên, điểm trừ của thiết kế này là không phải lúc nào hãng chip cũng cần tới 1 transistor tổ hợp như trên. Và chúng ta cũng chưa rõ liệu hiệu suất làm việc của transistor này có hiệu quả bằng 2 transistor độc lập hay không. Vì thế FS hay CFET có được áp dụng vô thực tiễn hay không vẫn là câu hỏi còn bỏ ngỏ.

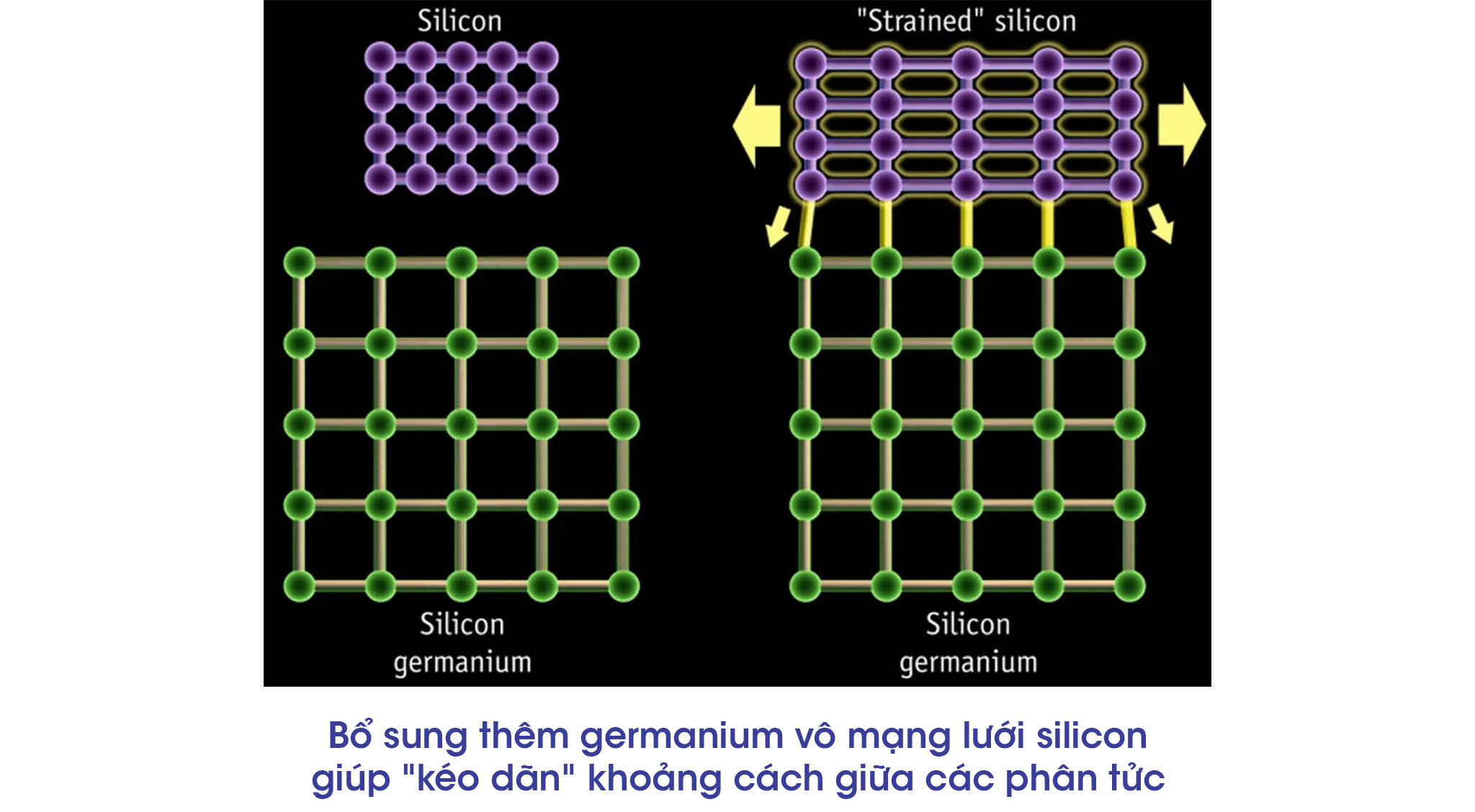

Với hướng thứ hai, thực tế các NSX đã từng áp dụng cách này trong quá khứ. Cụ thể như strained silicon (dùng mạng lưới tinh thể germanium để "kéo dãn" các nguyên tử silicon - do Ge có chung hoá trị 4 như Si) giúp electron di chuyển dễ dàng hơn. Hoặc vật liệu cách điện High-K để thay thế silicon dioxide (SiO2) do năng lực cách điện của SiO2 suy giảm mạnh khi bề dày của lớp này mỏng đi (dẫn tới sự rò rỉ điện áp từ gate sang channel làm tăng công suất tiêu thụ điện). Hoặc SOI (silicon on insulator) khi tạo thêm 1 lớp SiO2 nằm bên dưới source/channel/drain nhằm giảm bớt điện dung ký sinh của transistor, góp phần tăng hiệu suất làm việc.

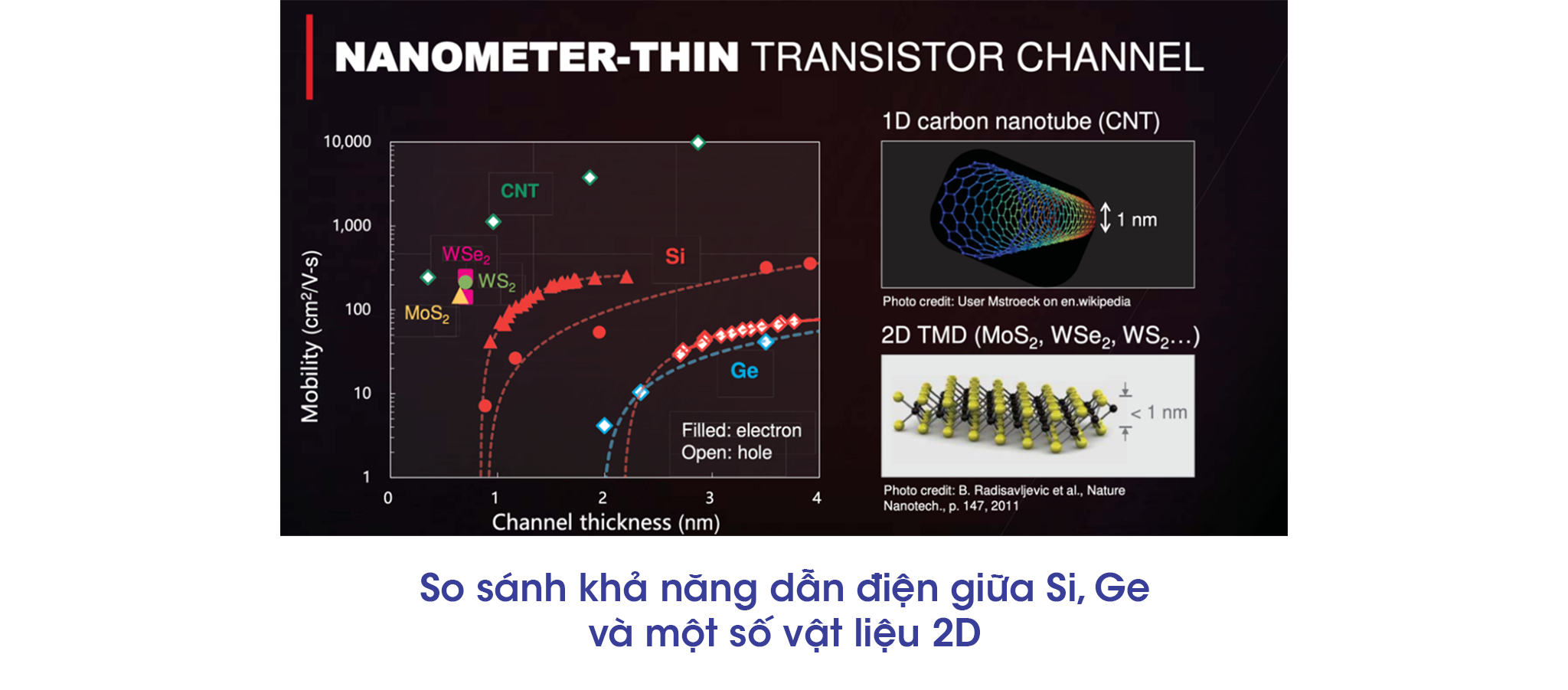

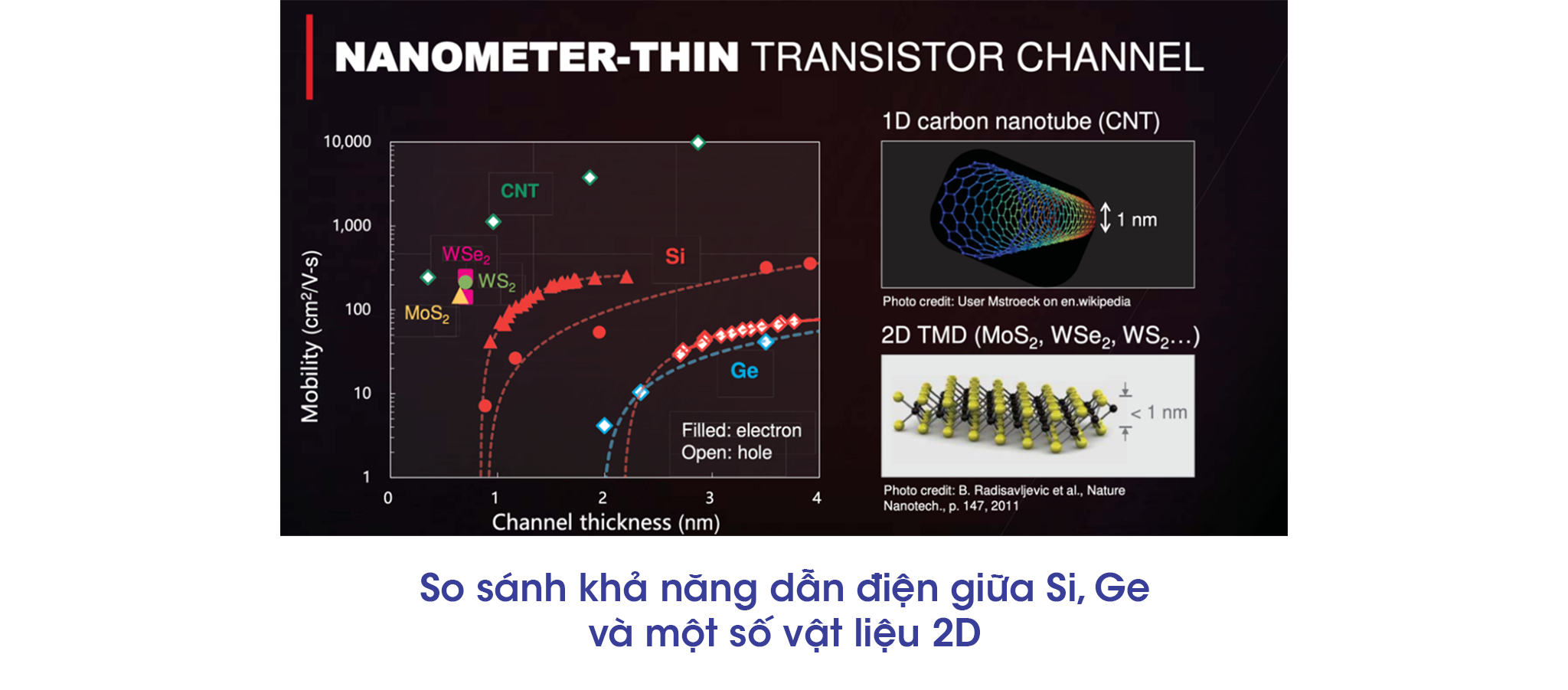

Quay lại câu chuyện "hậu GAAFET", những bàn luận chính về vật liệu chủ yếu nằm ở source/channel/drain sẽ được sản xuất từ nguyên tố gì. Hiện tại chúng ta đang có Si tinh thể (poly Si) và Si "kéo dãn" (SiGe). Nhưng khi độ dày các vật liệu này trở nên quá mỏng, thì khả năng di chuyển của dòng electron trong chúng sẽ bị tụt đi đáng kể, bất kể hiệu ứng trường do gate tạo ra mạnh đến mức nào (tưởng tượng 1 ngõ hẻm < 1 mét thì kể cả xe 2 bánh cũng không chạy qua suôn sẻ được). Tại sự kiện IEDM thứ 68 diễn ra vào năm ngoái, các nhà nghiên cứu khắp thế giới đã cùng chia sẻ một vài ý tưởng về các vật liệu có thể thay thế Si. Chúng có tên gọi chung là vật liệu 2D (ám chỉ bề dày chỉ có 1 lớp phân tử).

Những cái tên 2D có thể kể ra như graphene (lưới carbon dạng tổ ong), Molybdenum Disulfide (MoS2), Tungsten Disulfide (WS2), Tungsten Diselenide (WSe2)... Carbon Nanotube (CNT) tuy không phải là 2D nhưng cũng được nêu ra vì có thuộc tính điện lý phù hợp để làm bán dẫn (đường kính tối thiểu 1 nm). Hầu hết các vật liệu trên cho phép dòng electron chảy qua mạng tinh thể tốt hơn ngay cả khi độ dày < 1 nm (Ge "chào thua" ở 2 nm và Si ở 1 nm).

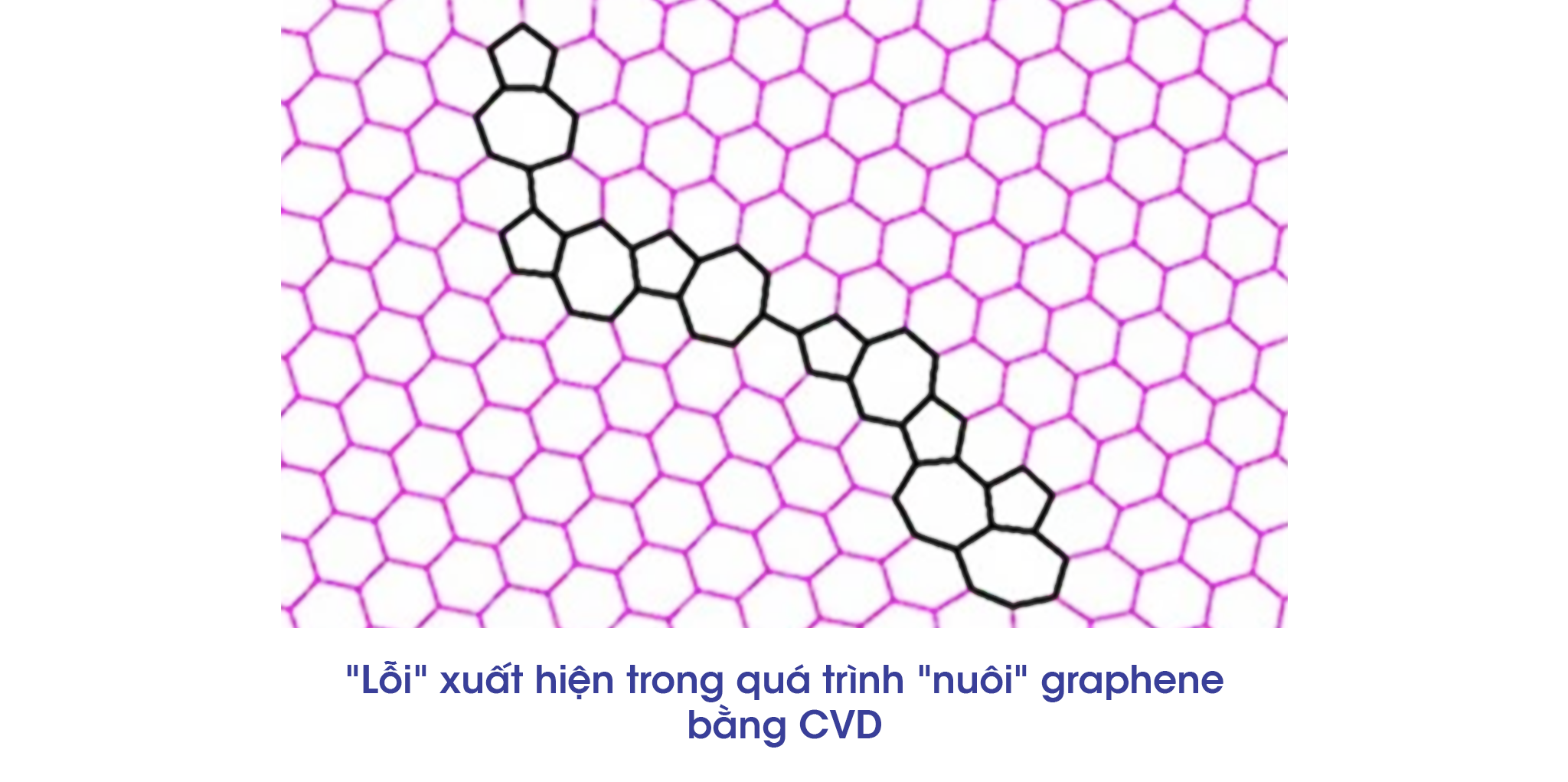

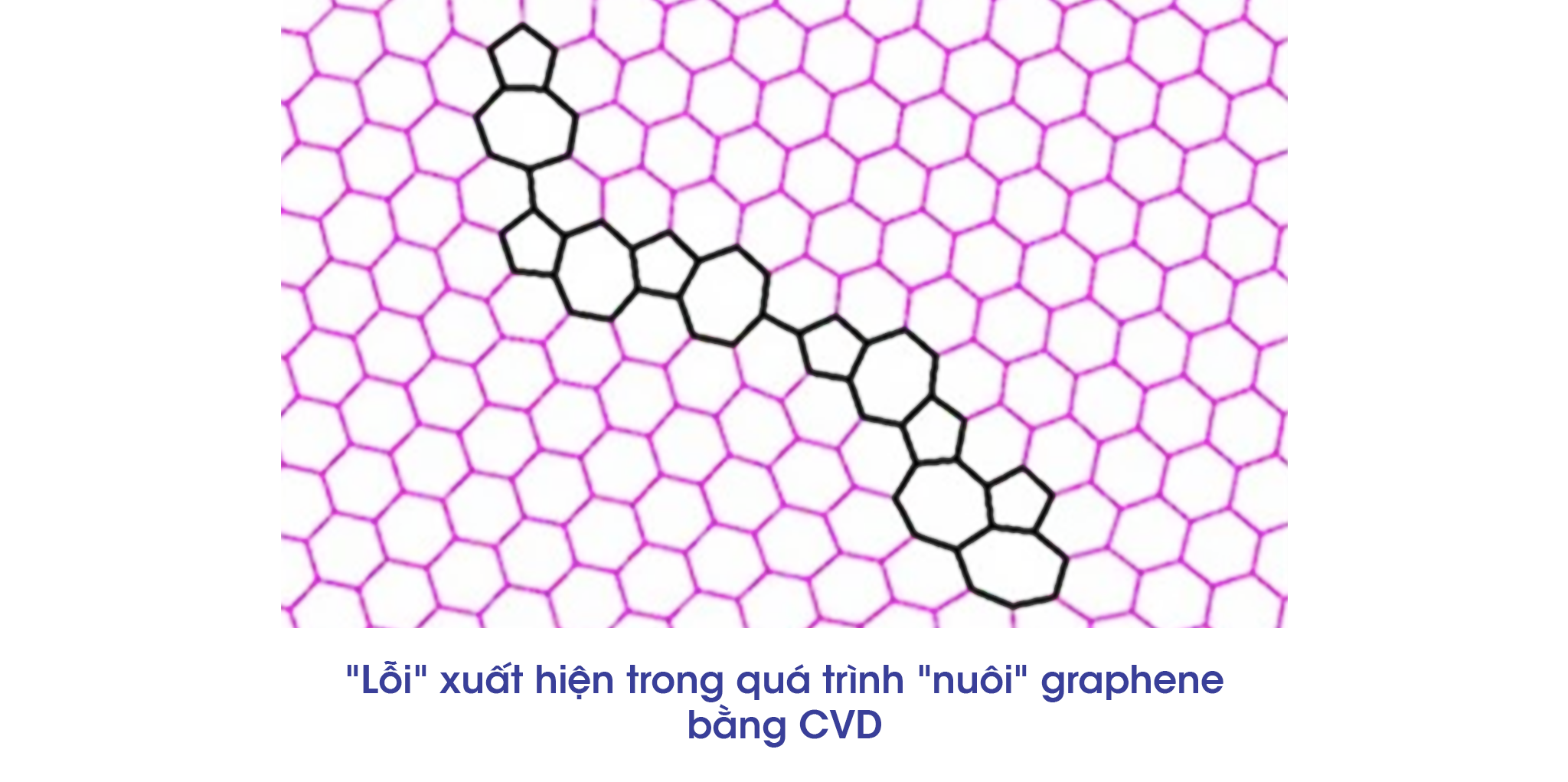

Mặc dù "hấp dẫn" là thế, quá trình sản xuất/tích hợp vật liệu 2D lên các wafer Si hoàn toàn không đơn giản. Ở các tiến trình MOSFET kể trên, bề dày của một lớp vật liệu vẫn có ít nhất hàng trăm - hàng ngàn phân tử (1 nguyên tử Si có đường kính chỉ 0.2 nm). Tạo ra một lớp vật liệu chỉ dày vài lớp phân tử là cực kỳ khó. Thêm vào đó, rủi ro xuất hiện lỗi trên mạng tinh thể là cực lớn. Ví dụ như graphene là vật liệu 2D "trưởng thành" nhất hiện nay vẫn gặp phải tình trạng "sạn" (grain) (các vòng carbon không phải 6 cạnh) khi sản xuất bằng phương pháp Kết tủa Bay hơi Hoá Chất (CVD). Gần đây có một phương pháp mới tên gọi Kết tủa Lớp Nguyên tử (ALD) nhưng vì quá mới nên chúng ta chưa có nhiều dữ liệu để so sánh.

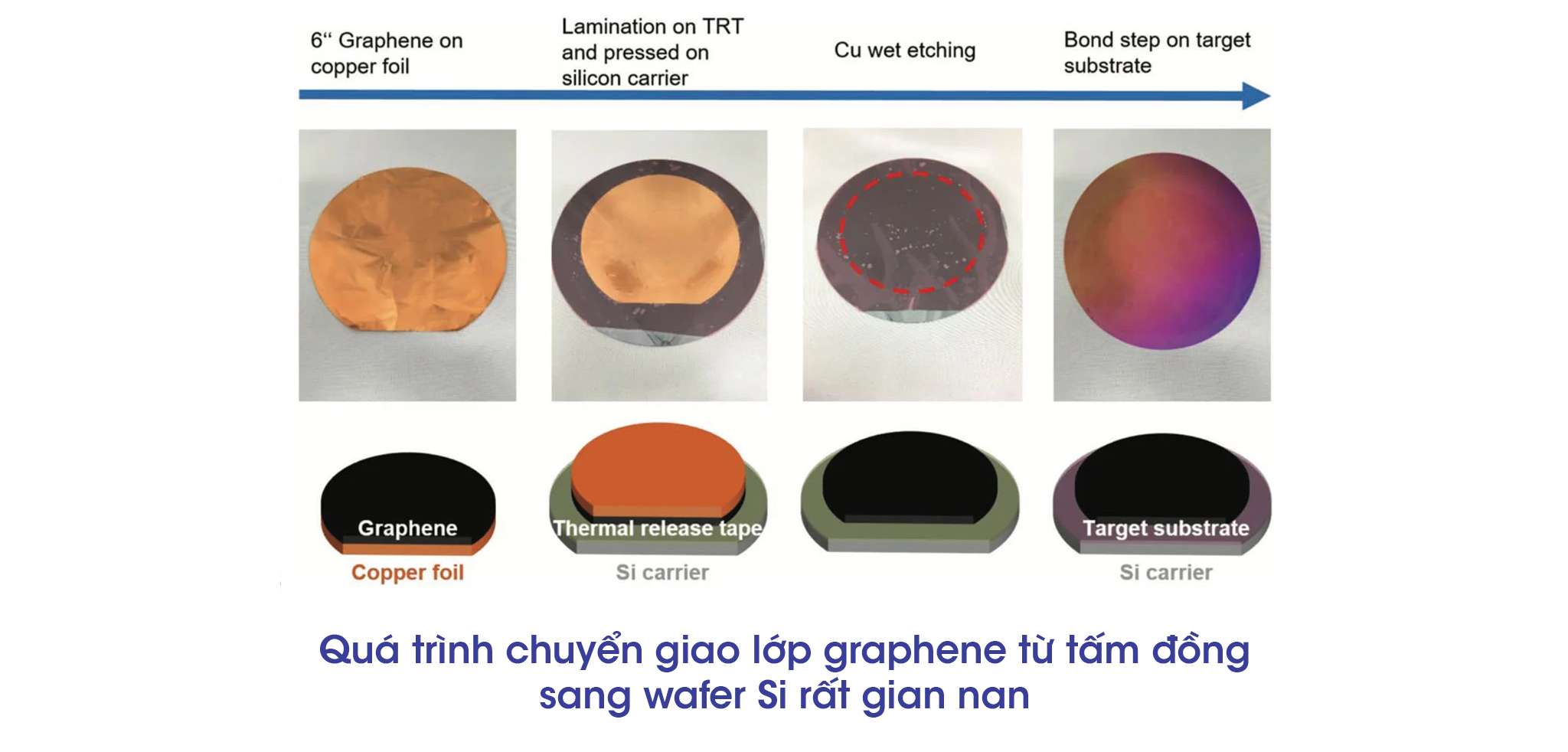

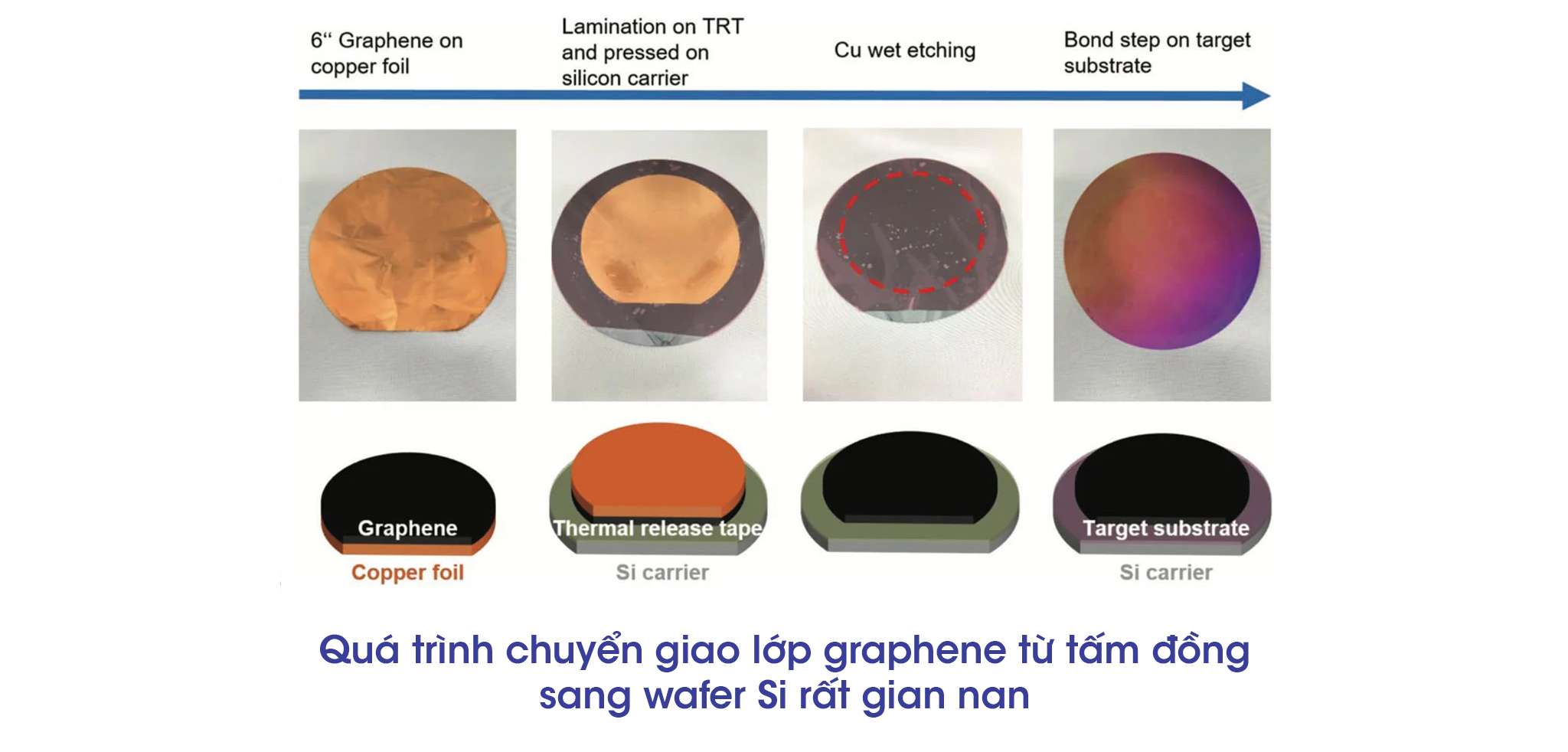

Một trong các khó khăn khác khi sản xuất vật liệu 2D là chúng thường được tạo ra trong môi trường nhiệt độ cực cao (> 600 °C) trên các tấm đồng hoặc sapphire chứ không làm trực tiếp trên wafer Si. Do đó sẽ phát sinh thêm vấn đề làm sao chuyển giao lớp phân tử 2D "mong manh" trên sang tấm Si được hoàn chỉnh.

Nhìn chung, những con đường mới vẫn còn khá "rậm rạp, chông gai và đầy thách thức". Một số có thể sẽ không bao giờ "thành đường". Song có thể nói rằng các transistor sẽ còn tiếp tục nhỏ hơn, hay đúng hơn, các con chip sẽ có thêm nhiều transistor hơn trước trong nhiều năm nữa. Và chúng ta sẽ có nhiều sản phẩm mạnh mẽ hơn nữa. Vấn đề chỉ còn lại - chi phí sản xuất chip có tăng lên nhiều hay không khi công nghệ làm ra chúng ngày càng phức tạp hơn?

Người ta chế tạo chip bán dẫn - transistor - như thế nào?

Mấy ngày nghỉ Tết âm lịch 2024 mình vẫn làm việc với máy tính, chợt nghĩ ra là những món đồ công nghệ hiện tại mà chúng ta đang sử dụng, đa phần đều có liên quan đến bán dẫn. Transistor là thành phần hay có thể coi là đơn vị cơ bản hình thành nên…

tinhte.vn

Nhưng trước khi đi sâu vào FinFET và GAAFET, anh em cần hiểu tại sao các NSX bán dẫn lại cần tới chúng. Lý do vì đâu mà planar MOSFET đã "nuôi sống" cả ngành công nghiệp suốt hàng chục năm nhưng giờ họ lại chuyển sang thứ khác?

Hãy quay lại với nguồn gốc của MOSFET - chúng chính là các FET hay transistor hiệu ứng trường. Do yêu cầu của ngành bán dẫn, kích thước các transistor ngày càng nhỏ đi theo thời gian. Điều này dĩ nhiên dẫn tới các thành phần của transistor (gate, source/drain, channel) cũng phải "teo nhỏ" theo. Hệ quả tương ứng là hiệu ứng trường do gate sinh ra cũng bị giảm theo (cả về cường độ lẫn bán kính tác dụng). Khi hiệu ứng trường không còn đủ mạnh thì tác dụng làm thay đổi thuộc tính dẫn điện/ngắt điện của channel lân cận đó không còn được đảm bảo - tương đương với chức năng của transistor không còn đáng tin cậy.

Thêm vào đó, các transistor planar còn gặp thêm tình trạng ngắn-mạch (short circuit) nếu NSX tìm cách tăng hiệu ứng trường bằng cách tăng điện thế hoặc cường độ dòng điện trong mạch, nhất là hiện tượng chui hầm lượng tử (quantum channel). Những yếu tố này khiến cho việc thu nhỏ transistor planar ngày càng trở nên vô nghĩa.

Để khắc phục những vấn đề trên, một số giải pháp được đưa ra. Ví như planar double-gate MOSFET khi có thêm một gate nằm ở phía đối diện. Ý tưởng này tuy hay khi gấp đôi được hiệu ứng trường nhưng lại khó cho sản xuất vì cần ghép chồng 2 wafer lên nhau và nằm sao để "canh chuẩn" cho 2 gate (kích thước vài chục nm) nằm đối xứng nhau là cực kỳ khó.

Nếu như đặt 2 gate ở "trên & dưới" channel khó quá, sao ta không đặt chúng ở bên "trái & phải"? Thế là FinFET ra đời! Thay cho việc gate "nằm đè" lên source/channel/drain như trước, nay bộ 3 này sẽ "đâm ngang" qua gate. Vì đặc trưng hình thái source/channel/drain lúc này mỏng như cái "vảy cá" (fin) nên từ đó chúng ta có cái tên FinFET (FET hình vảy). Một biến thể khác của FinFET là Tri-Gate trong đó bản thân transistor có nhiều fin hơn bình thường, mục đích cũng là để tăng hiệu quả của hiệu ứng trường hơn nữa.

Dĩ nhiên, nếu đã có thể bao bọc cả 3 phía source/channel/drain thì sao không làm triệt để hơn? Thế là chúng ta có thêm những kiểu gate mới như Pi-gate (hình chữ Pi), Omega-gate (hình chữ Omega) và Gate-all-around FET (gate bọc toàn bộ channel). Trong đó, GAAFET (nanowire hoặc nanosheet hoặc RibbonFET hoặc MBCFET) là loại cho hiệu ứng trường mạnh hơn tất cả. Một chi tiết có thể nêu thêm là GAAFET được đề xuất trước cả FinFET, nhưng nó chưa được đưa vô khai thác cho tới tận lúc này. Lý do là gì?

Có một thực tế là các thiết kế transistor đa gate đều không mới. Chúng đều đã được phát triển từ những năm cuối thập niên 80 hoặc đầu thập niên 90 của thế kỷ trước. Nhưng mãi tận vài chục năm sau chúng mới được đưa vào thương mại hoá. Là tại làm sao?

Trên lý thuyết, mọi hình thái transistor đều có thể sản xuất được ở bất kỳ tiến trình nào, dù là 180 nm hay 45 nm hay 14 nm hay 7 nm. Vấn đề nằm ở chỗ có những hình thái "dễ" và "khó" tạo ra hơn. Quay lại phần chế tạo transistor, có thể thấy về cơ bản, làm ra transistor cũng gần giống với xây nhà - trước hết là đóng cọc, làm móng, làm hầm, làm nền... rồi tới xây tường, đổ tấm, làm mái... Căn nhà càng phức tạp thì việc xây dựng sẽ lâu và mất nhiều thời gian, công đoạn hơn. Transistor cũng thế.

Nếu ở dạng planar phần source/channel/drain nằm hoàn toàn phía dưới gate thì sang FinFET, chúng "đứng" lên đâm xuyên qua gate. Riêng yếu tố này đã khiến cho quá trình cấy ion & ăn mòn vi mạch khác biệt đi thấy rõ. Tới GAAFET, sự phức tạp càng nhiều hơn nữa với phần sheet (source/channel/drain) chìm hẳn bên trong gate. Và không chỉ có 1 sheet mà là nhiều sheet nằm song song nhưng lại xen kẽ với gate. Có nghĩa NSX cứ phải hoàn thiện xong 1 sheet rồi họ phải làm thêm một lớp gate rồi lại làm tiếp 1 sheet mới. Nó gần tương tự như việc chúng ta xây một căn nhà cao tầng nhưng mỗi tầng phải hoàn thiện xong toàn bộ điện nước nội thất... rồi mới có thể đổ tấm để làm tới tầng kế tiếp. Không chỉ thế, bản thân từng sheet (kích thước chỉ vài ~ vài chục nm) cũng phải nằm chồng lên nhau, đặt ra yêu cầu chính xác tuyệt đối trên quy mô hàng triệu ~ hàng tỷ transistor đơn lẻ.

Với các đặc trưng trên, không khó để nhận ra nếu "nhu cầu" chưa thực sự cần thiết, các NSX bán dẫn sẽ không áp dụng ngay các thiết kế transistor có hình thái phức tạp trừ phi không còn lựa chọn nào khác. Lấy ví dụ Intel đưa vào áp dụng FinFET từ tiến trình 22 nm trở xuống nhưng TSMC và các hãng khác chỉ bắt đầu áp dụng FinFET từ 14/16 nm. Lý do chủ yếu vì các chip của Intel thường có xung nhịp rất cao (trên 3 GHz) nhưng các khách hàng của TSMC thường không cao đến vậy nên vẫn có thể sử dụng thiết kế planar.

Đối với GAAFET, Samsung là hãng đầu tiên áp dụng từ tiến trình 3 nm (3GAP, 2023). TSMC với quan điểm của mình, chỉ triển khai GAAFET từ 2 nm trở đi (N2, 2024). Còn Intel cho biết sẽ áp dụng ngay ở node Intel 20A. Tất nhiên, con số nm hiện nay chỉ còn mang tính "tham khảo" (marketing) vì chúng chỉ có ý nghĩa trên thiết kế planar. Kể từ thiết kế FinFET thì nm chỉ còn ý biểu trưng cho một node có mật độ transistor cao/thấp hơn các tiến trình khác. Tương tự khi sang GAAFET, để biết tiến trình của hãng nào "tốt hơn" chúng ta cần xem chi tiết "cấu hình" từng bên chứ không dựa vô con số marketing được. 2024 sẽ là một năm rất thú vị cho ngành bán dẫn.

GAAFET dù tốt hơn bao nhiêu thì nó cũng sẽ rơi vào tình trạng như FinFET lẫn planar đã từng - không thể thu nhỏ mãi mà không gặp vấn đề. Vì thế từ trước khi GAAFET được đưa vô khai thác, các NSX đã bắt tay vô tìm kiếm các giải pháp có thể thay thế để làm ra những con chip tốt hơn.

GAAFET dù tốt hơn bao nhiêu thì nó cũng sẽ rơi vào tình trạng như FinFET lẫn planar đã từng - không thể thu nhỏ mãi mà không gặp vấn đề. Vì thế từ trước khi GAAFET được đưa vô khai thác, các NSX đã bắt tay vô tìm kiếm các giải pháp có thể thay thế để làm ra những con chip tốt hơn.Tới đây, chúng ta không thực sự chắc chắn đâu sẽ là con đường để đi tiếp. Nhưng về căn bản, có 2 hướng có thể kể đến là (1) thay đổi hình thái transistor giống như quá khứ đã làm, (2) tìm kiếm loại vật liệu mới có các tính chất tốt hơn các vật liệu đang sử dụng.

Với hướng đầu tiên, hiện nay đang có 2 đề xuất đến từ hãng IMEC (một công ty chuyên bán dẫn). 1 là thiết kế Forksheet (FS) và 1 là CFET (complementary FET). Cả 2 đề xuất này cùng dựa trên ý tưởng kết hợp transistor loại N và P lại làm một. Thực tế hiện nay transistor N và P vẫn được sản xuất độc lập, có nghĩa 1 tổ hợp N-P sẽ cần tới 2 transistor độc lập đứng kề nhau. Nếu có thể ghép cả 2 lại làm 1 transistor thì không gian chiếm dụng sẽ giảm đi đáng kể. Tất nhiên, điểm trừ của thiết kế này là không phải lúc nào hãng chip cũng cần tới 1 transistor tổ hợp như trên. Và chúng ta cũng chưa rõ liệu hiệu suất làm việc của transistor này có hiệu quả bằng 2 transistor độc lập hay không. Vì thế FS hay CFET có được áp dụng vô thực tiễn hay không vẫn là câu hỏi còn bỏ ngỏ.

Với hướng thứ hai, thực tế các NSX đã từng áp dụng cách này trong quá khứ. Cụ thể như strained silicon (dùng mạng lưới tinh thể germanium để "kéo dãn" các nguyên tử silicon - do Ge có chung hoá trị 4 như Si) giúp electron di chuyển dễ dàng hơn. Hoặc vật liệu cách điện High-K để thay thế silicon dioxide (SiO2) do năng lực cách điện của SiO2 suy giảm mạnh khi bề dày của lớp này mỏng đi (dẫn tới sự rò rỉ điện áp từ gate sang channel làm tăng công suất tiêu thụ điện). Hoặc SOI (silicon on insulator) khi tạo thêm 1 lớp SiO2 nằm bên dưới source/channel/drain nhằm giảm bớt điện dung ký sinh của transistor, góp phần tăng hiệu suất làm việc.

Quay lại câu chuyện "hậu GAAFET", những bàn luận chính về vật liệu chủ yếu nằm ở source/channel/drain sẽ được sản xuất từ nguyên tố gì. Hiện tại chúng ta đang có Si tinh thể (poly Si) và Si "kéo dãn" (SiGe). Nhưng khi độ dày các vật liệu này trở nên quá mỏng, thì khả năng di chuyển của dòng electron trong chúng sẽ bị tụt đi đáng kể, bất kể hiệu ứng trường do gate tạo ra mạnh đến mức nào (tưởng tượng 1 ngõ hẻm < 1 mét thì kể cả xe 2 bánh cũng không chạy qua suôn sẻ được). Tại sự kiện IEDM thứ 68 diễn ra vào năm ngoái, các nhà nghiên cứu khắp thế giới đã cùng chia sẻ một vài ý tưởng về các vật liệu có thể thay thế Si. Chúng có tên gọi chung là vật liệu 2D (ám chỉ bề dày chỉ có 1 lớp phân tử).

Những cái tên 2D có thể kể ra như graphene (lưới carbon dạng tổ ong), Molybdenum Disulfide (MoS2), Tungsten Disulfide (WS2), Tungsten Diselenide (WSe2)... Carbon Nanotube (CNT) tuy không phải là 2D nhưng cũng được nêu ra vì có thuộc tính điện lý phù hợp để làm bán dẫn (đường kính tối thiểu 1 nm). Hầu hết các vật liệu trên cho phép dòng electron chảy qua mạng tinh thể tốt hơn ngay cả khi độ dày < 1 nm (Ge "chào thua" ở 2 nm và Si ở 1 nm).

Mặc dù "hấp dẫn" là thế, quá trình sản xuất/tích hợp vật liệu 2D lên các wafer Si hoàn toàn không đơn giản. Ở các tiến trình MOSFET kể trên, bề dày của một lớp vật liệu vẫn có ít nhất hàng trăm - hàng ngàn phân tử (1 nguyên tử Si có đường kính chỉ 0.2 nm). Tạo ra một lớp vật liệu chỉ dày vài lớp phân tử là cực kỳ khó. Thêm vào đó, rủi ro xuất hiện lỗi trên mạng tinh thể là cực lớn. Ví dụ như graphene là vật liệu 2D "trưởng thành" nhất hiện nay vẫn gặp phải tình trạng "sạn" (grain) (các vòng carbon không phải 6 cạnh) khi sản xuất bằng phương pháp Kết tủa Bay hơi Hoá Chất (CVD). Gần đây có một phương pháp mới tên gọi Kết tủa Lớp Nguyên tử (ALD) nhưng vì quá mới nên chúng ta chưa có nhiều dữ liệu để so sánh.

Một trong các khó khăn khác khi sản xuất vật liệu 2D là chúng thường được tạo ra trong môi trường nhiệt độ cực cao (> 600 °C) trên các tấm đồng hoặc sapphire chứ không làm trực tiếp trên wafer Si. Do đó sẽ phát sinh thêm vấn đề làm sao chuyển giao lớp phân tử 2D "mong manh" trên sang tấm Si được hoàn chỉnh.

Nhìn chung, những con đường mới vẫn còn khá "rậm rạp, chông gai và đầy thách thức". Một số có thể sẽ không bao giờ "thành đường". Song có thể nói rằng các transistor sẽ còn tiếp tục nhỏ hơn, hay đúng hơn, các con chip sẽ có thêm nhiều transistor hơn trước trong nhiều năm nữa. Và chúng ta sẽ có nhiều sản phẩm mạnh mẽ hơn nữa. Vấn đề chỉ còn lại - chi phí sản xuất chip có tăng lên nhiều hay không khi công nghệ làm ra chúng ngày càng phức tạp hơn?

Mình nghĩ là vây cá chứ không phải vảy cá.

Hình 3D của FinFET thì 2 cái kênh (S, D) nó nhỏ như cái vây đâm ra từ người con cá (là cực cổng G)

Hoặc hiểu theo nghĩa cái cực cổng G nó đang vây hai cái cực kênh (S/D) lại.

thành tựu nước nhà thì ko đăng bài suốt ngày đăng ba thứ gì gì

chứ viết chung chung như kia thì phi kim, kim loại như nhau cả

https://en.wikipedia.org/wiki/Valence_and_conduction_bands

Nhìn vào thấy hoa mắt chóng mặt đau đầu :D