High Bandwidth Memory (HBM) là một loại giao tiếp RAM tốc độ cao, trong đó các đế chip DRAM sẽ được chồng lên nhau theo chiều dọc và có một đường kết nối từ trên xuống dưới để truyền dẫn tín hiệu. HBM được phát triển bởi AMD và Hynix, sau đó họ đề xuất chuẩn này lên Hiệp hội công nghệ thể rắn (JEDEC) để tiếp tục biến thành chuẩn chung. So với giao tiếp RAM truyền thống là DDR4 (dùng cho bộ nhớ chính của thiết bị điện tử) hay GDDR5 (dùng cho chip đồ họa), HBM hứa hẹn mang lại hiệu năng cao hơn trong khi mức độ tiêu thụ điện thì giảm đi. Trong bài này mời các bạn tìm hiểu thêm nhiều thông tin thú vị khác về HBM nhé.

1. Vì sao HBM ra đời?

Theo tài liệu của SK Hynix hồi năm 2014, hiện nay càng lúc các bộ xử lý càng trở nên mạnh mẽ hơn, dù cho đó là CPU, GPU hay là chip xử lý tín hiệu mạng. Trong tương lai, xu hướng đó sẽ không dừng lại khi mà càng ngày càng có nhiều ứng dụng nặng về đồ họa ra đời, kết nối Ethernet thì sẽ có lúc đạt đến 40Gbps hay thậm chí là 100Gbps chứ chắc chắn không chỉ dừng ở con số 10Gbps hiện tại.

Và để có thể đảm đương được ngần ấy lượng dữ liệu trong một thời gian ngắn, bộ xử lý sẽ cần đến một bộ nhớ đủ nhanh để có thể đưa dữ liệu đầu vào cho CPU/GPU kịp lúc cũng như nhận lại dữ liệu đã được xử lý xong. Nếu bộ nhớ không nhanh thì sẽ xảy ra hiện tượng nghẽn cổ chai, đó là khi chip đã xử lý xong loạt dữ liệu đầu tiên rồi nhưng không thể làm tiếp mà phải đứng lại chờ dữ liệu được chuyển đến, điều đó làm giảm đi hiệu năng của hệ thống.

Từ trước đến nay người ta đã làm nhiều cách để giải quyết vấn đề nghẽn cổ chai nói trên, từ việc đưa bộ nhớ tốc độ cao register vào trực tiếp trên đế bán dẫn của CPU cho đến các bộ nhớ đệm cache L1, L2, L3. RAM mà chúng ta đang dùng hiện nay cũng là một cách giảm thời gian chờ dữ liệu được lấy từ bộ nhớ vĩnh viễn (chính là HDD/SSD).

Vấn đề là tốc độ của RAM hiện nay không còn đủ đáp ứng cho các bộ xử lý của tương lai, trong khi cải tiến hay triển khai register, cache mới thì sẽ đắt đỏ hơn, tốn thời gian hơn. Thế nên người ta nghĩ đến việc phải làm mới giao tiếp giữa RAM và hệ thống.

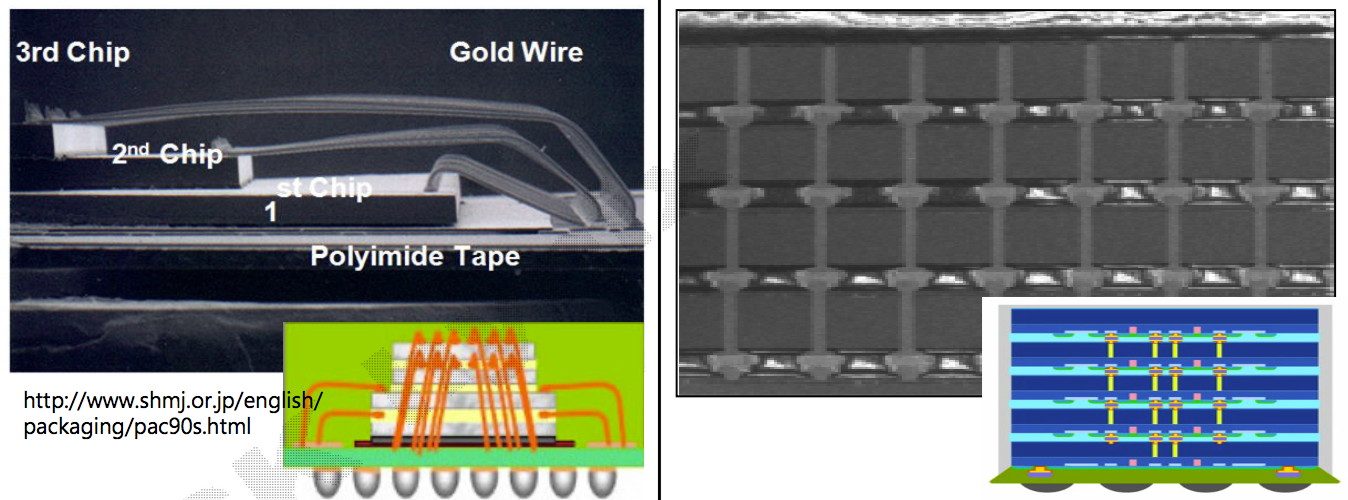

Nhưng HBM cũng chưa ra đời ngay lúc này đâu. Trước khi thật sự đưa ra khái niệm về HBM, người ta đã nghĩ đến TSV (Trough silicon via). Đây là công nghệ dùng các kết nối theo chiều dọc để liên kết các đế chip nhớ lại với nhau, và chúng cũng liên kết luôn chip nhớ với bo mạch bên dưới rồi từ đó dẫn sang CPU/GPU thay vì dùng dây hàn như giải pháp truyền thống. TSV chính là nền tảng cơ bản để AMD và SK Hynix làm ra HBM.

Bên trái là cấu trúc sử dụng dây vàng để liên kết các chip nhớ DRAM đang xài trong chuẩn DDR và GDDR, bên phải là đường liên kết TSV (màu vàng) để nối các chip DRAM xài trong chuẩn HBM

Giải pháp HBM thương mại sắp được triển khai vào các sản phẩm thực tế sử dụng 4 con chip DRAM chồng lên nhau theo chiều dọc, mỗi chip có 2 kênh truyền dữ liệu tương tự như giao diện DDR tiêu chuẩn. Như vậy cứ một cụm HBM 4 chip thì sẽ có 8 kênh, mà tuyệt hơn nữa là mỗi kênh này đều độc lập với nhau nên những gì xảy ra ở một kênh sẽ không làm ảnh hưởng đến các kênh còn lại. Dung lượng của chúng có thể từ 1 đến 32GB tùy theo ý định của nhà sản xuất.

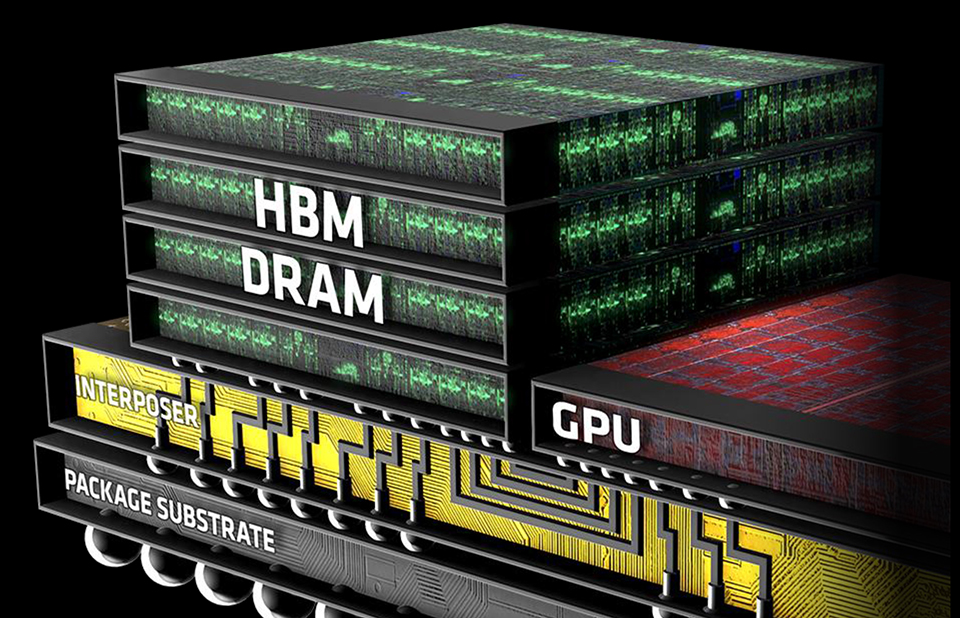

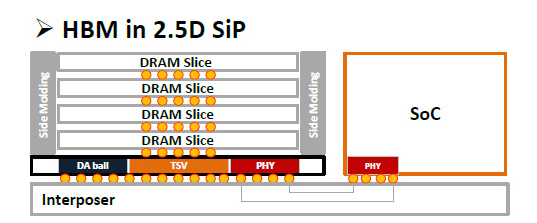

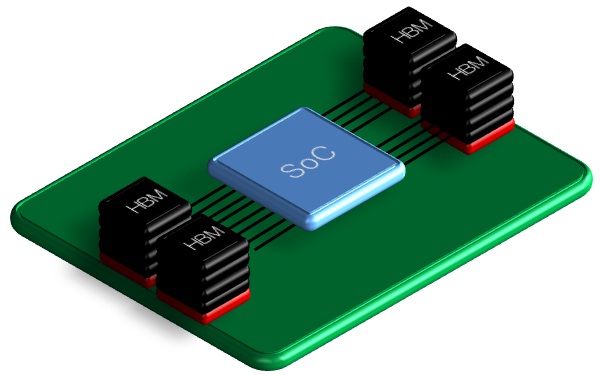

Ở thời điểm ban đầu, các chip HBM sẽ được đặt BÊN CẠNH bộ xử lý (CPU/GPU/SoC). Chính vì thế giải pháp này được gọi là 2,5D mà thôi. Trong tương lai, các nhà sản xuất sẽ tiếp tục phát triển nó thành 3D thực thụ, lúc đó các cụm DRAM có thể nằm bên trên bộ xử lý.

HBM sẽ cạnh tranh trực tiếp với Hybrid Memory Cub (HMC), cũng là một loại bộ nhớ xếp chồng lên nhau, có điều đứng sau nó là Intel và Micron. Samsung cũng có dòng chip nhớ 3D của riêng mình.

Cấu trúc của bộ nhớ HBM 2,5D: 4 con chip DRAM đặt chồng lên nhau, bên dưới nó là lớp nền và các lớp liên kết (Interposer), đặt bên cạnh SoC

Quảng cáo

2. Lợi ích của HBM

Lợi ích đầu tiên đó là tốc độ. Do chip nhớ DRAM được đặt gần bộ xử lý hơn nên tốc độ truyền tải sẽ nhanh hơn. Giải pháp TSV cũng góp phần tăng cao tốc độ truyền tải so với việc sử dụng các kênh RAM riêng lẻ như truyền thống. Theo số liệu của NVIDIA, một kênh bộ nhớ HBM thì sẽ mang lại băng thông khoảng 16 đến 32GB/s. Với giải pháp 4 chip 8 kênh như đã nói ở trên, chúng ta có tổng băng thông lên đến 128-256GB/s. Và nếu ghép nhiều cụm chip lại thì con số này còn tăng lên nữa.

Để các bạn dễ so sánh thì GPU mạnh nhất của NVIDIA hiện tại dùng cho mục đích chơi game là GeForce GTX TITAN Black, nó sử dụng giao tiếp GDDR5 và có băng thông vào khoảng 336GB/s. Với các GPU trong tương lai sử dụng 4 cụm HBM (4 * 4 = 16 con chip DRAM), băng thông này hoàn toàn có thể đạt đến mức 512GB đến 1TB/s.

Lợi ích thứ hai là về diện tích. Một cụm chip HBM chỉ tốn khoảng 42mm vuông mà thôi, trong khi chip DDR3 thì phải cần đến 117mm vuông. Kết hợp với việc nó có thể được chồng lên trên bộ xử lý (hoặc đặt bên cạnh), người ta có thể làm ra những thiết bị ngày càng nhỏ gọn hơn mà không phải hi sinh hiệu năng.

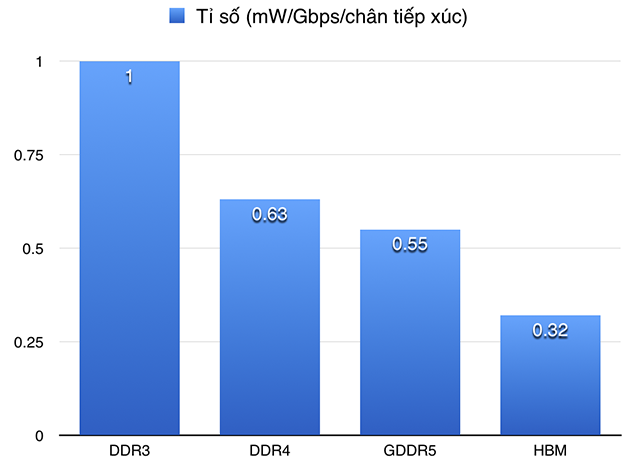

Lợi ích thứ ba là về năng lượng. HBM có mức độ tiêu thụ điện trên mỗi chân chip thấp hơn nhiều so với GDDR5 lẫn DDR4, dòng điện cần để bộ nhớ hoạt động cũng thấp hơn nên hiệu quả tiêu thụ điện cao hơn. AMD cho biết các GPU xài bộ nhớ HBM của họ sắp ra mắt trong năm sau có tỉ số hiệu năng/watt điện cao gấp 3 lần so với chuẩn GDDR5 hiện nay, còn mức độ tiêu thụ điện thì giảm đi 42% đến 50%.

Quảng cáo

3. Hai thế hệ HBM

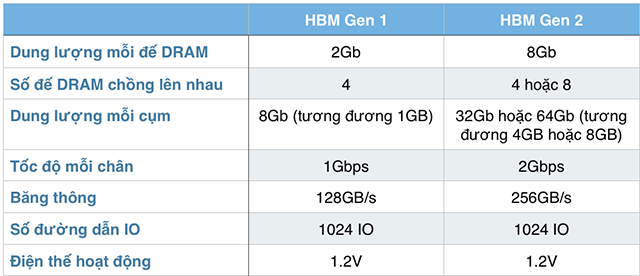

Hiện tại HBM đã được phát triển lên đến thế hệ thứ 2, và đây cũng là thế hệ sẽ được AMD xài cho các GPU của mình vào năm 2016. Hay nói cách khác, khi vừa đến tay người dùng thì HBM đã đạt đến thế hệ 2 rồi. Bên dưới là sự khác biệt cơ bản giữa HBM Gen 1 và Gen 2.

4. Các tính năng khác của HBM

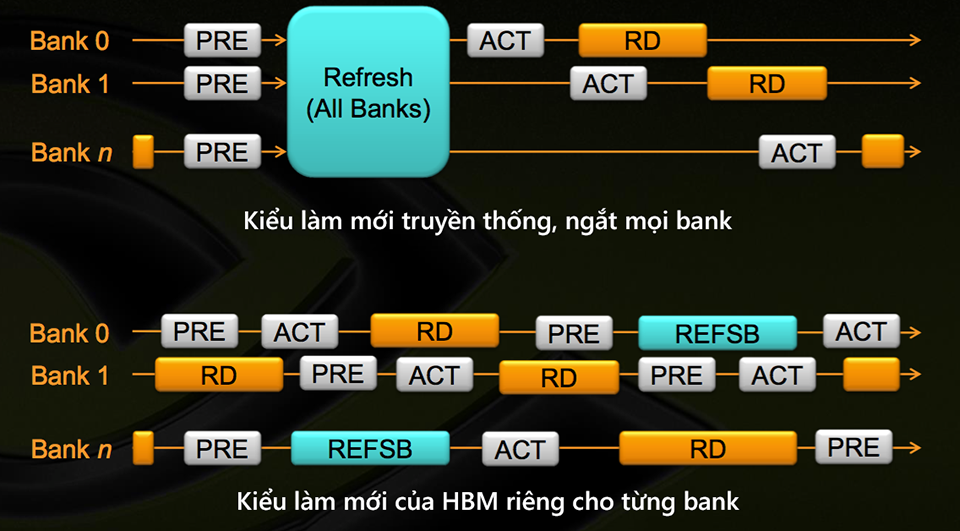

Bộ nhớ máy tính thường được chia thành các "bank", có thể hiểu như các phân nhánh nhỏ của bộ nhớ, để cho phép việc truy cập song song diễn ra dễ dàng hơn, và trong máy tính bình thường của chúng ta thì mỗi khe gắn RAM sẽ có nhiều bank.

Trong quá trình DRAM hoạt động, điện tích của mỗi cell sẽ bị giảm đi theo thời gian. Chính vì thế, chuẩn DDR yêu cầu mỗi cell nhớ phải được "làm mới" sau mỗi 64 micro giây, và khi việc này diễn ra thì tất cả các bank đều phải bị đóng lại khiến băng thông tiềm năng bị giảm đi 5-10%. Còn với chuẩn HBM, mỗi bank có thể được làm mới riêng rẽ nên bus dữ liệu lúc nào cũng trong trạng thái "kích hoạt" cả. Song song đó, nếu bank này đang đóng thì bank khác sẽ chạy những tác vụ như đọc hoặc lấy dữ liệu nhằm tiết kiệm thời gian.

Ngoài ra, HBM còn có thể điều chỉnh tần số làm mới dựa theo nhiệt độ của thiết bị. Bộ điều khiển (memory controller) sẽ lấy thông tin từ một cảm biến nhiệt để điều chỉnh cho phù hợp: nếu máy đang ở chế độ nghỉ và mát mẻ thì tần số sẽ khác, nếu nhiệt độ nóng lên lúc tải nặng thì sẽ khác.

5. Kết

Tóm lại thì HBM có 4 điều cần lưu ý như sau:

- Tốc độ cao hơn so với RAM DDR truyền thống, có thể lên tới 256GB/s cho mỗi cụm chip HBM

- Dung lượng mỗi cụm RAM cao hơn, mỗi cụm có thể lên tới 8GB, và có thể ghép nhiều cụm lại với nhau

- Giúp tạo ra những thiết bị nhỏ hơn, gọn hơn

- Hiệu quả tiêu thụ năng lượng tốt hơn

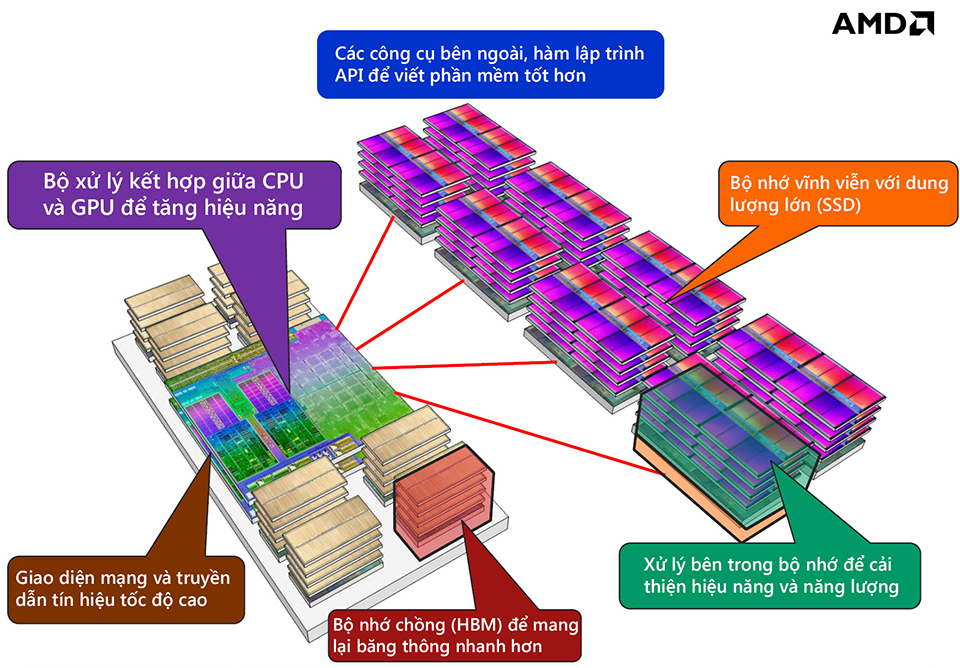

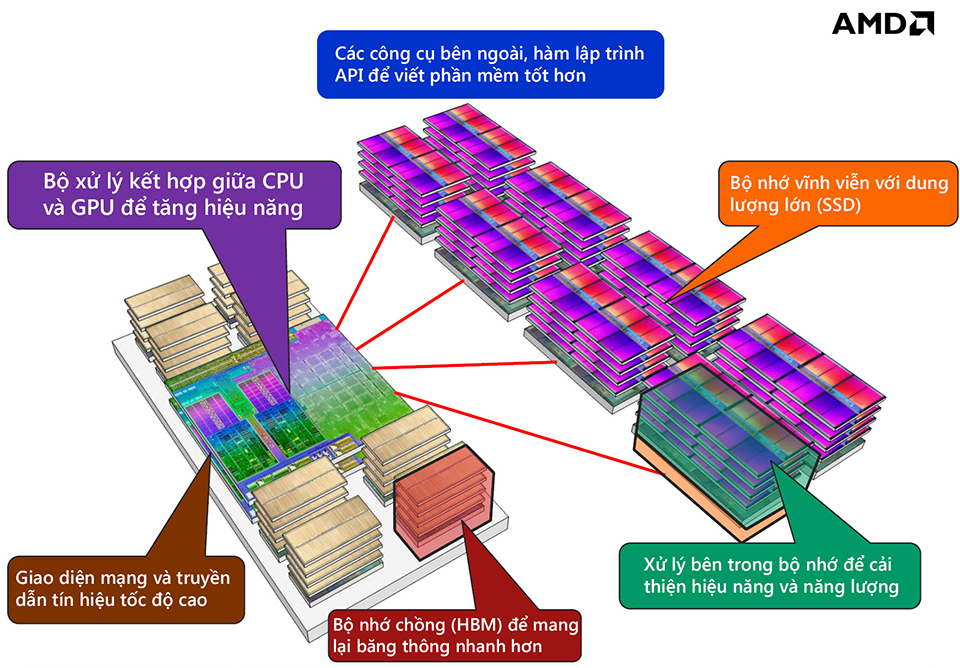

Tầm nhìn của AMD về tương lai của thiết bị điện toán, chúng bao gồm những thành phần sau