Mấy ngày nghỉ Tết âm lịch 2024 mình vẫn làm việc với máy tính, chợt nghĩ ra là những món đồ công nghệ hiện tại mà chúng ta đang sử dụng, đa phần đều có liên quan đến bán dẫn. Transistor là thành phần hay có thể coi là đơn vị cơ bản hình thành nên rất nhiều thứ phục vụ cho cuộc sống hiện đại. Anh em có bao giờ thắc mắc người ta chế tạo ra bán dẫn như thế nào chưa?

Trong khuôn khổ bài viết này, chúng ta sẽ gặp rất nhiều thuật ngữ chuyên ngành bán dẫn. Một số có thể bạn đã nghe qua, một số khá lạ lẫm, một số lại bao gồm những cái tên khác (kiểu tập hợp cha vs. tập hợp con), một số có thể tương đồng hoặc gần nghĩa. Vì thế chúng ta sẽ cần một vài "quy định" để việc "đọc hiểu" có thể diễn ra một cách tương đối "chuẩn" nhất.

Transistor. Đây là thuật ngữ chúng ta sẽ gặp nhiều nhất và cũng là cơ bản nhất của bài viết này. Về cơ bản, transistor là một thiết bị bán dẫn có tác dụng để đóng/mở hoặc phóng đại tín hiệu/cường độ dòng điện. Các mạch điện hoặc mạch điện tích hợp (IC) là sự kết hợp giữa các transistor lại với nhau - trong đó đầu ra tín hiệu của transistor này sẽ là đầu vào của một hoặc nhiều transistor khác hoặc ngược lại - góp phần tạo ra những mạch chức năng chuyên môn tuỳ theo ý muốn của kỹ sư hoặc nhà sản xuất (NSX).

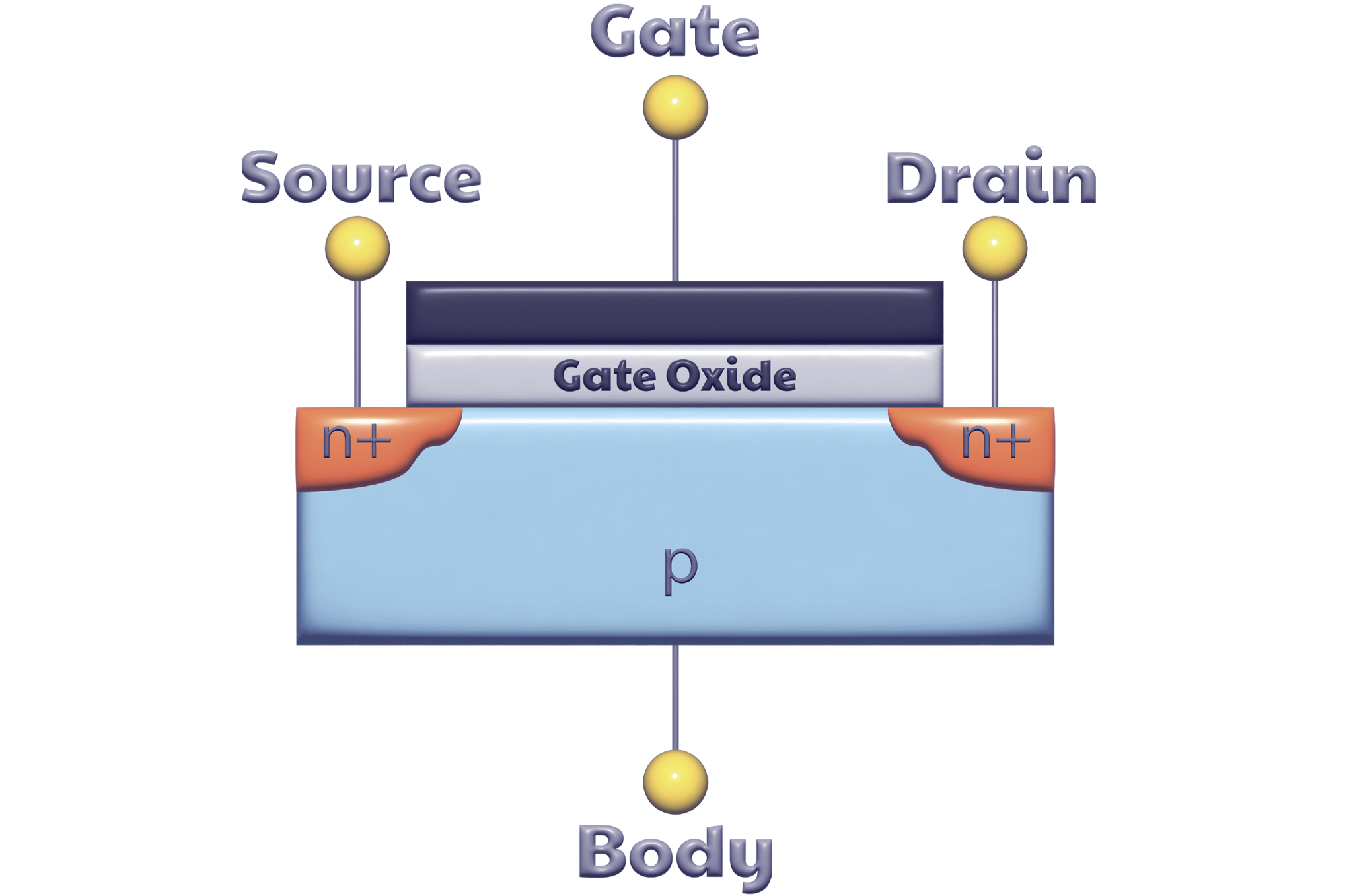

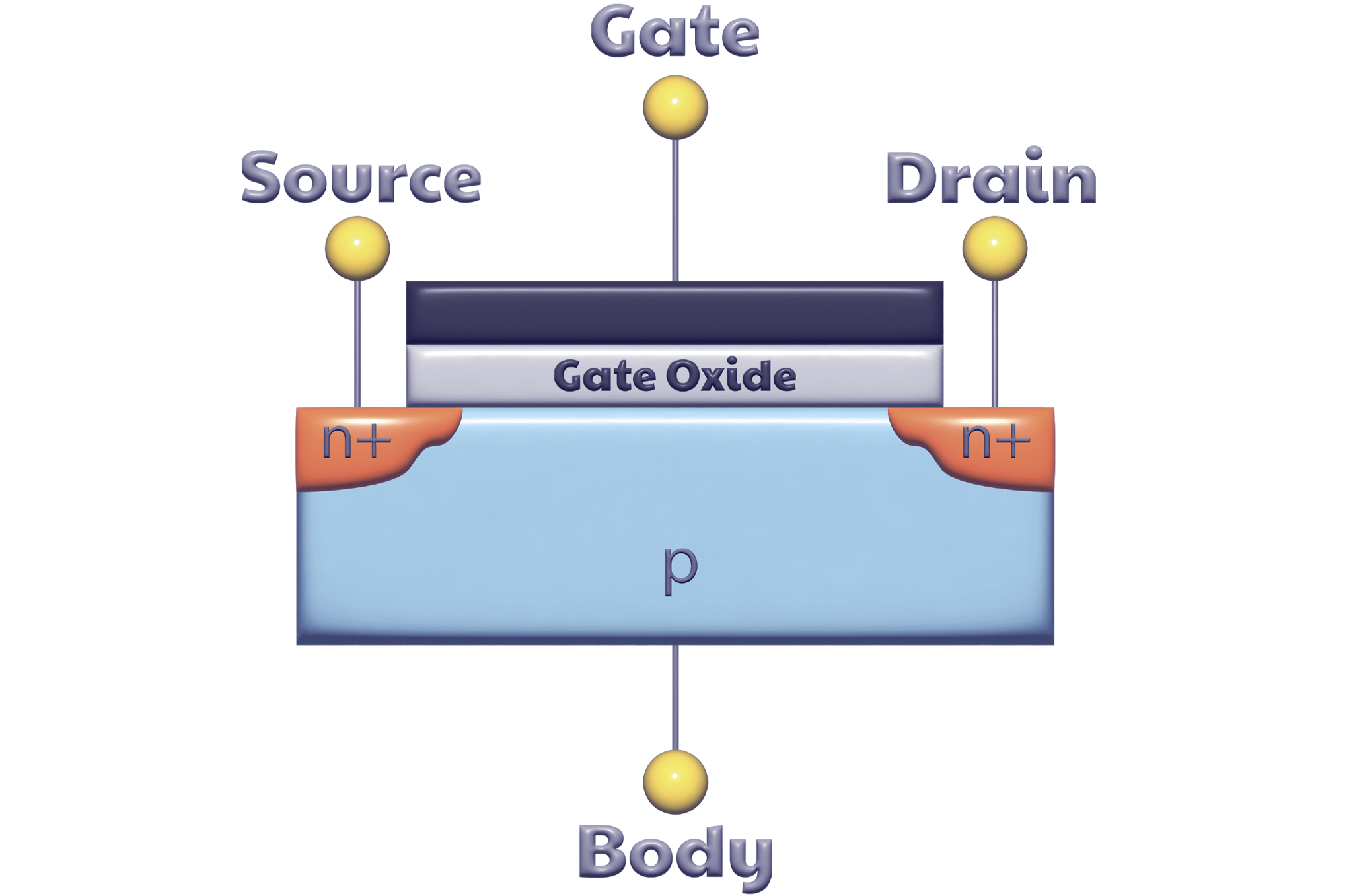

Gate hoặc cổng tín hiệu là một thành phần của transistor. Đây có thể xem là thành phần quan trọng nhất vì nếu không có nó thì ý niệm về transistor xem như "phá sản" - chúng ta sẽ không thể nào ngắt/đóng dòng điện nếu không có cầu dao, công tắc hoặc CB (Circuit Breaker). Tuy gate không phải là thứ trực tiếp dẫn tín hiệu điện trong mạch, nhưng nó là thứ điều khiển xem mạch điện có tín hiệu hay không. Từ đó chúng ta mới phân định được bit dữ liệu sẽ là 0 hay 1 tuỳ theo tình trạng của mạch điện.

Drain, source hoặc 2 cực của transistor. Nếu một mạch điện không có gate thì nó sẽ không được xem là phân cực. Khi xuất hiện gate thì source (nguồn) sẽ là nơi tín hiệu điện đi vào và drain (đích) là nơi tín hiệu sẽ đi ra. Tuỳ theo bản chất transistor là loại P (positive) hay N (negative) mà giữa source và drain sẽ có dòng điện chạy qua hay không, nhất là khi đang có điện thế đặt vô gate. Để đơn giản vấn đề, chúng ta sẽ tạm hiểu khi gate có điện thì source & drain sẽ có dòng điện chạy qua, tương ứng với mạch ON và giá trị bit là 1.

Channel hay kênh dẫn điện. Đây là phần nằm giữa source & drain và có chức năng chuyển tín hiệu từ nguồn sang đích. Nhưng chức năng của channel không do nó tự quyết định mà bị ảnh hưởng bởi gate nằm ở gần đó. Về bản chất, channel là một vật liệu bán dẫn có khi là chất dẫn điện, có khi là chất cách điện, vốn sẽ thay đổi thuộc tính tuỳ theo điều kiện nhiệt độ, áp suất hoặc dòng điện mà gate tác động lên nó.

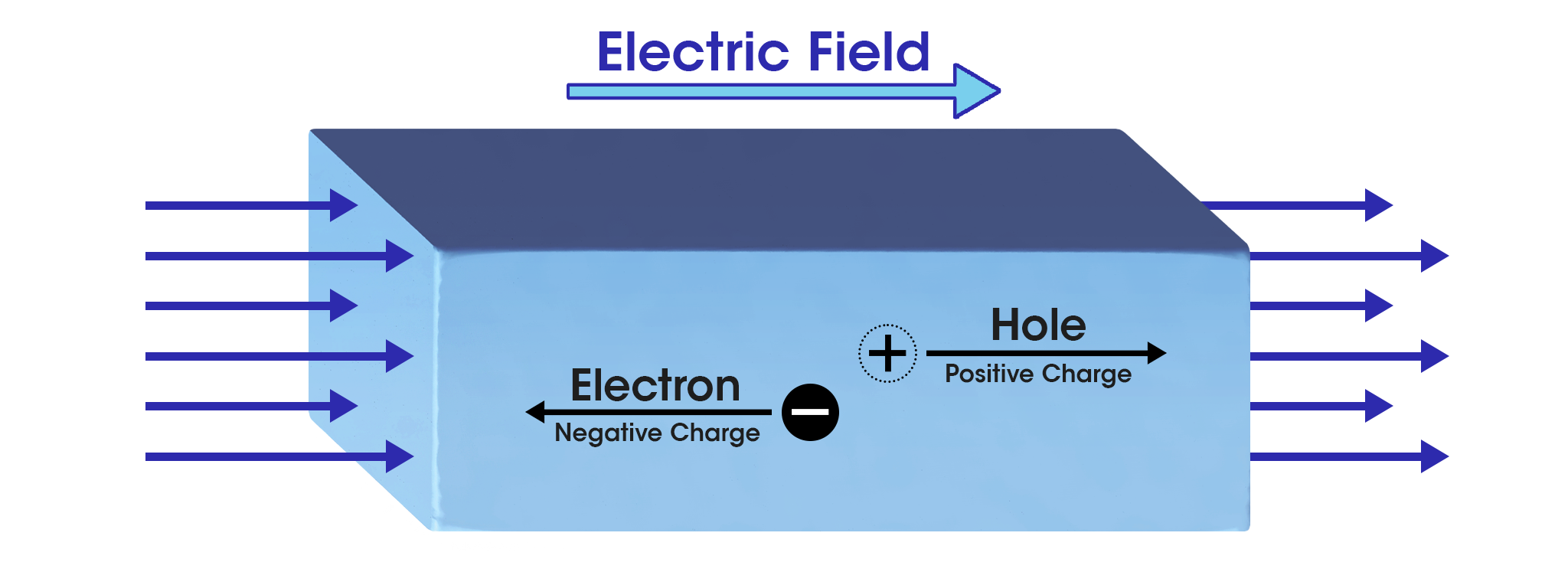

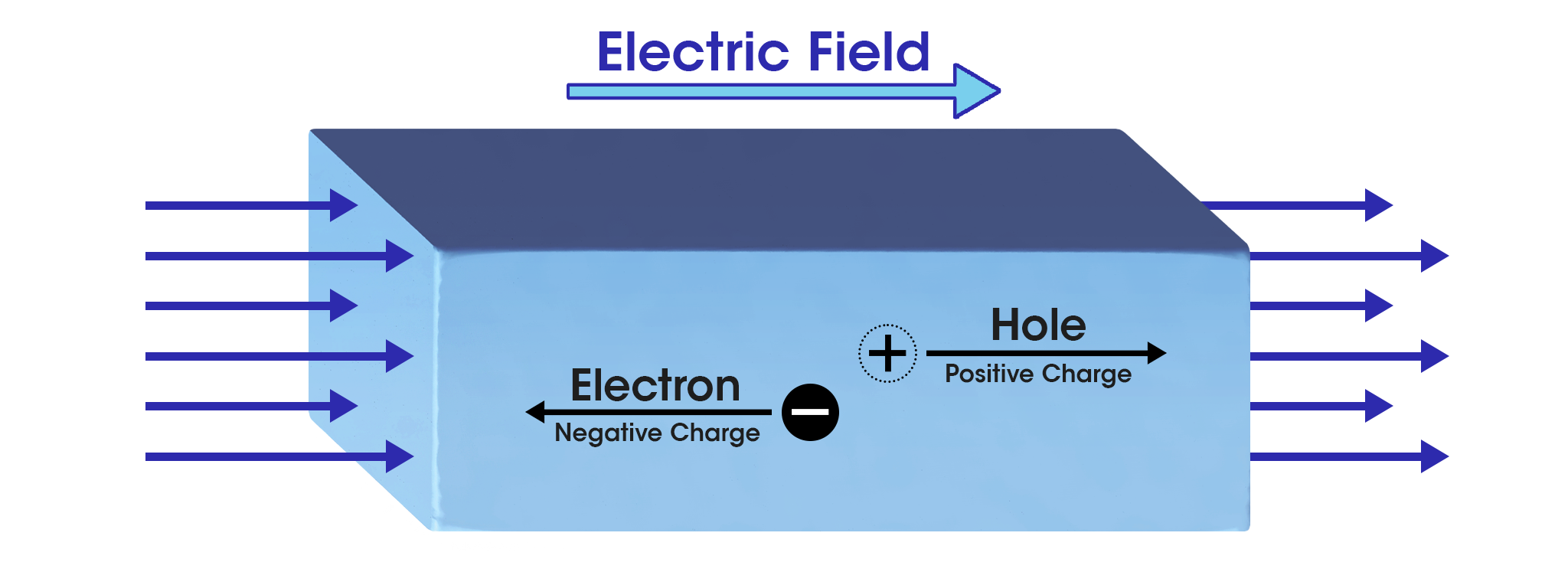

FET hay Field-Effect Transistor là một loại transistor. Có nhiều loại transistor tuỳ theo ứng dụng IC. Trong mảng bán dẫn thì FET là loại transistor quan trọng nhất. Nó dựa trên hiệu ứng trường để thay đổi trạng thái transistor khi có sự thay đổi về điện thế áp dụng lên gate. Cụ thể khi có điện áp trên gate, nó sẽ tạo ra một điện trường (field) và điện trường này sẽ làm thay đổi điện tính của channel. Một điều quan trọng là gate sẽ không tiếp xúc trực tiếp với channel mà qua một lớp cách điện. Do đó, phải có hiệu ứng trường thì FET mới hoạt động được.

MOSFET hoặc MISFET. Đây là loại FET được sử dụng phổ biến nhất ngày nay. Nó thường được sản xuất dựa trên việc oxy hoá lớp vỏ bề mặt tấm wafer silicon. Và thông qua các quá trình in khắc/quang lithography, điện phân, ăn mòn acid hoặc kết tủa kim loại... (tuỳ theo từng công nghệ bán dẫn) mà transistor được hình thành. Trên thực tế, FinFET hay GAAFET cũng là MOSFET, chủ yếu khác nhau ở cấu tạo hoặc cách làm ra các thành phần như gate, drain/source và channel. Ở nghĩa hẹp, MOSFET có thể hiểu là dạng FET sản xuất trên mặt phẳng 2D (planar), khác với không gian 3D như FinFET hay GAAFET.

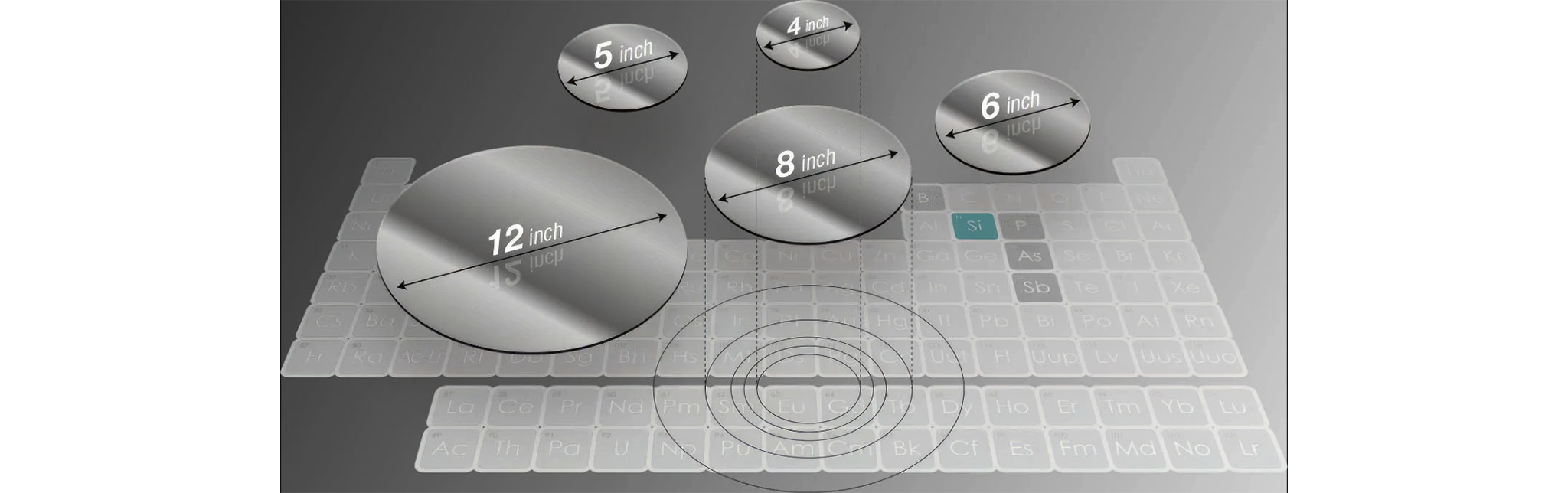

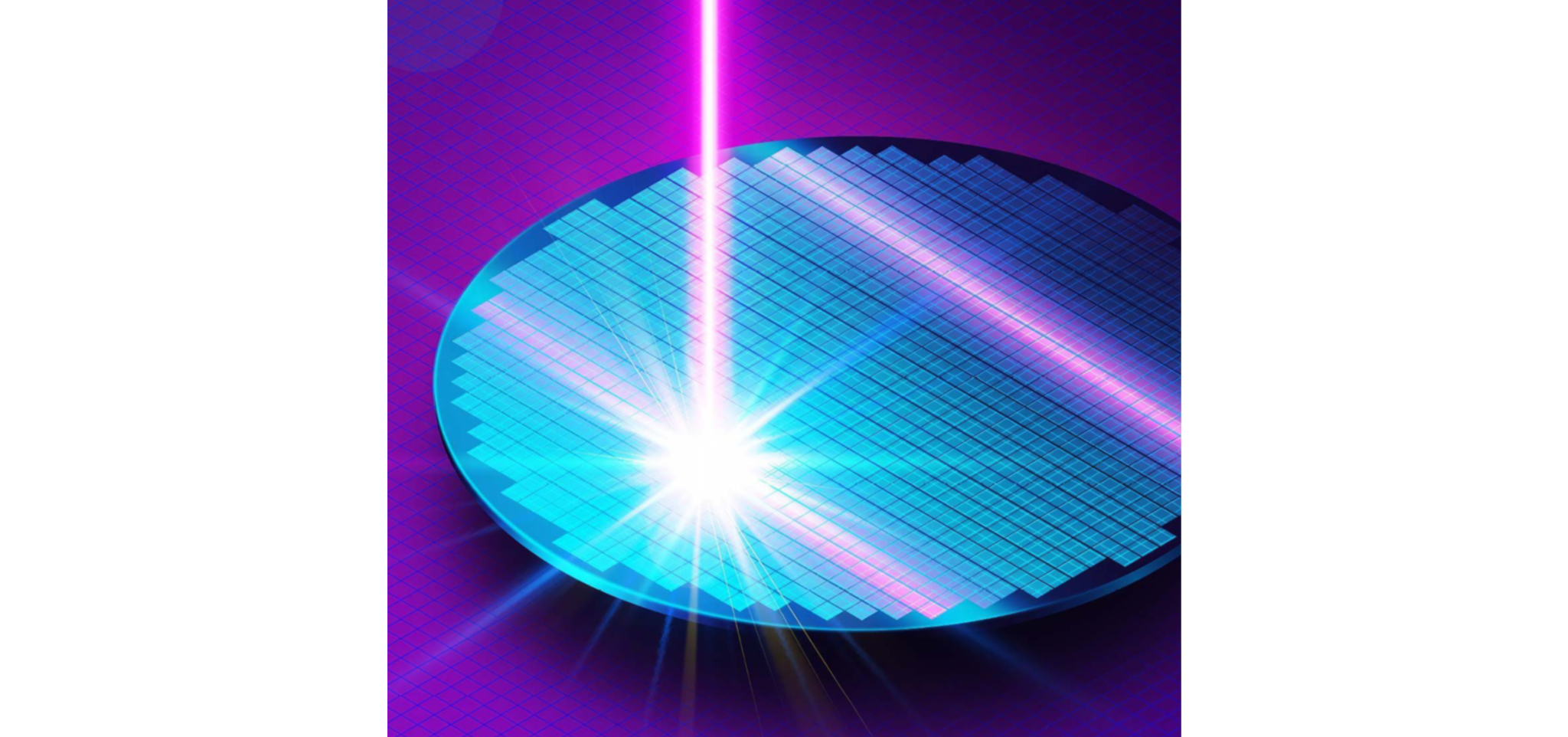

Wafer (silicon). Là tấm nền làm ra transistor có cấu tạo từ các tinh thể silicon (Si) được tạo ra bằng cách nấu chảy cát hoặc các chất chủ yếu chứa cấu trúc silic. Wafer cần có độ tinh khiết rất cao tới 99.9999999% hoặc hơn (cấp độ 9N) mới có thể được dùng để sản xuất ra chip. Wafer hiện nay chủ yếu có các kích thước tính theo đường kính như 100 mm (4 inch), 150 mm (6 inch), 200 mm (8 inch) và 300 mm (12 inch).

Trước khi đào sâu hơn về khác biệt giữa 3 loại transistor nêu ở đầu, chúng ta cần hiểu hơn một chút về cách một con transistor phổ thông (planar) được chế tạo như thế nào. Trong khuôn khổ bài này, chúng ta chủ yếu nói về kỹ thuật in quang lithography đang được sử dụng phổ biến nhất hiện nay. Tất nhiên sẽ có một số khác biệt ở từng tiến trình cụ thể, ở từng công ty cụ thể, nhưng nhìn chung hầu hết sẽ có những bước cơ bản liệt kê dưới đây.

Làm sạch wafer. Wafer sau khi sản xuất xong có thể chưa được dùng ngay mà vẫn để trong kho lưu trữ. Trong khi lưu trữ, chúng vẫn có thể dính phải tạp chất và cần phải được làm sạch bằng các hoá chất dạng lỏng nhằm loại bỏ các tạp chất vô cơ, hữu cơ, phần tử ion hoặc các lớp oxide.

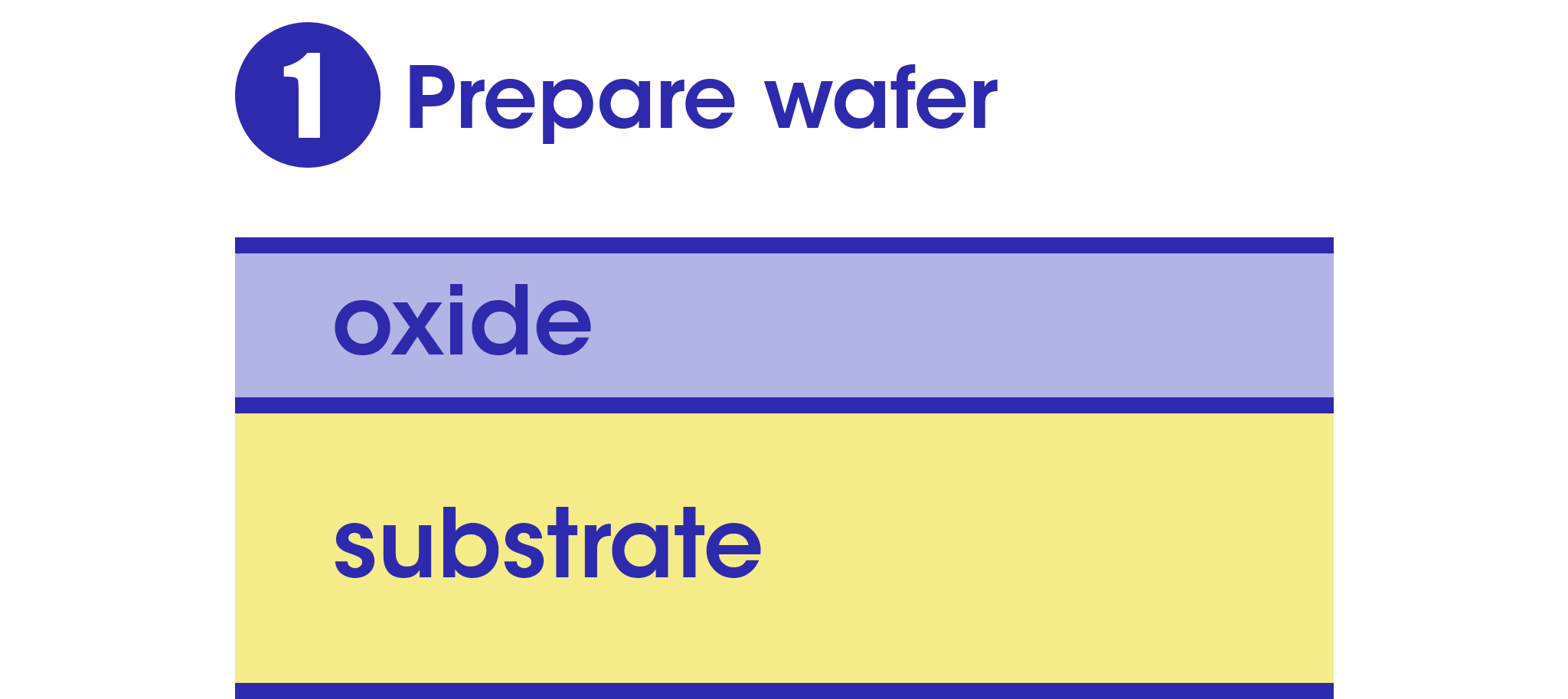

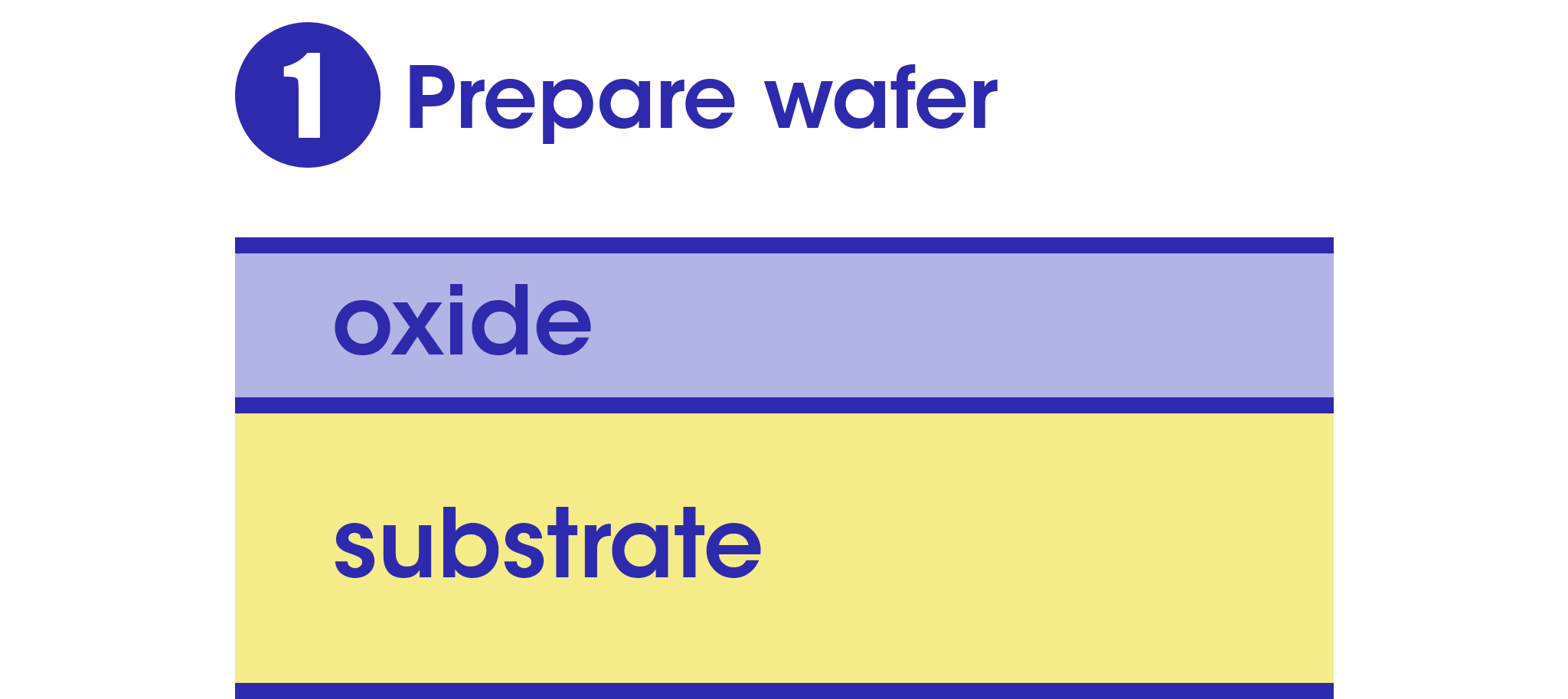

Chuẩn bị wafer. Wafer sau khi được làm sạch sẽ cần gia nhiệt sơ ở 150 °C trong khoảng 10 phút. Mục đích của bước này là để loại bỏ hoàn toàn mọi hơi ẩm hoặc phân tử nước còn bám trên bề mặt. Để chắc ăn hơn, NSX còn có thể phủ thêm một lớp chống thấm vừa có tác dụng ngăn phân tử nước, vừa hỗ trợ việc phủ lớp chặn quang (diễn ra ở sau) được tốt hơn. Sau đó tấm wafer có thể được phơi khô ở 120 °C để giúp "tạo nét" các vi mạch rõ ràng hơn.

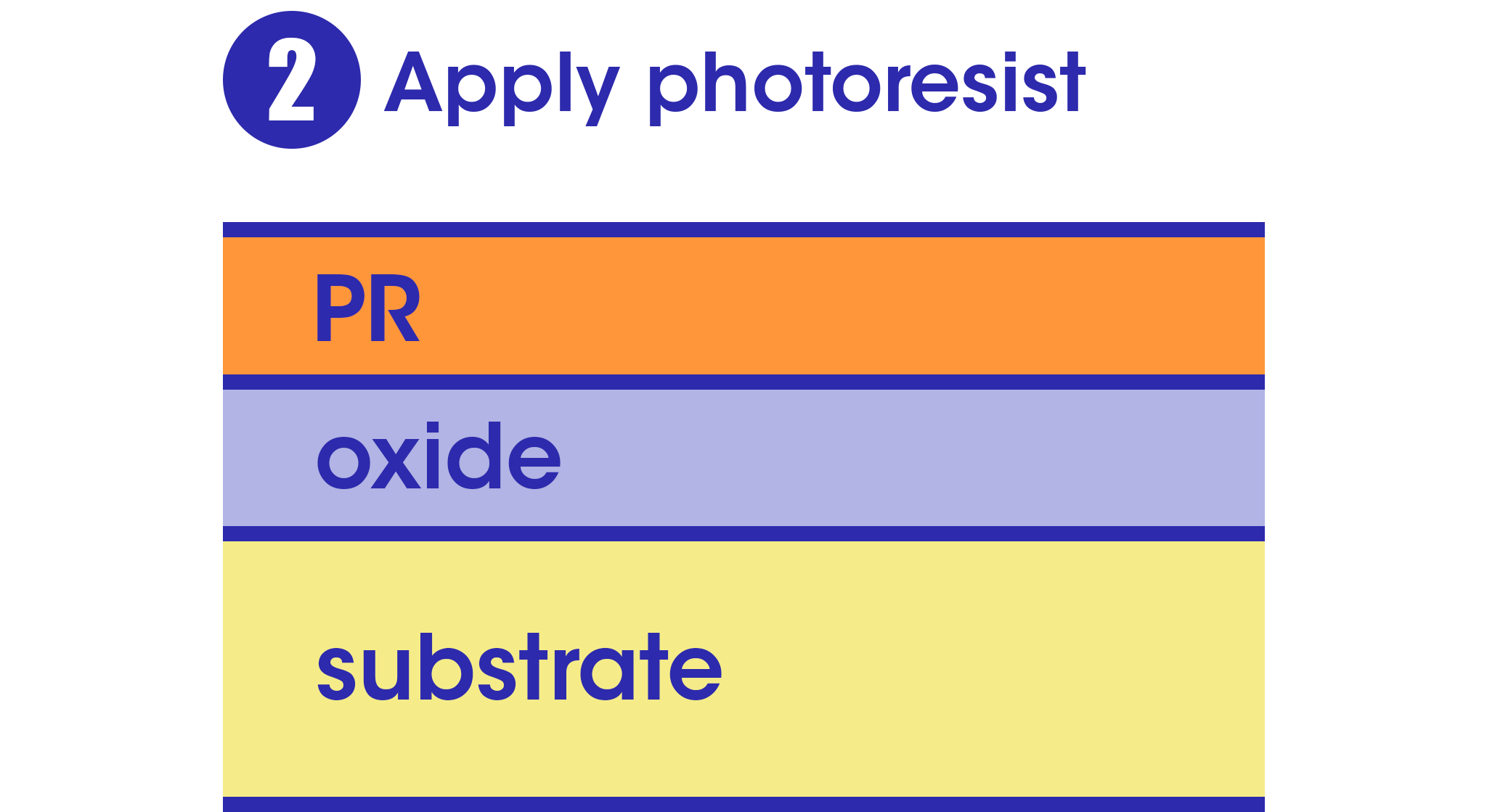

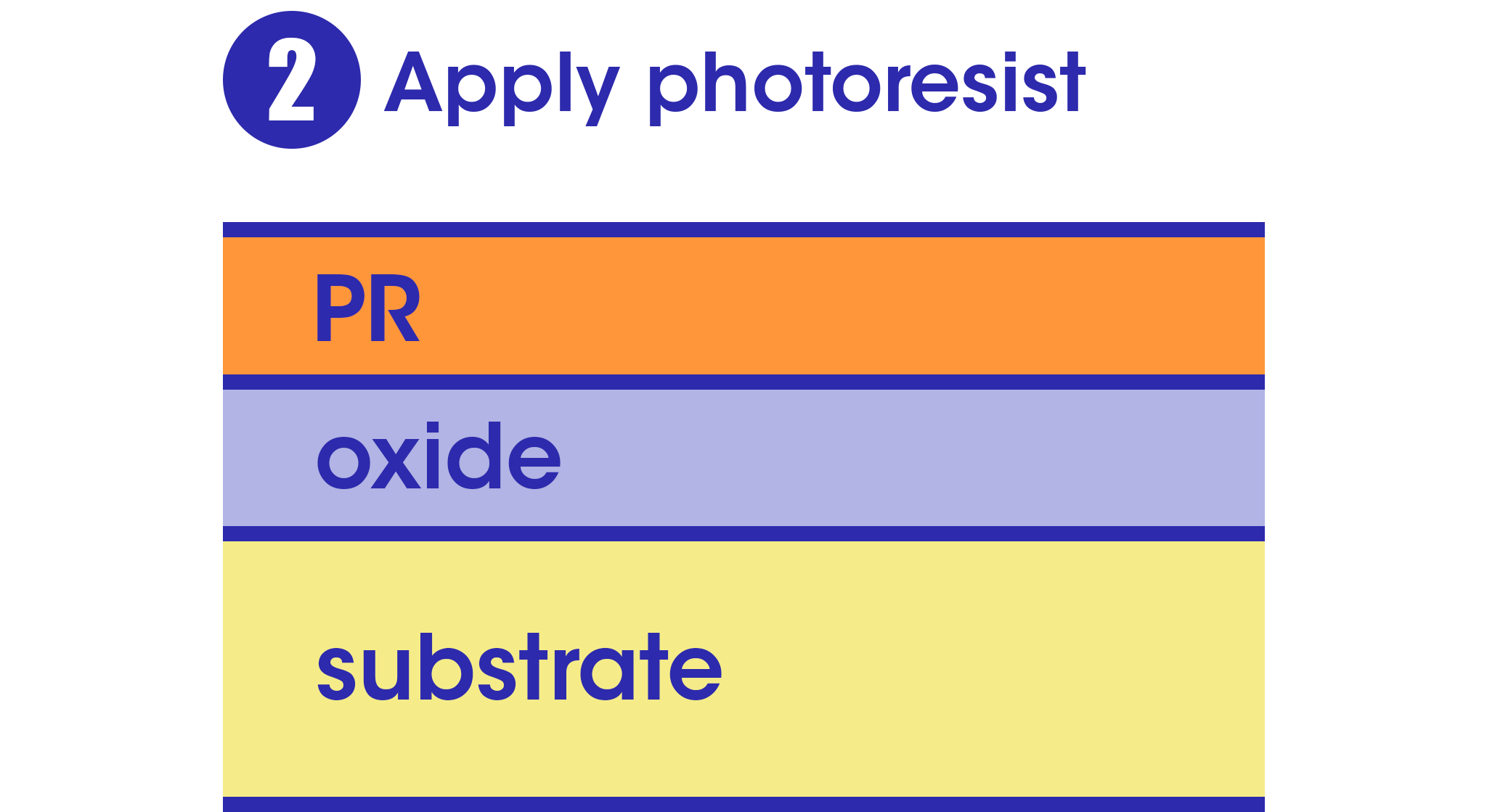

Phủ chất chặn quang (photoresist). Bản chất của phương pháp in quang lithography chính là các phản ứng hoá học dựa trên tiếp xúc quang học (photo). Trong đó những khu vực phơi sáng (hoặc không phơi sáng, tuỳ loại hoá chất) sẽ diễn ra các thay đổi về mặt hoá học so với các khu vực còn lại. Những thay đổi này tạo điều kiện cho các phản ứng hoá học diễn ra sau đó và sau khi các phản ứng này hoàn tất, trên bề mặt tấm wafer sẽ hình thành ra các cấu trúc vi mạch khác nhau, làm tiền đề để hình thành nên con chip sau này.

Trong đó, việc phủ chất chặn quang là bước đầu tiên để các quá trình trên diễn ra. Cụ thể, tấm wafer sẽ được đặt trên một bàn xoay và chất chặn quang sẽ được thả lên đó. Nhờ lực ly tâm của bàn xoay nên lớp chặn quang sẽ được dàn đều ra khắp nơi nhằm đảm bảo độ dày của nó là gần như đồng nhất trên toàn bộ wafer. Độ dày của lớp chặn quang hết sức quan trọng vì nó quyết định tới độ chính xác các cấu trúc vi mạch sau đó. Với các cấu trúc siêu vi dưới 125 nm, độ dày tối đa cho lớp chặn quang là 0,5 µm (hoặc 500 nm). Sau đó, tấm wafer sẽ được "nấu sơ" (baking) ở 90 - 100 °C trong khoảng 1 phút để bay hơi bớt lượng chặn quang còn thừa trên bề mặt.

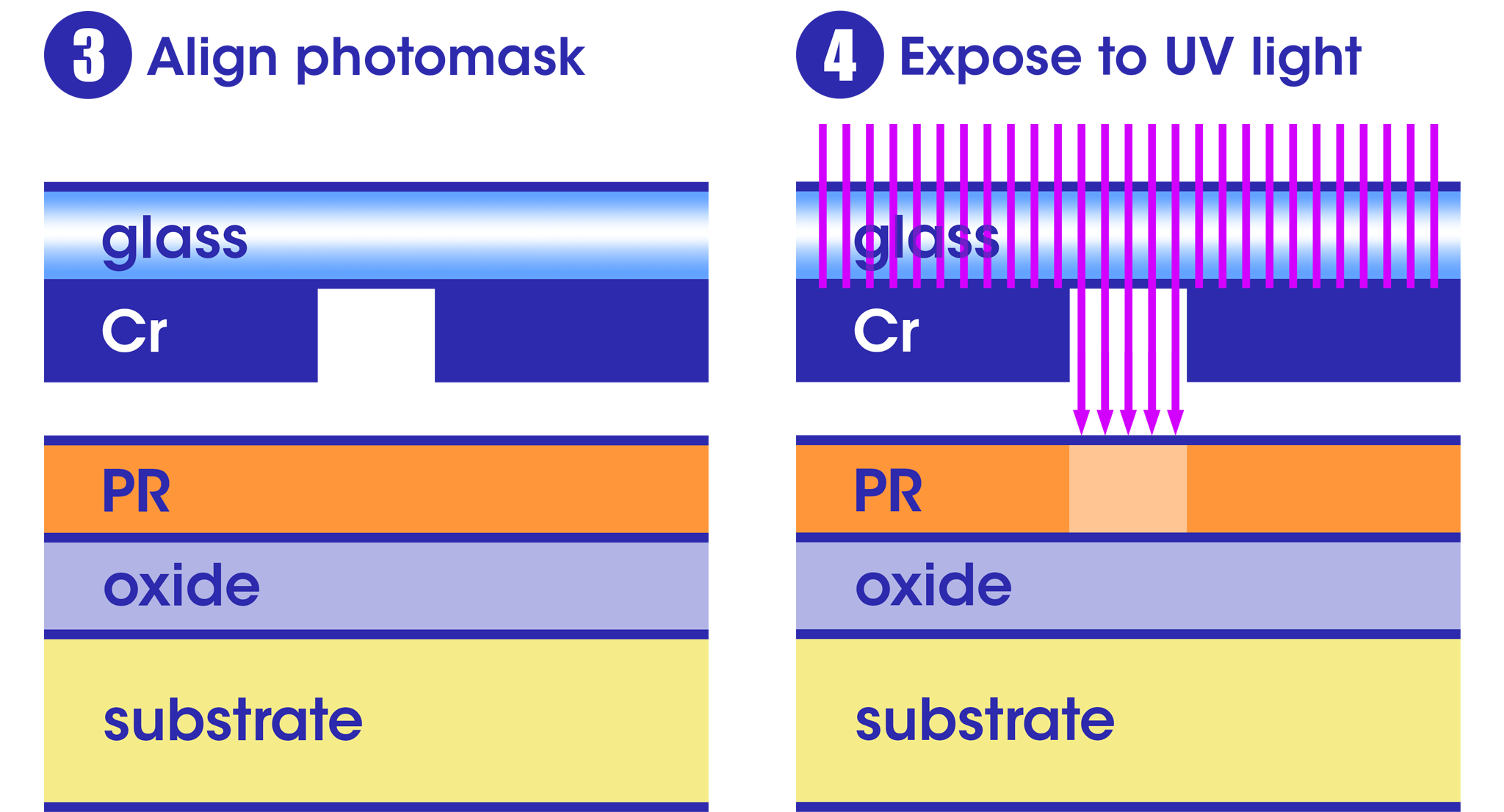

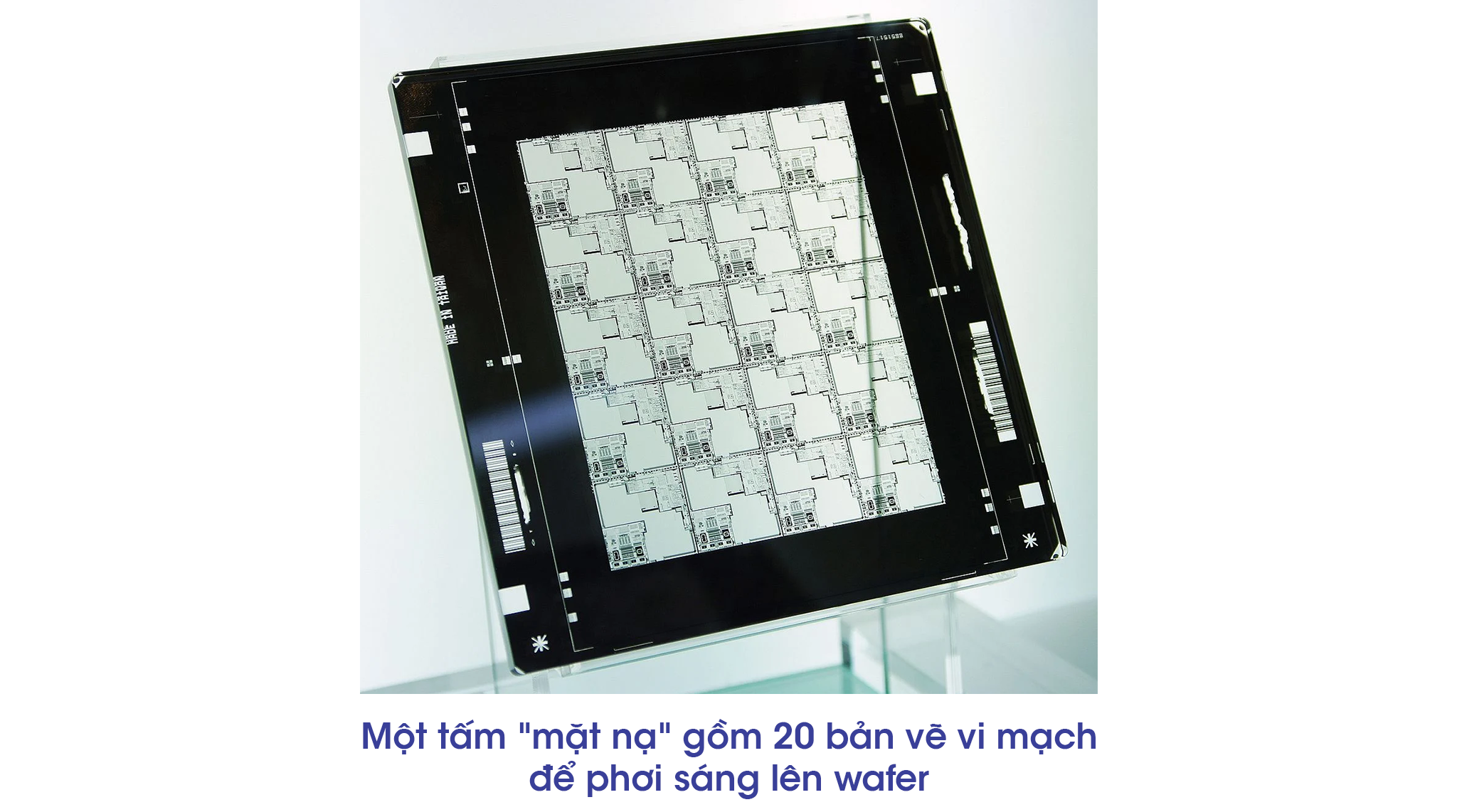

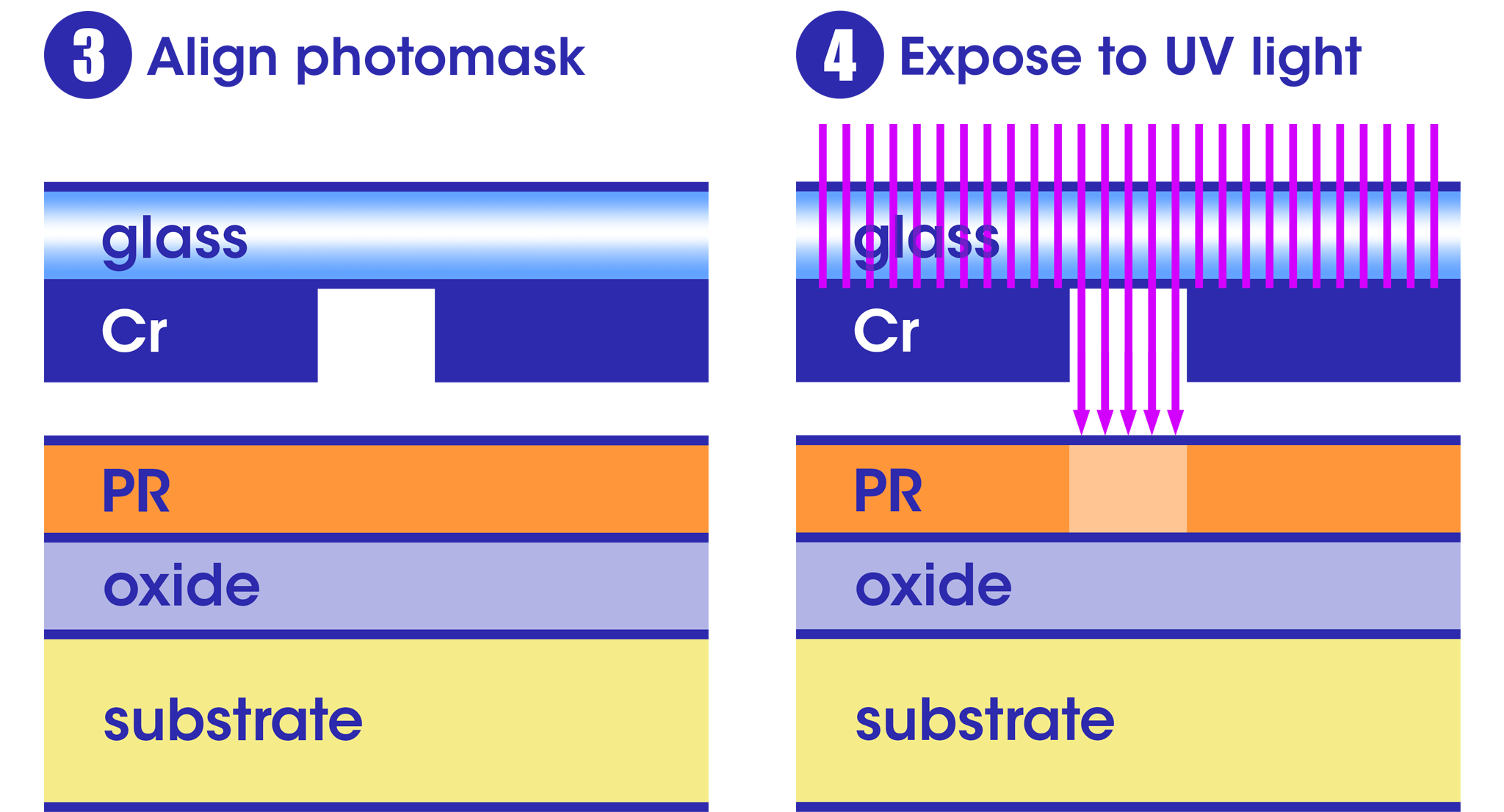

Phơi sáng (hoặc chụp phơi sáng). Wafer sau khi được phủ chặn quang sẽ được đưa tiếp qua công đoạn chụp phơi sáng. Đây là bước tại sao chúng ta có thể tạo ra được các transistor siêu nhỏ ở cấp độ hàng trăm hoặc hàng chục nm. Chính là nhờ 2 yếu tố - mặt nạ quang học (photomask) và bước sóng phơi sáng (UV, DUV, EUV). Trong đó, mặt nạ gồm mặt cắt bản vẽ vi mạch của die chip (cỡ lớn) và một hệ thấu kính giúp thu nhỏ bản vẽ đó hàng trăm, hàng ngàn lần lên tấm wafer. Nhưng để các cấu trúc vi mạch có thể hình thành chính xác trên tấm wafer thì đòi hỏi bước sóng phơi sáng phải càng ngắn càng tốt. Ví dụ DUV có bước sóng từ 193 - 248 nm, EUV thì chỉ có 13.5 nm. Bước sóng càng ngắn thì sai số do giao thoa quang học càng thấp và các "nét vẽ" càng rõ ràng hơn.

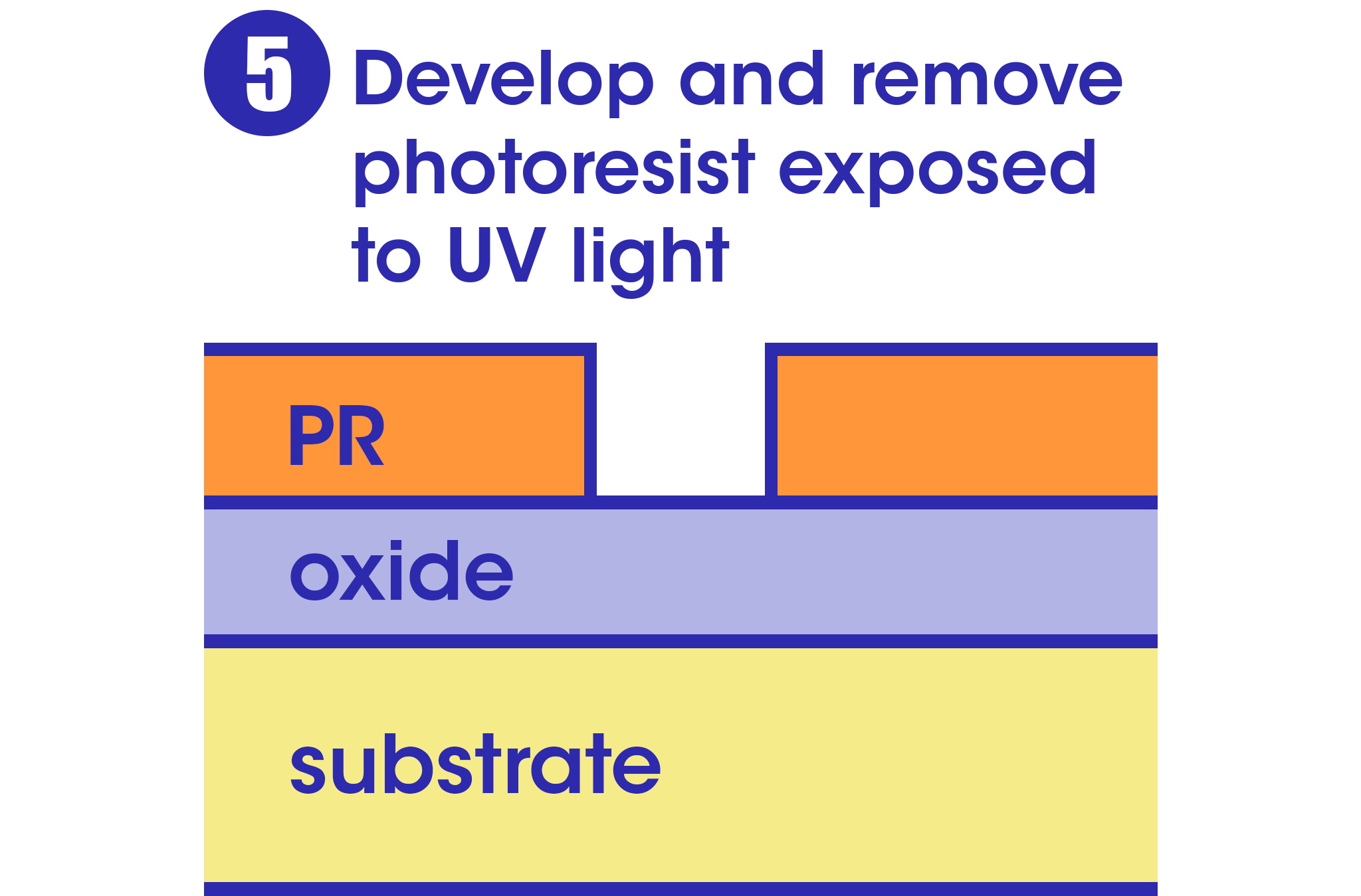

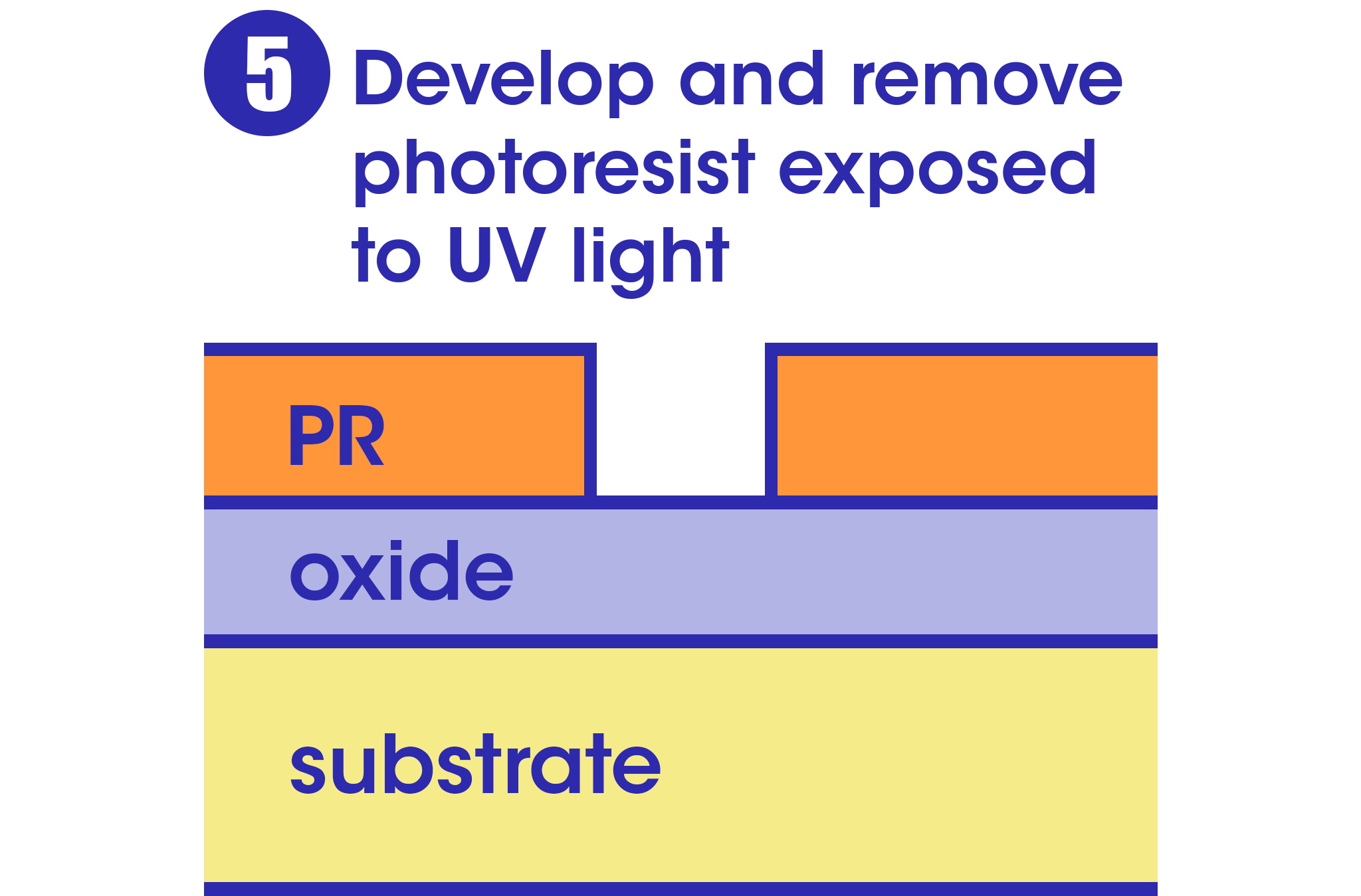

Tráng rửa lớp chặn quang (developing). Dùng từ "tráng rửa" ở đây vì ý nghĩa của nó tương đồng với việc tráng rửa phim trong kỹ thuật chụp ảnh film âm bản. Cụ thể lớp chặn quang sau khi bị chiếu DUV hay EUV, những khu vực "bị lộ" ra sẽ có thuộc tính hoá học khác với khu vực "được che chắn". Tấm wafer cũng sẽ được đặt trên một bàn xoay như ở bước phủ chặn quang. Nhưng lần này nó sẽ được tráng một lớp hoá chất để "bóc tách" phần chặn quang không mong muốn (căn cứ theo bản vẽ chip). Nếu là chất chặn quang dương tính, phần bị phơi sáng sẽ bị hoà tan đi. Nếu là âm tính, thì phần không phơi sáng sẽ bị hoà tan. Những gì không hoà tan còn lại trên tấm wafer là tiền đề cho các vi mạch "mọc" lên (develop) ở các công đoạn sau này.

Cấy ion (implantation). Thực tế cho tới lúc này, các thành phần của transistor (gate, source/drain, channel) vẫn chưa hình thành. Nhưng các bước phủ chặn quang, phơi sáng và rửa chặn quang có tác dụng "phân lô bán nền". Chúng giúp xác định cụ thể vị trí của từng transistor sẽ nằm ở đâu trên tấm wafer. Vì một con chip sẽ là tổ hợp của hàng ngàn, hàng triệu, hàng tỷ transistor khác nhau. Nên các transistor không thể nằm "lộn xộn bừa bãi" mà phải có "địa chỉ" cụ thể.

Khi vị trí từng transistor đã được xác định, chúng ta chuyển qua việc cấy ion và ăn mòn vi mạch. Mục đích của 2 công đoạn này là để tạo ra từng thành phần của transistor. Trên nguyên lý mỗi thành phần sẽ có lý tính, hoá tính khác nhau. Ví dụ nMOSFET sẽ có source/drain cùng loại n (negative hay điện âm), tấm nền loại p (positive hay điện dương). Khi đó việc cấy ion sẽ bao gồm đặt thêm mặt nạ quang học (ứng với bản vẽ nMOSFET) và bắn các ion âm qua các khe hở của mặt nạ lên bề mặt wafer. Các vị trí trên tấm wafer sau khi bị bắn ion âm sẽ trở thành source/drain loại n và có tính dẫn điện. Các vị trí không bị bắn ion sẽ vẫn là trung tính. Với pMOSFET thì ngược lại, vị trí bị bắn sẽ là ion dương và tấm nền là âm. Về bản chất, công đoạn cấy ion tương tự như phơi sáng lớp chặn quang, đều giúp tạo ra các đường nét cho vi mạch.

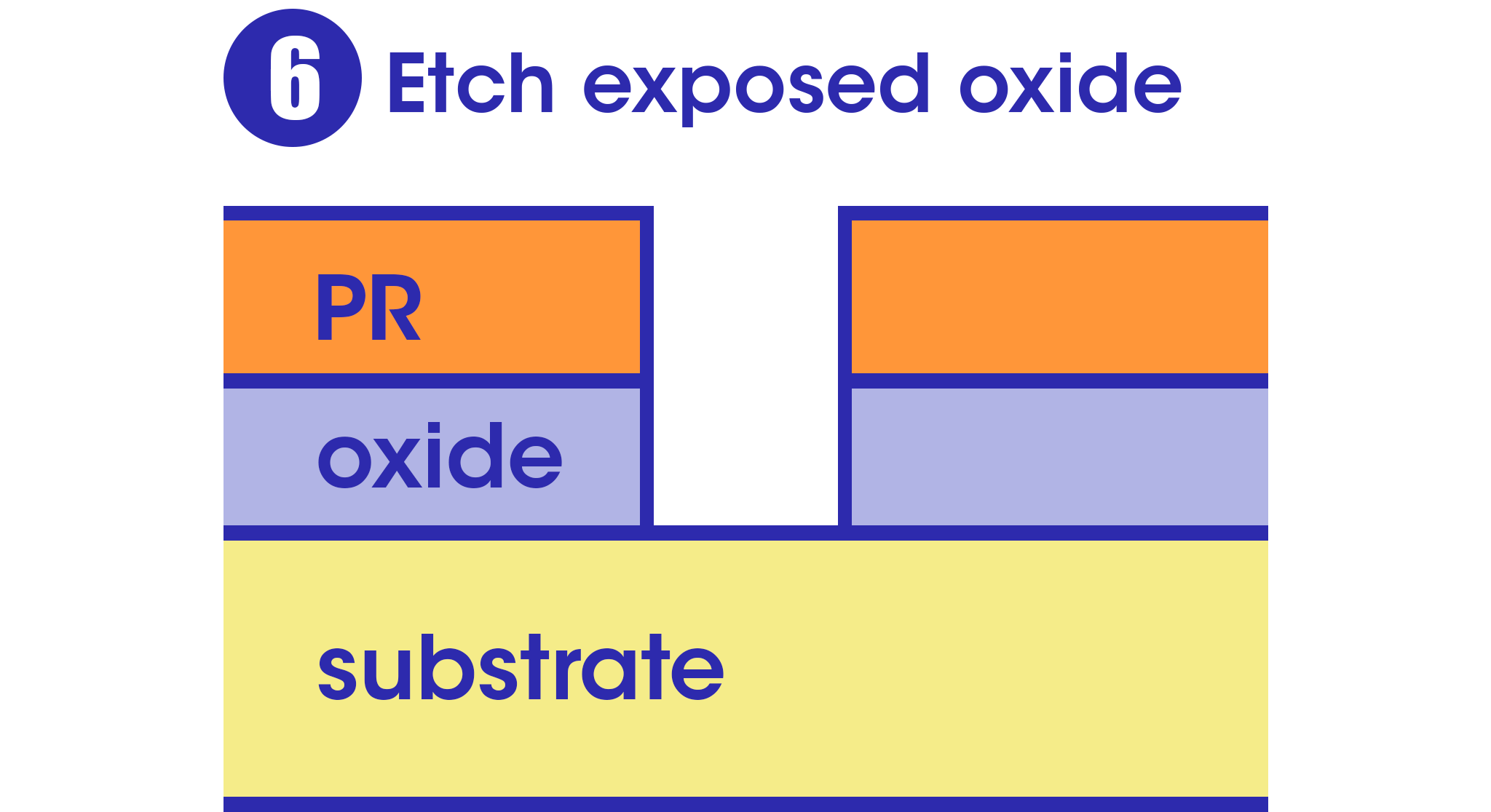

Ăn mòn vi mạch (etching). Nếu cấy ion giống như phơi sáng lớp chặn quang thì ăn mòn sẽ tương tự như tráng rửa lớp chặn quang. Nó có ý nghĩa giúp "bóc" đi những vị trí không cần thiết trên wafer để làm rõ nét các thành phần của transistor hơn. Đồng thời, nó có thể hỗ trợ để chuẩn bị trước cho việc cấy ion vào những vị trí khác các vị trí cấy ban đầu (do khác biệt tính chất, chức năng của từng bộ phận). Nếu gọi cấy ion là "lấp đất" thì ăn mòn vi mạch chính là "đào đất" - cả 2 cùng có tác dụng tương hỗ cho việc làm ra từng cấu thành của con chip. Và một con chip có thể trải qua nhiều lần cấy - đào khác nhau trước khi một sản phẩm hoàn chỉnh ra đời.

Về cách tiến hành, có 2 dạng ăn mòn - ăn mòn "khô" bằng tia plasma hoặc ăn mòn "ướt" bằng hoá chất. Ăn mòn "ướt" tương tự như tráng rửa lớp chặn quang - wafer được ngâm trong một loại hoá chất có khả năng hoà tan những vị trí có hoá tính phù hợp (chẳng hạn acid hoà tan được base hay oxide) từ đó làm lộ ra các vị trí mong muốn. Còn ăn mòn "khô" được thực hiện bằng cách bắn chùm tia plasma lên bề mặt wafer thông qua mặt nạ quang học. Các vị trí bị bắn sẽ xuất hiện các thay đổi lý tính khiến chúng bị bốc hơi đi. Ăn mòn "khô" hiện được ưa dùng hơn do tốc độ bào mòn có thể thay đổi được chứ không đồng nhất ở mọi vị trí như ăn mòn "ướt", từ đó không làm hao hụt đi quá nhiều những vị trí không mong muốn.

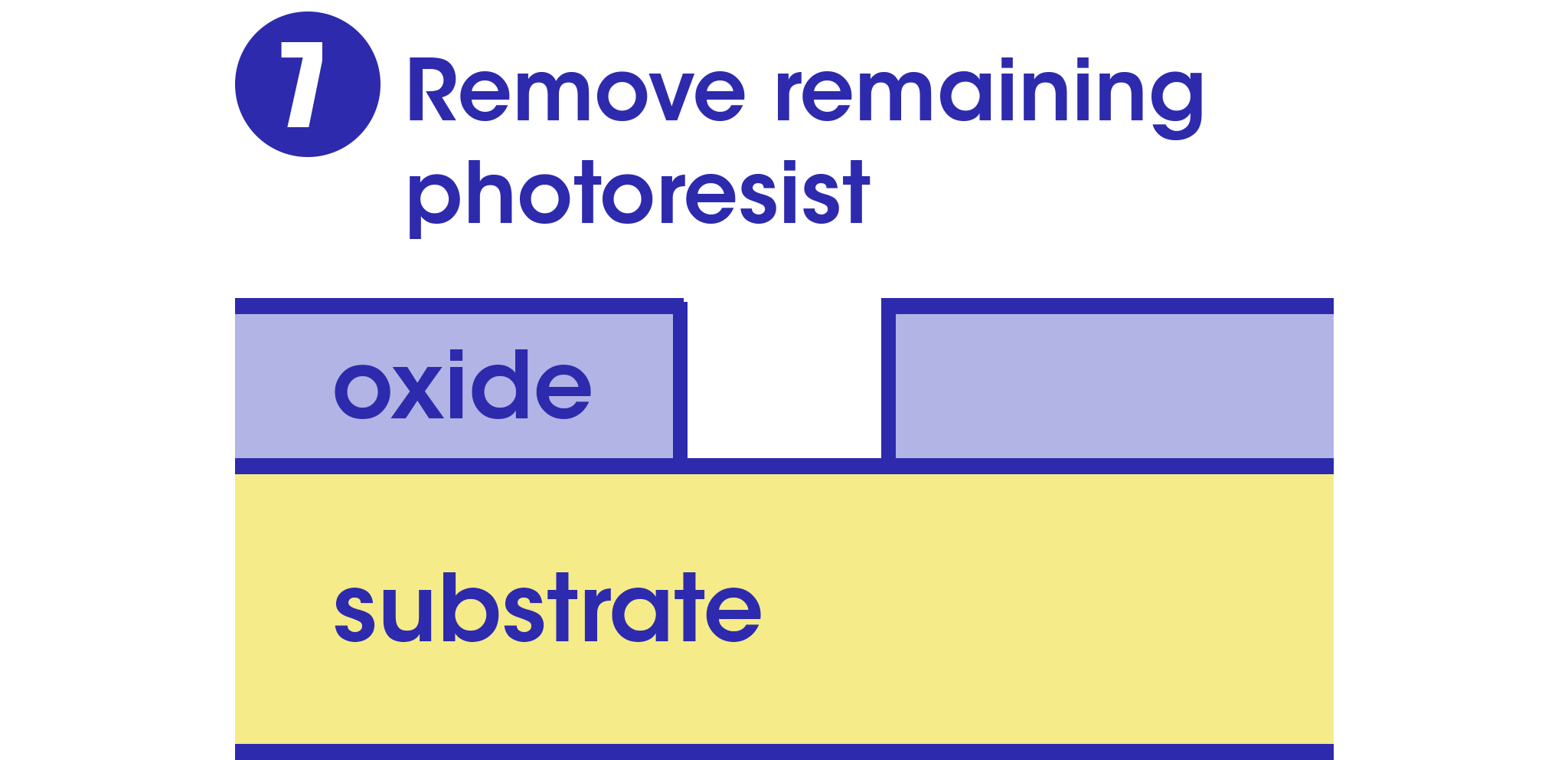

Hoàn tất hoặc loại bỏ lớp chặn quang. Sau khi tất cả các thành phần của die chip đã được làm xong, phần lớp chặn quang còn sót lại (chưa bị rửa đi ở công đoạn trước) sẽ được "bóc" đi nốt. Tương tự bước ăn mòn vi mạch, lớp chặn quang có thể bị loại bỏ bằng hoá chất hoặc bằng tia plasma. Hoá chất sẽ làm thay đổi thuộc tính của lớp chặn quang, khiến cho nó mất khả năng bám dính vô bề mặt wafer. Còn tia plasma đặc biệt có chứa oxygen cũng sẽ làm oxy hoá lớp vật liệu này một cách nhanh chóng. Những gì không mong muốn còn sót lại cũng sẽ được xử lý tương tự.

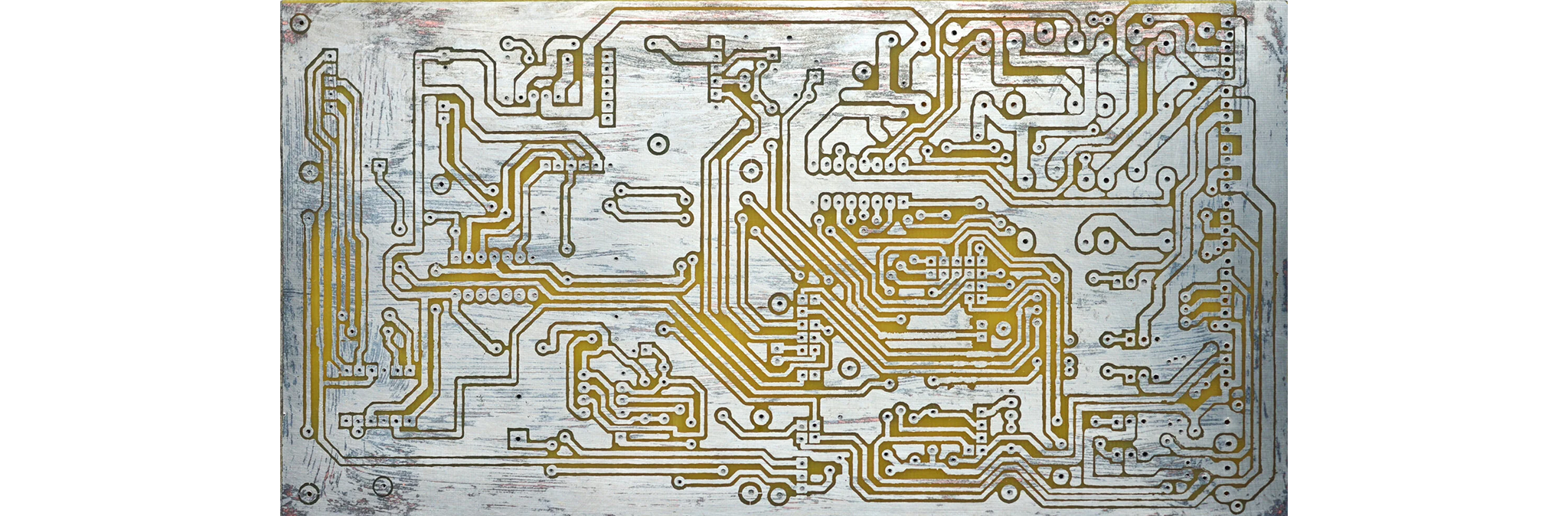

Sản phẩm sau cùng sẽ là tấm wafer có chứa đầy các die chip đã hoàn chỉnh. Việc còn lại là chuyển chúng đến các cơ sở chuyên cắt wafer thành từng die riêng và tiến hành các công tác kiểm định xem die nào hoạt động tốt hay không tốt. Không tốt thì không tốt như thế nào và có thể dùng được tới đâu. Quá trình này gọi là harvest nhằm tận dụng lại những die chip không hoàn hảo để làm ra những model cấp thấp hơn để phân phối ra thị trường. Về khâu này, chúng ta sẽ có bài viết chuyên sâu hơn để bàn.

Video tóm tắt quá trình sản xuất chip.

Phần 2: Planar MOSFET, FinFET, GAAFER và tương lai của ngành bán dẫn

Trong khuôn khổ bài viết này, chúng ta sẽ gặp rất nhiều thuật ngữ chuyên ngành bán dẫn. Một số có thể bạn đã nghe qua, một số khá lạ lẫm, một số lại bao gồm những cái tên khác (kiểu tập hợp cha vs. tập hợp con), một số có thể tương đồng hoặc gần nghĩa. Vì thế chúng ta sẽ cần một vài "quy định" để việc "đọc hiểu" có thể diễn ra một cách tương đối "chuẩn" nhất.

Transistor. Đây là thuật ngữ chúng ta sẽ gặp nhiều nhất và cũng là cơ bản nhất của bài viết này. Về cơ bản, transistor là một thiết bị bán dẫn có tác dụng để đóng/mở hoặc phóng đại tín hiệu/cường độ dòng điện. Các mạch điện hoặc mạch điện tích hợp (IC) là sự kết hợp giữa các transistor lại với nhau - trong đó đầu ra tín hiệu của transistor này sẽ là đầu vào của một hoặc nhiều transistor khác hoặc ngược lại - góp phần tạo ra những mạch chức năng chuyên môn tuỳ theo ý muốn của kỹ sư hoặc nhà sản xuất (NSX).

Gate hoặc cổng tín hiệu là một thành phần của transistor. Đây có thể xem là thành phần quan trọng nhất vì nếu không có nó thì ý niệm về transistor xem như "phá sản" - chúng ta sẽ không thể nào ngắt/đóng dòng điện nếu không có cầu dao, công tắc hoặc CB (Circuit Breaker). Tuy gate không phải là thứ trực tiếp dẫn tín hiệu điện trong mạch, nhưng nó là thứ điều khiển xem mạch điện có tín hiệu hay không. Từ đó chúng ta mới phân định được bit dữ liệu sẽ là 0 hay 1 tuỳ theo tình trạng của mạch điện.

Drain, source hoặc 2 cực của transistor. Nếu một mạch điện không có gate thì nó sẽ không được xem là phân cực. Khi xuất hiện gate thì source (nguồn) sẽ là nơi tín hiệu điện đi vào và drain (đích) là nơi tín hiệu sẽ đi ra. Tuỳ theo bản chất transistor là loại P (positive) hay N (negative) mà giữa source và drain sẽ có dòng điện chạy qua hay không, nhất là khi đang có điện thế đặt vô gate. Để đơn giản vấn đề, chúng ta sẽ tạm hiểu khi gate có điện thì source & drain sẽ có dòng điện chạy qua, tương ứng với mạch ON và giá trị bit là 1.

Channel hay kênh dẫn điện. Đây là phần nằm giữa source & drain và có chức năng chuyển tín hiệu từ nguồn sang đích. Nhưng chức năng của channel không do nó tự quyết định mà bị ảnh hưởng bởi gate nằm ở gần đó. Về bản chất, channel là một vật liệu bán dẫn có khi là chất dẫn điện, có khi là chất cách điện, vốn sẽ thay đổi thuộc tính tuỳ theo điều kiện nhiệt độ, áp suất hoặc dòng điện mà gate tác động lên nó.

FET hay Field-Effect Transistor là một loại transistor. Có nhiều loại transistor tuỳ theo ứng dụng IC. Trong mảng bán dẫn thì FET là loại transistor quan trọng nhất. Nó dựa trên hiệu ứng trường để thay đổi trạng thái transistor khi có sự thay đổi về điện thế áp dụng lên gate. Cụ thể khi có điện áp trên gate, nó sẽ tạo ra một điện trường (field) và điện trường này sẽ làm thay đổi điện tính của channel. Một điều quan trọng là gate sẽ không tiếp xúc trực tiếp với channel mà qua một lớp cách điện. Do đó, phải có hiệu ứng trường thì FET mới hoạt động được.

MOSFET hoặc MISFET. Đây là loại FET được sử dụng phổ biến nhất ngày nay. Nó thường được sản xuất dựa trên việc oxy hoá lớp vỏ bề mặt tấm wafer silicon. Và thông qua các quá trình in khắc/quang lithography, điện phân, ăn mòn acid hoặc kết tủa kim loại... (tuỳ theo từng công nghệ bán dẫn) mà transistor được hình thành. Trên thực tế, FinFET hay GAAFET cũng là MOSFET, chủ yếu khác nhau ở cấu tạo hoặc cách làm ra các thành phần như gate, drain/source và channel. Ở nghĩa hẹp, MOSFET có thể hiểu là dạng FET sản xuất trên mặt phẳng 2D (planar), khác với không gian 3D như FinFET hay GAAFET.

Wafer (silicon). Là tấm nền làm ra transistor có cấu tạo từ các tinh thể silicon (Si) được tạo ra bằng cách nấu chảy cát hoặc các chất chủ yếu chứa cấu trúc silic. Wafer cần có độ tinh khiết rất cao tới 99.9999999% hoặc hơn (cấp độ 9N) mới có thể được dùng để sản xuất ra chip. Wafer hiện nay chủ yếu có các kích thước tính theo đường kính như 100 mm (4 inch), 150 mm (6 inch), 200 mm (8 inch) và 300 mm (12 inch).

Trước khi đào sâu hơn về khác biệt giữa 3 loại transistor nêu ở đầu, chúng ta cần hiểu hơn một chút về cách một con transistor phổ thông (planar) được chế tạo như thế nào. Trong khuôn khổ bài này, chúng ta chủ yếu nói về kỹ thuật in quang lithography đang được sử dụng phổ biến nhất hiện nay. Tất nhiên sẽ có một số khác biệt ở từng tiến trình cụ thể, ở từng công ty cụ thể, nhưng nhìn chung hầu hết sẽ có những bước cơ bản liệt kê dưới đây.

Làm sạch wafer. Wafer sau khi sản xuất xong có thể chưa được dùng ngay mà vẫn để trong kho lưu trữ. Trong khi lưu trữ, chúng vẫn có thể dính phải tạp chất và cần phải được làm sạch bằng các hoá chất dạng lỏng nhằm loại bỏ các tạp chất vô cơ, hữu cơ, phần tử ion hoặc các lớp oxide.

Chuẩn bị wafer. Wafer sau khi được làm sạch sẽ cần gia nhiệt sơ ở 150 °C trong khoảng 10 phút. Mục đích của bước này là để loại bỏ hoàn toàn mọi hơi ẩm hoặc phân tử nước còn bám trên bề mặt. Để chắc ăn hơn, NSX còn có thể phủ thêm một lớp chống thấm vừa có tác dụng ngăn phân tử nước, vừa hỗ trợ việc phủ lớp chặn quang (diễn ra ở sau) được tốt hơn. Sau đó tấm wafer có thể được phơi khô ở 120 °C để giúp "tạo nét" các vi mạch rõ ràng hơn.

Phủ chất chặn quang (photoresist). Bản chất của phương pháp in quang lithography chính là các phản ứng hoá học dựa trên tiếp xúc quang học (photo). Trong đó những khu vực phơi sáng (hoặc không phơi sáng, tuỳ loại hoá chất) sẽ diễn ra các thay đổi về mặt hoá học so với các khu vực còn lại. Những thay đổi này tạo điều kiện cho các phản ứng hoá học diễn ra sau đó và sau khi các phản ứng này hoàn tất, trên bề mặt tấm wafer sẽ hình thành ra các cấu trúc vi mạch khác nhau, làm tiền đề để hình thành nên con chip sau này.

Trong đó, việc phủ chất chặn quang là bước đầu tiên để các quá trình trên diễn ra. Cụ thể, tấm wafer sẽ được đặt trên một bàn xoay và chất chặn quang sẽ được thả lên đó. Nhờ lực ly tâm của bàn xoay nên lớp chặn quang sẽ được dàn đều ra khắp nơi nhằm đảm bảo độ dày của nó là gần như đồng nhất trên toàn bộ wafer. Độ dày của lớp chặn quang hết sức quan trọng vì nó quyết định tới độ chính xác các cấu trúc vi mạch sau đó. Với các cấu trúc siêu vi dưới 125 nm, độ dày tối đa cho lớp chặn quang là 0,5 µm (hoặc 500 nm). Sau đó, tấm wafer sẽ được "nấu sơ" (baking) ở 90 - 100 °C trong khoảng 1 phút để bay hơi bớt lượng chặn quang còn thừa trên bề mặt.

Phơi sáng (hoặc chụp phơi sáng). Wafer sau khi được phủ chặn quang sẽ được đưa tiếp qua công đoạn chụp phơi sáng. Đây là bước tại sao chúng ta có thể tạo ra được các transistor siêu nhỏ ở cấp độ hàng trăm hoặc hàng chục nm. Chính là nhờ 2 yếu tố - mặt nạ quang học (photomask) và bước sóng phơi sáng (UV, DUV, EUV). Trong đó, mặt nạ gồm mặt cắt bản vẽ vi mạch của die chip (cỡ lớn) và một hệ thấu kính giúp thu nhỏ bản vẽ đó hàng trăm, hàng ngàn lần lên tấm wafer. Nhưng để các cấu trúc vi mạch có thể hình thành chính xác trên tấm wafer thì đòi hỏi bước sóng phơi sáng phải càng ngắn càng tốt. Ví dụ DUV có bước sóng từ 193 - 248 nm, EUV thì chỉ có 13.5 nm. Bước sóng càng ngắn thì sai số do giao thoa quang học càng thấp và các "nét vẽ" càng rõ ràng hơn.

Tráng rửa lớp chặn quang (developing). Dùng từ "tráng rửa" ở đây vì ý nghĩa của nó tương đồng với việc tráng rửa phim trong kỹ thuật chụp ảnh film âm bản. Cụ thể lớp chặn quang sau khi bị chiếu DUV hay EUV, những khu vực "bị lộ" ra sẽ có thuộc tính hoá học khác với khu vực "được che chắn". Tấm wafer cũng sẽ được đặt trên một bàn xoay như ở bước phủ chặn quang. Nhưng lần này nó sẽ được tráng một lớp hoá chất để "bóc tách" phần chặn quang không mong muốn (căn cứ theo bản vẽ chip). Nếu là chất chặn quang dương tính, phần bị phơi sáng sẽ bị hoà tan đi. Nếu là âm tính, thì phần không phơi sáng sẽ bị hoà tan. Những gì không hoà tan còn lại trên tấm wafer là tiền đề cho các vi mạch "mọc" lên (develop) ở các công đoạn sau này.

Cấy ion (implantation). Thực tế cho tới lúc này, các thành phần của transistor (gate, source/drain, channel) vẫn chưa hình thành. Nhưng các bước phủ chặn quang, phơi sáng và rửa chặn quang có tác dụng "phân lô bán nền". Chúng giúp xác định cụ thể vị trí của từng transistor sẽ nằm ở đâu trên tấm wafer. Vì một con chip sẽ là tổ hợp của hàng ngàn, hàng triệu, hàng tỷ transistor khác nhau. Nên các transistor không thể nằm "lộn xộn bừa bãi" mà phải có "địa chỉ" cụ thể.

Khi vị trí từng transistor đã được xác định, chúng ta chuyển qua việc cấy ion và ăn mòn vi mạch. Mục đích của 2 công đoạn này là để tạo ra từng thành phần của transistor. Trên nguyên lý mỗi thành phần sẽ có lý tính, hoá tính khác nhau. Ví dụ nMOSFET sẽ có source/drain cùng loại n (negative hay điện âm), tấm nền loại p (positive hay điện dương). Khi đó việc cấy ion sẽ bao gồm đặt thêm mặt nạ quang học (ứng với bản vẽ nMOSFET) và bắn các ion âm qua các khe hở của mặt nạ lên bề mặt wafer. Các vị trí trên tấm wafer sau khi bị bắn ion âm sẽ trở thành source/drain loại n và có tính dẫn điện. Các vị trí không bị bắn ion sẽ vẫn là trung tính. Với pMOSFET thì ngược lại, vị trí bị bắn sẽ là ion dương và tấm nền là âm. Về bản chất, công đoạn cấy ion tương tự như phơi sáng lớp chặn quang, đều giúp tạo ra các đường nét cho vi mạch.

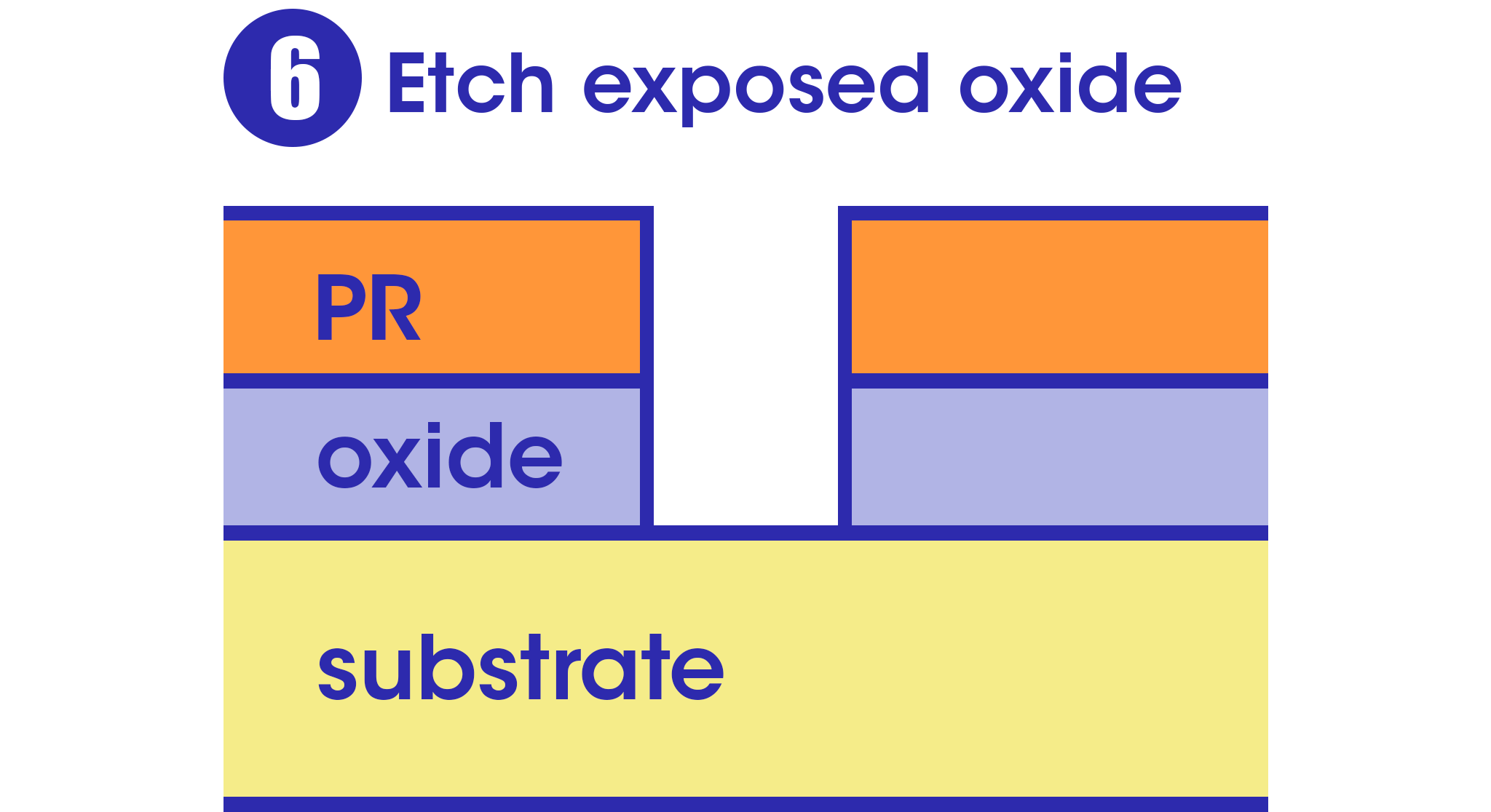

Ăn mòn vi mạch (etching). Nếu cấy ion giống như phơi sáng lớp chặn quang thì ăn mòn sẽ tương tự như tráng rửa lớp chặn quang. Nó có ý nghĩa giúp "bóc" đi những vị trí không cần thiết trên wafer để làm rõ nét các thành phần của transistor hơn. Đồng thời, nó có thể hỗ trợ để chuẩn bị trước cho việc cấy ion vào những vị trí khác các vị trí cấy ban đầu (do khác biệt tính chất, chức năng của từng bộ phận). Nếu gọi cấy ion là "lấp đất" thì ăn mòn vi mạch chính là "đào đất" - cả 2 cùng có tác dụng tương hỗ cho việc làm ra từng cấu thành của con chip. Và một con chip có thể trải qua nhiều lần cấy - đào khác nhau trước khi một sản phẩm hoàn chỉnh ra đời.

Về cách tiến hành, có 2 dạng ăn mòn - ăn mòn "khô" bằng tia plasma hoặc ăn mòn "ướt" bằng hoá chất. Ăn mòn "ướt" tương tự như tráng rửa lớp chặn quang - wafer được ngâm trong một loại hoá chất có khả năng hoà tan những vị trí có hoá tính phù hợp (chẳng hạn acid hoà tan được base hay oxide) từ đó làm lộ ra các vị trí mong muốn. Còn ăn mòn "khô" được thực hiện bằng cách bắn chùm tia plasma lên bề mặt wafer thông qua mặt nạ quang học. Các vị trí bị bắn sẽ xuất hiện các thay đổi lý tính khiến chúng bị bốc hơi đi. Ăn mòn "khô" hiện được ưa dùng hơn do tốc độ bào mòn có thể thay đổi được chứ không đồng nhất ở mọi vị trí như ăn mòn "ướt", từ đó không làm hao hụt đi quá nhiều những vị trí không mong muốn.

Hoàn tất hoặc loại bỏ lớp chặn quang. Sau khi tất cả các thành phần của die chip đã được làm xong, phần lớp chặn quang còn sót lại (chưa bị rửa đi ở công đoạn trước) sẽ được "bóc" đi nốt. Tương tự bước ăn mòn vi mạch, lớp chặn quang có thể bị loại bỏ bằng hoá chất hoặc bằng tia plasma. Hoá chất sẽ làm thay đổi thuộc tính của lớp chặn quang, khiến cho nó mất khả năng bám dính vô bề mặt wafer. Còn tia plasma đặc biệt có chứa oxygen cũng sẽ làm oxy hoá lớp vật liệu này một cách nhanh chóng. Những gì không mong muốn còn sót lại cũng sẽ được xử lý tương tự.

Sản phẩm sau cùng sẽ là tấm wafer có chứa đầy các die chip đã hoàn chỉnh. Việc còn lại là chuyển chúng đến các cơ sở chuyên cắt wafer thành từng die riêng và tiến hành các công tác kiểm định xem die nào hoạt động tốt hay không tốt. Không tốt thì không tốt như thế nào và có thể dùng được tới đâu. Quá trình này gọi là harvest nhằm tận dụng lại những die chip không hoàn hảo để làm ra những model cấp thấp hơn để phân phối ra thị trường. Về khâu này, chúng ta sẽ có bài viết chuyên sâu hơn để bàn.

Video tóm tắt quá trình sản xuất chip.

Phần 2: Planar MOSFET, FinFET, GAAFER và tương lai của ngành bán dẫn

a. Phủ lớp cách điện oxide SiO2 phục vụ quá trình tạo giếng loại âm, hay còn gọi là Nwell để tạo PMOS

b. Phủ thêm lớp chặn quang cho quá trình khắc với mặt nạ

c. Bắn phá bằng tia UV

d. Sau khi bắn phá thì thành thế này

e. Khắc xuyên qua lớp oxide thì thành thế này

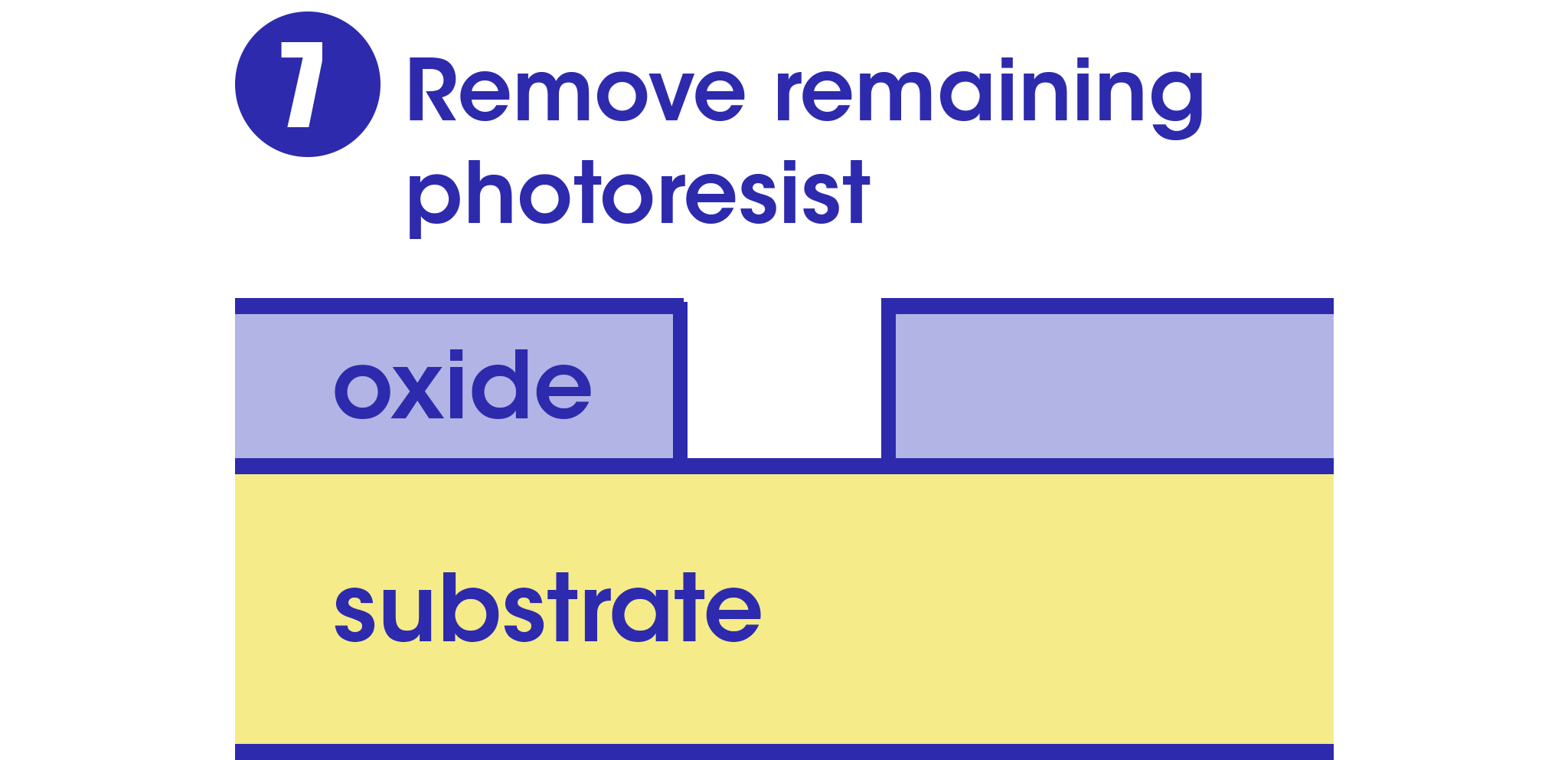

f. Loại bỏ lớp chặn quang để chuẩn bị cho quá trình tiếp theo

Đó là cơ bản. Tùy từng lớp thì công đoạn sẽ hơi khác một chút. Ví dụ như pha thêm các hạt N+ và P+ để làm implement thế nào. Thêm các trường oxide mỏng để tạo lớp cách điện cho poly gate. Rồi thì tạo các lớp contact, metal, via để kết nối mạch điện. Sử dụng các mặt nạ sáng, mặt nạ tối...

Cơ bản nhất là loại Planar MOSFET, phức tạp hơn thì là FiNFET, hơn nữa thì là GAAFET...

(ảnh bên dưới là từ quyển CMOS Circuit Design, Layout, and Simulation của Jacob Baker)

Người hiểu thì không viết thế này.

gần đây có kỹ thuật powervia thì sẽ khác đi một chút

Mềnh nghe nói bên Taiwain TMSC có chuỗi cty phụ trợ packaging tốt, đc đầu tư bài bản hàng chục tỷ đô la tạo thành chuỗi cung cấp chip cao cấp.

FPT vừa đạt doanh thu toàn cầu $1 tỷ, nếu đầu tư phát triển chip cao cấp còn xa phết, ít ra họ dám nhảy vào mảng khoai này.

1. Con người k đủ kiến thức.

2. Giới hạn của công nghệ vì máy khắc người ta độc quyền .

3. Đầu tư nhưng chắc chắn lỗ

làm fab sản xuất semi chua lắm, FPT chui vào có mà phá sản