Cho đến thời điểm hiện tại, Intel đang khai thác gần như tối đa tiến trình 10nm SuperFIN. Intel 10nm SuperFIN là một bước tiến lớn bởi nó chính là pha "Tick" - thu nhỏ tiến trình đầu tiên sau nhiều năm mắc kẹt ở 14nm. Intel 10nm SuperFIN cũng đã đạt được độ chín, sản lượng cao khi chính Intel cho biết số lượng wafer 10nm sản xuất được mỗi ngày giờ đây nhiều hơn 14nm và nhờ đó, Intel tự tin chuyển đổi từ 14nm sang 10nm.

10 nmSuperFIN hiện đang được dùng để sản xuất nhiều sản phẩm của Intel như vi xử lý thế hệ 11 cho laptop, GPU và vi xử lý cho máy chủ. Tuy nhiên, Intel không muốn lặp lại những dấu "+" như thời 14nm với tiến trình 10nm SuperFIN. Từ đây đến 2025, lịch trình của Intel bao gồm Intel 7, Intel 4, Intel 3 và Intel 20A nhưng đáng chú ý nhất là 20A bởi nó sử dụng thiết kế transitor mới là GAAFET thay vì FinFET.

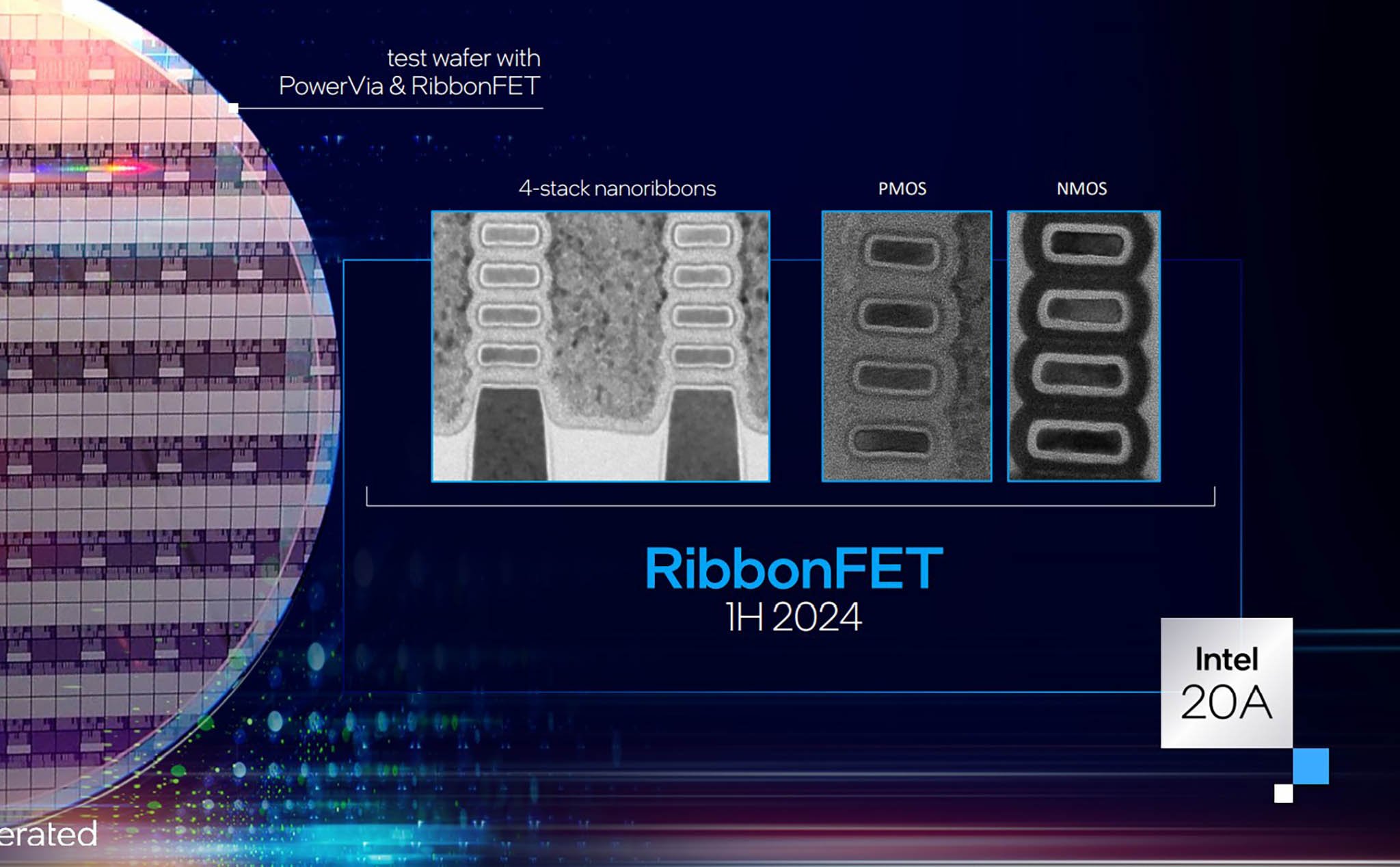

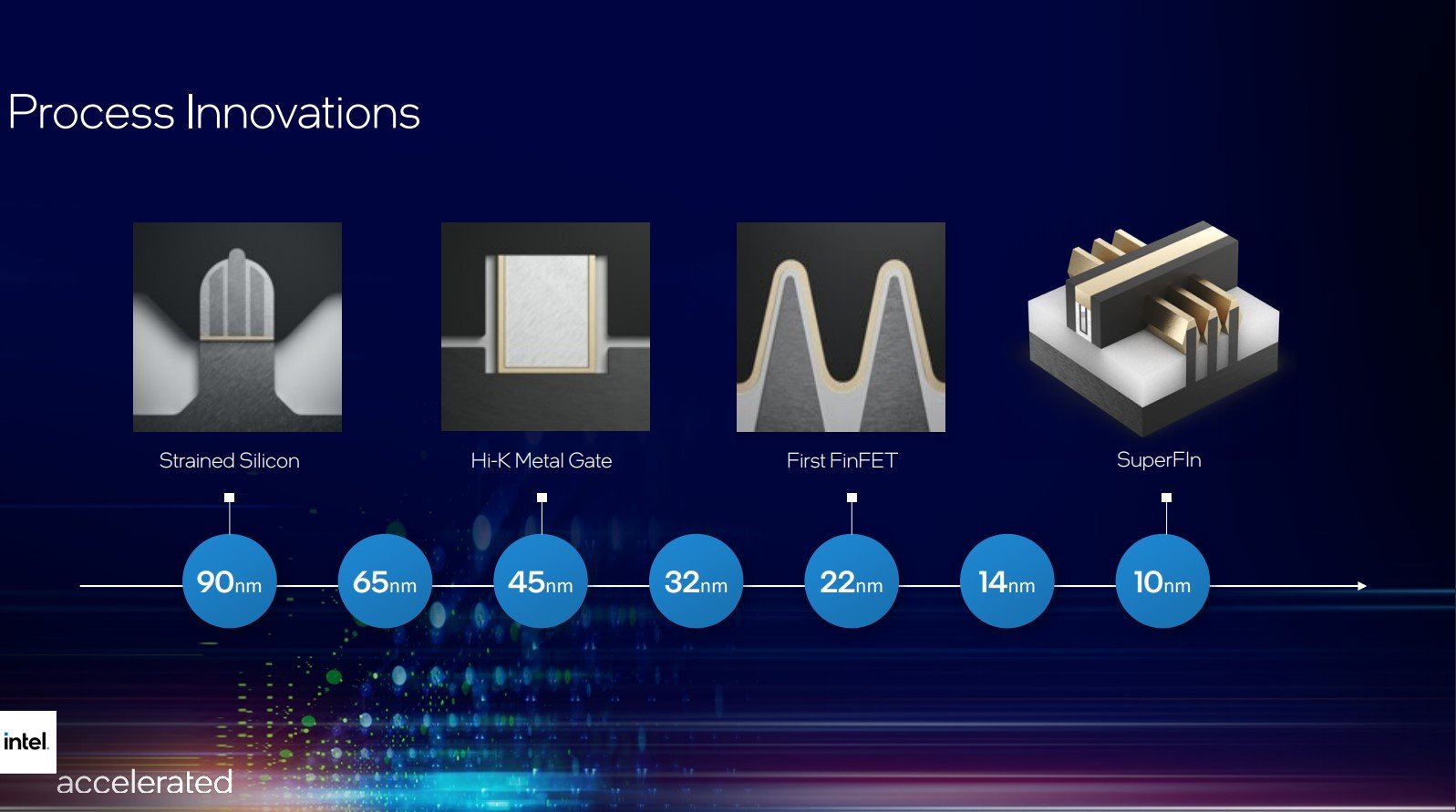

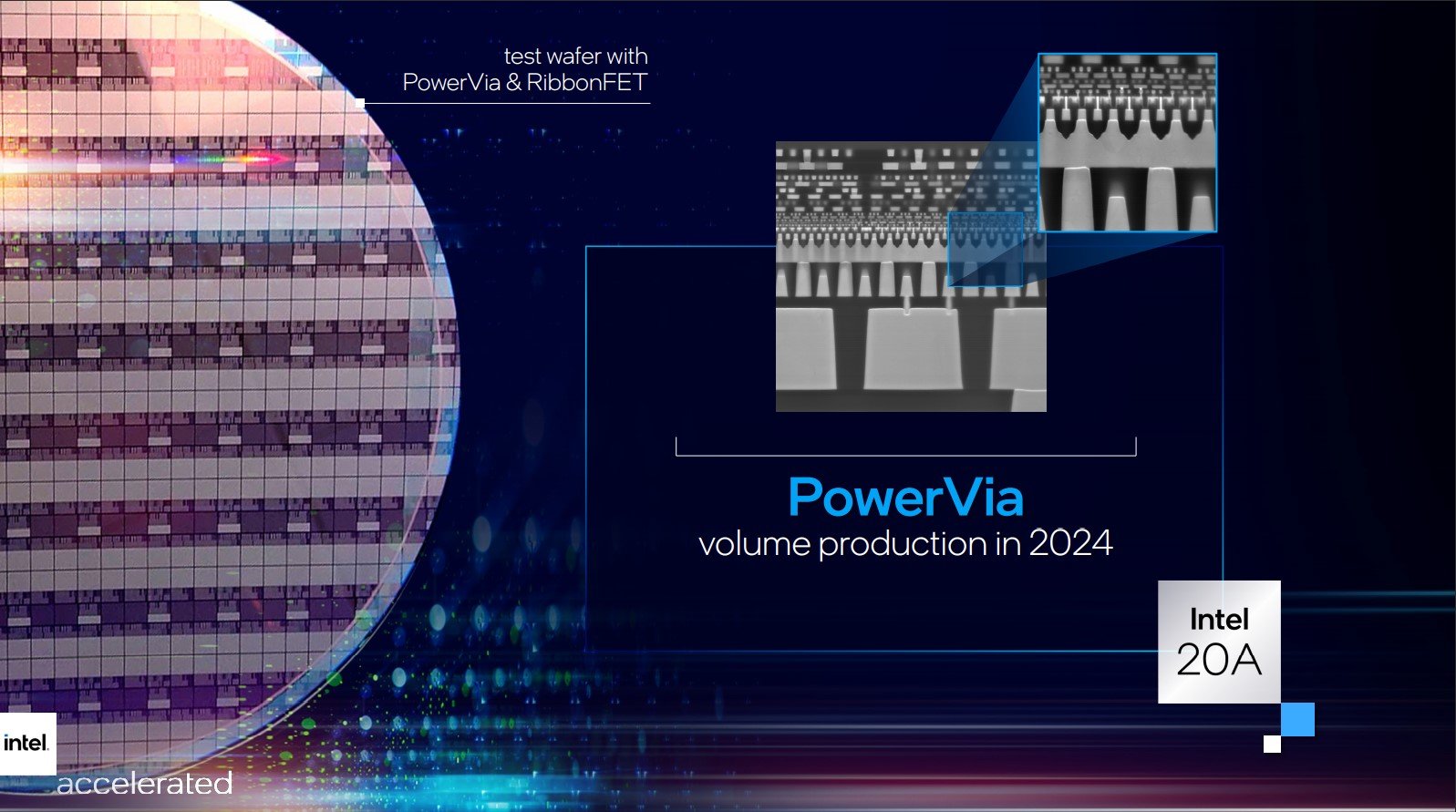

Sau Intel 3 sẽ là Intel 20A - Intel gọi là kỷ nguyên Angstrom. Tiến sĩ Ann Kelleher - người đứng đầu mảng phát triển công nghệ của Intel đã nhắc lại về lịch sử đặt nền móng của Intel với từ tiến trình 90nm Strained Silicon đến Hi-K Metal Gate của tiến trình 14nm, thế hệ FinFET đầu tiên trên tiến trình 22nm và gần đây là SuperFIN 10nm. Với Intel 20A, Intel giới thiệu RibbonFET - một phiên bản của Intel với thiết kế transistor GAA (Gate-All-Around) và công nghệ PowerVIA.

10A (Angstrom) = 1nm và 20A tức 2nm. Tuy nhiên, điều đáng nói không nằm ở kích thước mà ở thiết kế transistor - chuyển từ FinFET sang GAA hay GAAFET. Nhưng trước khi hiểu rõ hơn về thiết kế GAAFET thì chúng ta cần điểm lại thiết kế bóng bán dẫn hiệu ứng trường FET (Field Effect Transistor).

10 nmSuperFIN hiện đang được dùng để sản xuất nhiều sản phẩm của Intel như vi xử lý thế hệ 11 cho laptop, GPU và vi xử lý cho máy chủ. Tuy nhiên, Intel không muốn lặp lại những dấu "+" như thời 14nm với tiến trình 10nm SuperFIN. Từ đây đến 2025, lịch trình của Intel bao gồm Intel 7, Intel 4, Intel 3 và Intel 20A nhưng đáng chú ý nhất là 20A bởi nó sử dụng thiết kế transitor mới là GAAFET thay vì FinFET.

Sau Intel 3 sẽ là Intel 20A - Intel gọi là kỷ nguyên Angstrom. Tiến sĩ Ann Kelleher - người đứng đầu mảng phát triển công nghệ của Intel đã nhắc lại về lịch sử đặt nền móng của Intel với từ tiến trình 90nm Strained Silicon đến Hi-K Metal Gate của tiến trình 14nm, thế hệ FinFET đầu tiên trên tiến trình 22nm và gần đây là SuperFIN 10nm. Với Intel 20A, Intel giới thiệu RibbonFET - một phiên bản của Intel với thiết kế transistor GAA (Gate-All-Around) và công nghệ PowerVIA.

10A (Angstrom) = 1nm và 20A tức 2nm. Tuy nhiên, điều đáng nói không nằm ở kích thước mà ở thiết kế transistor - chuyển từ FinFET sang GAA hay GAAFET. Nhưng trước khi hiểu rõ hơn về thiết kế GAAFET thì chúng ta cần điểm lại thiết kế bóng bán dẫn hiệu ứng trường FET (Field Effect Transistor).

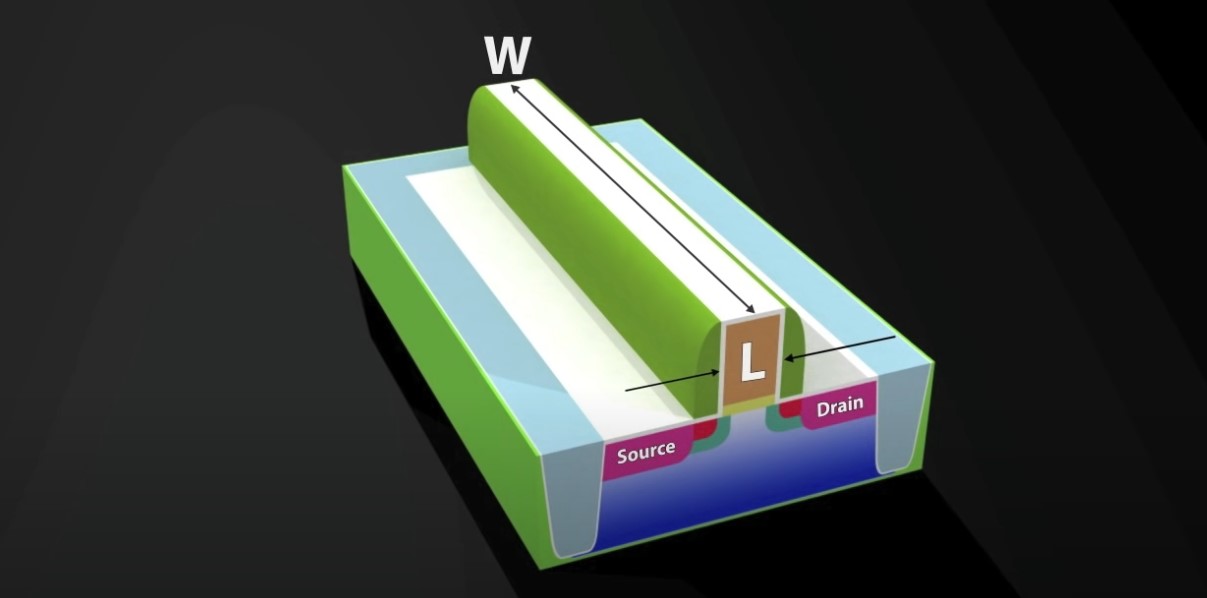

Tất cả các transistor hoạt động bằng cách điều khiển sự chuyển động của các electron, với thiết kế FET thì nó có ba thành phần đầu cuối cơ bản gồm source (bộ phát hay emitter), drain (bộ thu hay collector) và gate (cổng đóng mở) (kích thước của gate sẽ được tính là chiều dài (L) bằng khoảng cách giữa source và drain, chiều rộng (W) lại dài hơn và cũng là chiều rộng của channel (kênh truyền dẫn electron từ source sang drain). Transistor thì được làm bằng silicon - một chất bán dẫn, không hoàn toàn dẫn và cũng không hoàn tòan cách điện. Tuy nhiên khi được pha tạp với các chất khác thì nó sẽ có thêm các electron mang điện tích âm, nếu là loại n-type (pha với arsen hay phốt pho) thì các electron này dễ mất, dễ cho đi và ngược lại loại p-type (pha với boron, nhôm, gallium) thì các electron bổ sung ít hơn và có xu hướng hút các electron khác hay dễ nhận hơn.

Source và drain đều có bán dẫn n-type nhưng chúng không trao đổi electron với nhau được vì các lỗ trống trong bán dẫn p-type nằm giữa. Tuy nhiên, nếu đặt vào gate một điện áp dương thì điện trường tạo ra tại đây cho phép các electron chảy trong một kênh hẹp từ source sang drain. Điện trường cũng chính là công tắc đóng mở của bán dẫn.

Tuy nhiên, electron vẫn bị rò rỉ từ điểm nối bán dẫn giữa chất bán dẫn p-type và n-type được pha tạp nhiều, ngay cả khi gate đã ngắt điện. Khi kích thước của gate được làm nhỏ đi, chiều dài ngắn lại (cũng là kích thước vật lý để đặt tên cho tiến trình trước đây) thì nó sẽ khó đạt được trạng thái tĩnh điện hoàn toàn hơn và từ đó tình trạng rò rỉ vẫn tiếp diễn, ảnh hưởng đến hiệu suất của vi xử lý.

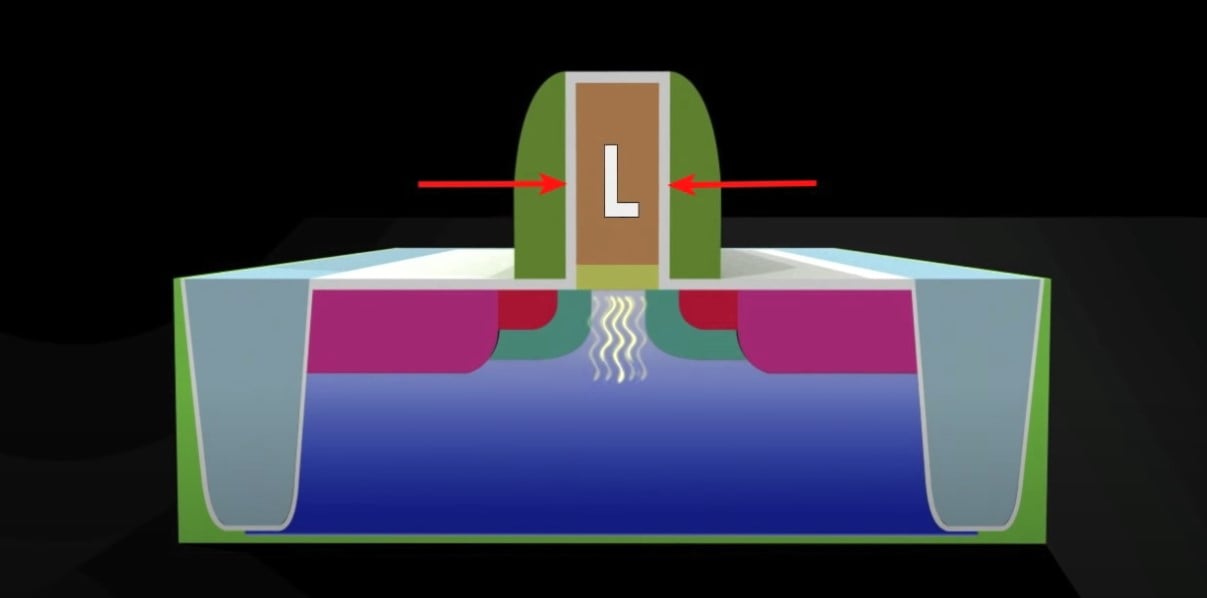

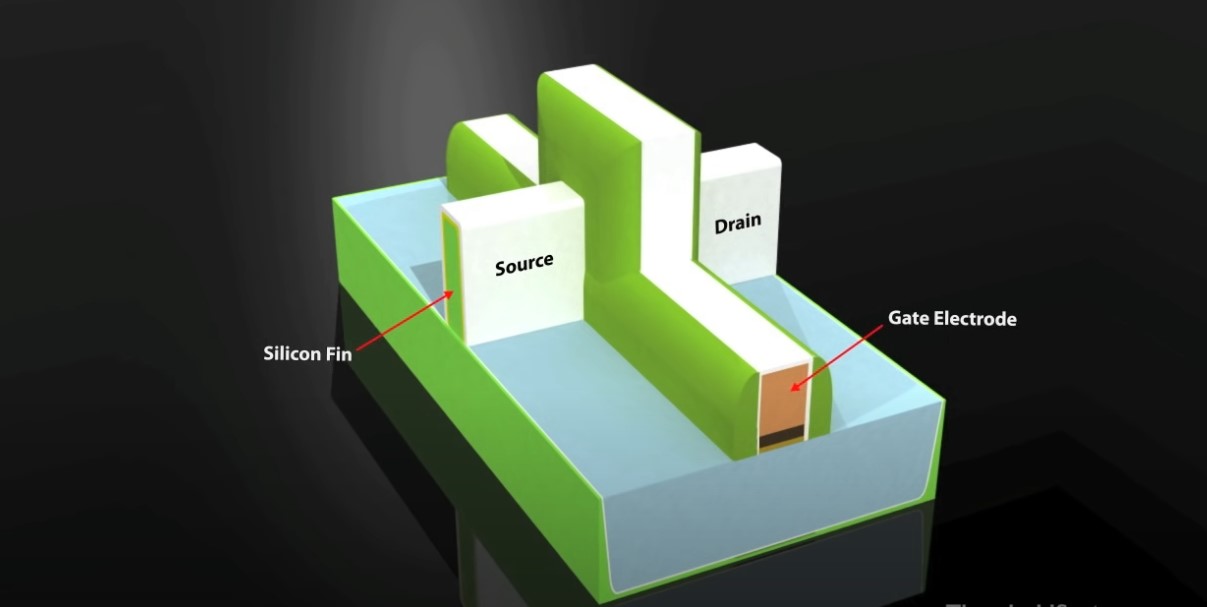

FinFET cải tiến từ Planar CMOS với thiết kế "vây" fin bằng silicon chứa source và drain từ đó tăng bề mặt của channel, cho phép nhiều electron di chuyển hơn và gate sẽ bao quanh fin hay channel ở 3 mặt (tri-gate), tăng khả năng kiểm soát điện áp. Tuy nhiên khi chiều dài của gate giảm đi đến giới hạn vật lý thì nó dẫn đến hiệu ứng đoản kênh và tình trạng rò electron ở mặt dưới của channel vốn không được bao bọc bởi gate. Từ đó, mục tiêu điện năng và hiệu năng sẽ khó có thể đạt được với tiến trình nhỏ. Vậy là GAA là giải pháp tiếp theo.

Hiện tại các hãng sản xuất bán dẫn đều có thiết kế GAA riêng với tên gọi khác nhau, MCBFET của Samsung hay RibbonFET của Intel nhưng nguyên lý cơ bản channel tức kênh truyền dẫn điện tích từ source đến drain của một transistor phải được bao bọc bên trong gate để đạt được tính tĩnh điện lý tưởng nhất từ đó hạn chế tối đa tình trạng rò electron. Khi channel được bao bọc trong gate thì nó được gọi là GATE-ALL-AROUND (GAA) hay nano-wired.

Quảng cáo

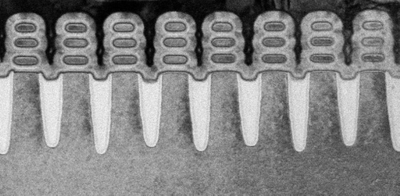

Samsung đã công bố phiên bản MCBFET tức Multi-Bridge Channel FET vào năm 2019 và Intel là RibbonFET với thiết kế gần như tương tự, tên gọi này có thể bắt nguồn từ hình dạng của channel, nó giống dải ruy băng, Samsung thì gọi là các nanosheet. Intel chọn thiết kế 4-stack nanoribbon, hiện tại số lượng các channel là từ 3 đến 5 và con số tối ưu vẫn chưa được xác định. Mỗi fin sẽ có nhiều độ dài khác nhau từ đó dòng điện cho mỗi nhóm transistor hay cell có thể được tối ưu về điện năng, hiệu năng và diện tích.

Một công nghệ mới nữa trên tiến trình Intel 20A là PowerVIA - về cơ bản là thay đổi cách con chip được thiết kế từ mô hình giống như bánh kem nhiều tầng thành bánh mì kẹp. Theo giải thích của AnandTech thì một con chip hiện đại được thiết kế bắt đầu từ lớp transistor (M0) - lớp nhỏ nhất, từ đây thì các lớp kim loại được thêm vào và tăng dần kích thước để tạo ra tất cả các dây dẫn giữa các bán dẫn và nhiều thành phần khác của một vi xử lý như bộ đệm cache, gia tốc, các vi xử lý phụ … Thiết kế vi xử lý hiệu năng cao hiện đại thường có từ 10 đến 20 lớp kim loại như vậy và lớp trên cùng sẽ là nơi đặt các kết nối ngoài. Sau đó con chip được lật ngược lại nhờ đó nó có thể nói chuyện với thế giới bên ngoài thông qua các chân ở dưới còn transistor ở trên.

Với PowerVIA thì Intel thiết kế lớp transistor ở giữa. Một mặt của lớp transistor sẽ có các dây dẫn cho phép nhiều thành phần của chip nói chuyện với nhau, mặt còn lại sẽ là tất cả các kết nối liên quan đến điện cùng với bộ điều khiển điện tích qua gate. Có thể hình dung lớp thịt giữa 2 lát bánh mì chính là transistor. Thiết kế này có ưu điểm là đơn giản hóa phần nguồn và dây dẫn dẫn. Nếu thiết kế theo cách thông thường thì hệ thống dây dẫn và nguồn phải đảm bảo không nhiễu tín hiệu nhưng rất khó, nhất là ở các dây dẫn công suất lớn. Giờ khi tách biệt phần dây dẫn giúp các thành phần của vi xử lý giao tiếp với nhau sang một mặt và toàn bộ phần dây cấp nguồn ở mặt kia, ngăn tách bởi lớp transistor thì nó sẽ giảm thiểu tình trạng nhiễu tín hiệu. Ngoài ra, sự giao cắt của các dây dẫn dữ liệu có thể làm tăng điện trở, khiến năng lượng bị thất thoát và phát sinh nhiệt. Với việc dồn dây cấp điện sang một mặt thì các transistor sẽ nhận được nguồn điện trực tiếp thay vì đi lòng vòng theo thiết kế cũ.