Dù không tự sản xuất ra máy in EUV, TSMC vẫn có những cải tiến mà chính ASML cũng không ngờ tới.

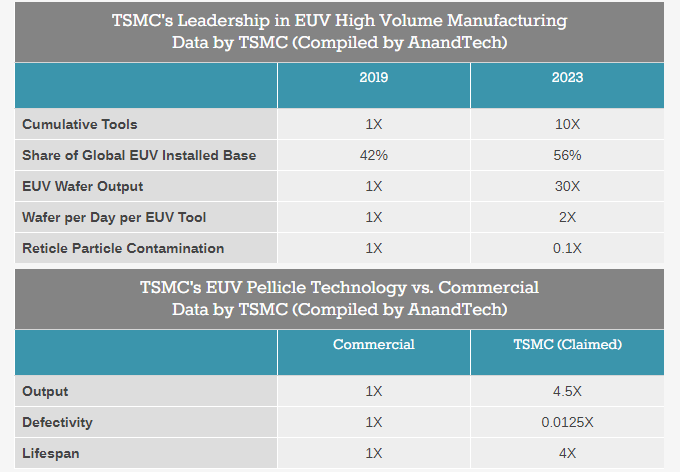

Công ty gia công bán dẫn Đài Loan có thể không phải là đơn vị khai thác EUV đầu tiên (Samsung làm trước) nhưng ngày nay nếu nhắc tới EUV, TSMC là trùm! Theo thông tin chia sẻ tại sự kiện European Technology Symposium, TSMC cho biết họ đã đạt sản lượng EUV tới mức cao nhất trong khi tỷ lệ lỗi sản phẩm là thấp nhất trên thị trường.

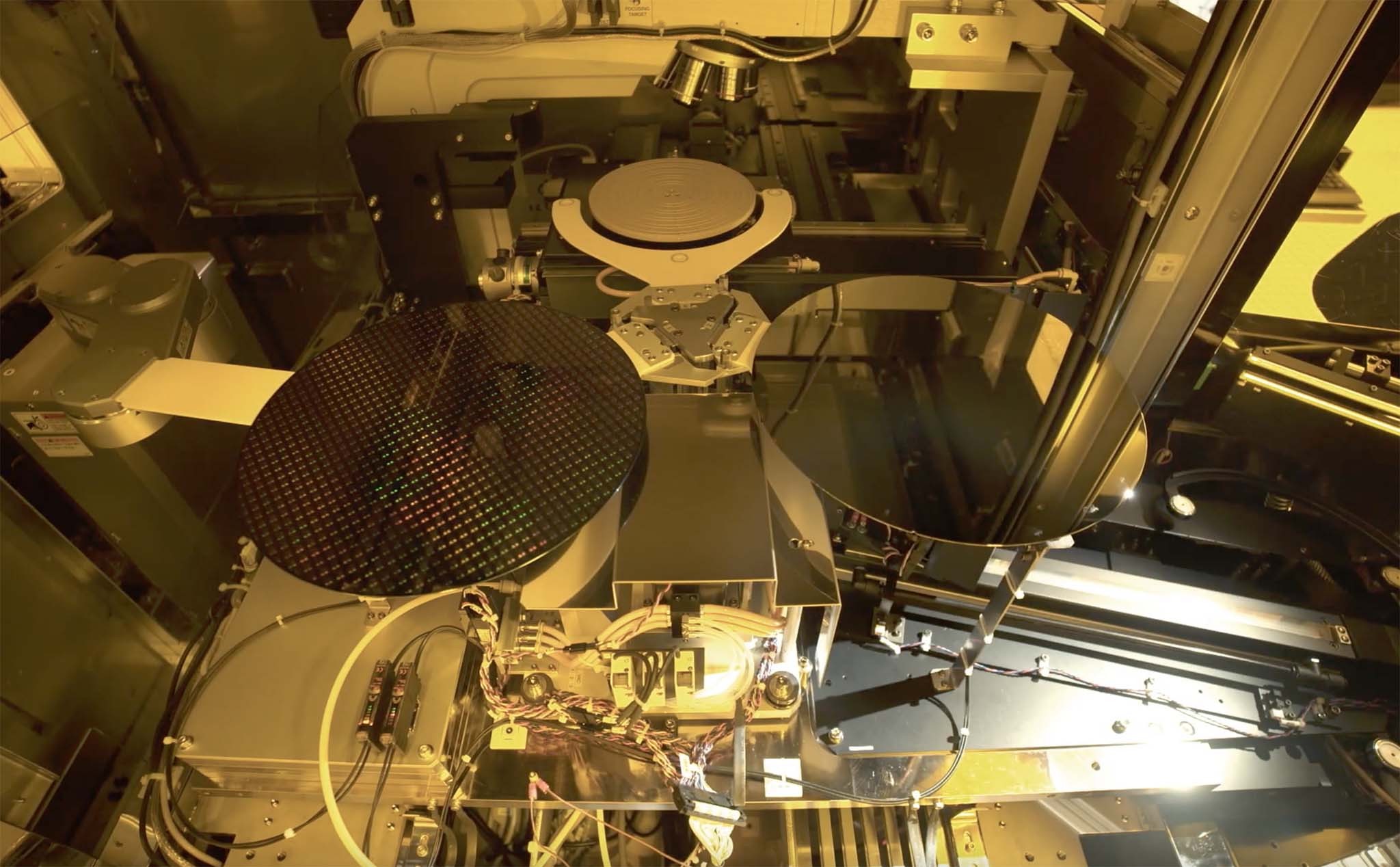

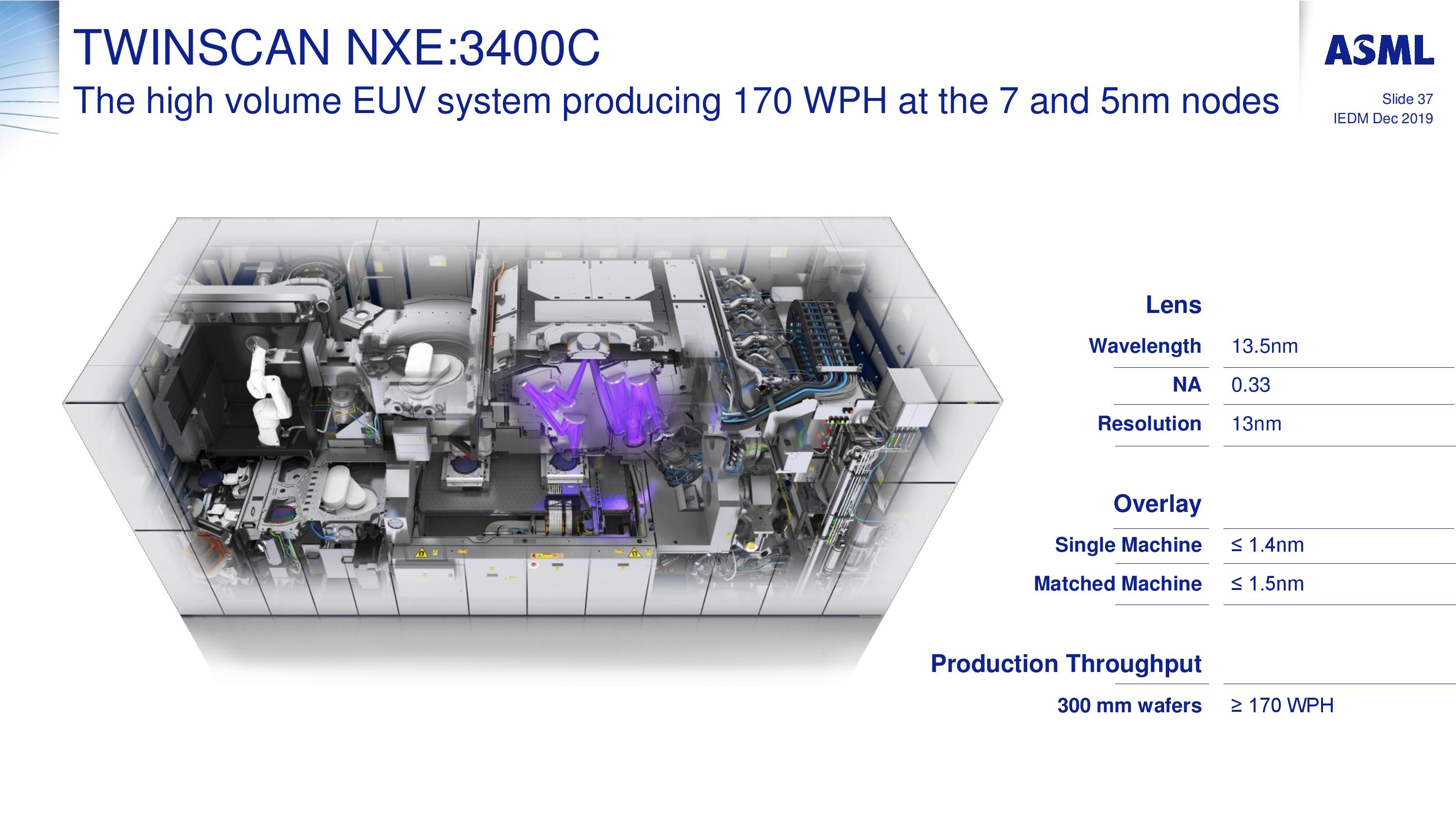

Nhắc lại quá khứ, khi TSMC lần đầu đưa EUV vào sản xuất trong 2019 trên node N7+ (dùng cho chip Huawei), hãng này chiếm 42% tổng số hệ thống EUV có trên toàn thế giới. Tới 2020 thì con số này là 50% và đến 2024 là 56%. Dĩ nhiên, hãng này không phải khách hàng duy nhất của ASML. Samsung và Intel vẫn luôn liên tục đặt hàng mua các hệ thống Twinscan NXE của công ty Hà Lan.

Công ty gia công bán dẫn Đài Loan có thể không phải là đơn vị khai thác EUV đầu tiên (Samsung làm trước) nhưng ngày nay nếu nhắc tới EUV, TSMC là trùm! Theo thông tin chia sẻ tại sự kiện European Technology Symposium, TSMC cho biết họ đã đạt sản lượng EUV tới mức cao nhất trong khi tỷ lệ lỗi sản phẩm là thấp nhất trên thị trường.

Nhắc lại quá khứ, khi TSMC lần đầu đưa EUV vào sản xuất trong 2019 trên node N7+ (dùng cho chip Huawei), hãng này chiếm 42% tổng số hệ thống EUV có trên toàn thế giới. Tới 2020 thì con số này là 50% và đến 2024 là 56%. Dĩ nhiên, hãng này không phải khách hàng duy nhất của ASML. Samsung và Intel vẫn luôn liên tục đặt hàng mua các hệ thống Twinscan NXE của công ty Hà Lan.

Sơ lược về sản xuất công nghiệp

Song số lượng máy móc EUV chỉ là phần nổi của tảng băng. Điều đáng nói nằm trên title bài viết. Trong khi số thiết bị sản xuất "chỉ" tăng gấp 10 lần, thì sản lượng lại tăng tới 30 lần! Có nghĩa là bình quân một hệ thống EUV, TSMC đã "vắt kiệt" gấp 3 lần sản lượng so với giá trị ban đầu! Không chỉ thế, tỷ lệ lỗi sản phẩm gần như là thấp nhất trong toàn ngành công nghiệp.

Nhưng để có thể hiểu được sự "thần kỳ" ở đây, bạn cần có chút kiến thức về sản xuất công nghiệp. Trong sản xuất thông thường sẽ có 2 con số cơ bản - sản lượng mỗi giờ (hoặc ngày, tháng, tuỳ theo loại sản phẩm) và tỷ lệ sản phẩm lỗi (thường là phần trăm trên tổng sản phẩm làm ra). Ngoài ra, còn một khái niệm nữa là thời gian chết (downtime), đó là khi máy móc không vận hành sản xuất được (có thể vì bị lỗi, có thể vì thay thế nâng cấp thiết bị).

Trong sản xuất dây chuyền, công đoạn chiếm nhiều thời gian nhất ảnh hưởng nhất tới năng suất

Giả dụ nếu nói sản lượng là 300 sản phẩm/giờ, tỷ lệ lỗi 5% (tức 15 sản phẩm lỗi/giờ), downtime trung bình 10' mỗi giờ. Có nghĩa cỗ máy/dây chuyền đó chỉ làm ra 300 sản phẩm trong vòng 50' (vì 10' không hoạt động), hoặc 6 sản phẩm trong 1'. Như vậy nếu có thể giảm downtime còn 5' mỗi giờ, thì bạn sẽ có thêm 5' sản xuất, tương ứng với thêm 30 sản phẩm/giờ. Có nghĩa sản lượng của bạn sẽ tăng 330 sản phẩm/giờ khi giảm downtime còn 1/2 so với ban đầu.

Tình huống khác, với sản lượng 300 sản phẩm/giờ, tỷ lệ lỗi 5%, có nghĩa cứ 300 sản phẩm bạn làm ra sẽ có 15 sản phẩm không xuất được, cho ra sản lượng thực tế (tính tới tay khách hàng) chỉ còn 285 sản phẩm/giờ. Vậy nếu có thể cải tiến dây chuyền để ít sản phẩm lỗi hơn, thì số sản phẩm tới tay khách hàng sẽ cao hơn. Ví dụ tỷ lệ lỗi giảm còn 3%, ứng với 9 sản phẩm lỗi/giờ, hoặc 291 sản phẩm tốt/giờ. Tỷ lệ lỗi thấp hơn sẽ giúp tiết kiệm chi phí nguyên liệu cũng như thời gian sản xuất, đồng thời gia tăng sản lượng (thực tế tới tay khách hàng).

Hệ thống Twinscan NXE 3400C của ASML có năng suất 170+ wafer/giờ

Và đấy chính là những điều TSMC đã/đang và sẽ tiếp tục làm.

Quảng cáo

Tối ưu dây chuyền EUV

Trước khi đi tiếp, bạn có thể đọc lại một số bài viết sau để nắm hơn về quy trình sản xuất chip.

Người ta chế tạo chip bán dẫn - transistor - như thế nào?

Mấy ngày nghỉ Tết âm lịch 2024 mình vẫn làm việc với máy tính, chợt nghĩ ra là những món đồ công nghệ hiện tại mà chúng ta đang sử dụng, đa phần đều có liên quan đến bán dẫn. Transistor là thành phần hay có thể coi là đơn vị cơ bản hình thành nên…

tinhte.vn

Planar MOSFET, FinFET, GAAFET và tương lai của ngành bán dẫn

Planar MOSFET chính là MOSFET nhưng ở hình thái cơ bản nhất (dạng phẳng 2D - planar). Nó là hình dạng chung của hầu hết MOSFET được sản xuất trên các tiến trình bán dẫn trước 14 nm. Tên gọi planar chỉ bắt đầu sau khi các nhà sản xuất bán dẫn nghĩ…

tinhte.vn

Một chi tiết quan trọng trong hệ thống EUV (ban đầu) là chúng không có các tấm bảo vệ photomask/reticle (pellicle) như dây chuyền DUV. Reticle chính là bản vẽ mạch in trước khi chúng được soi chiếu qua chùm UV/DUV/EUV rồi qua hệ thống thấu kính xuống tấm wafer. Do đó nếu reticle bị dơ hoặc bám bụi hoặc có dị vật thì chi tiết mạch in sẽ bị sai lệch so với mong muốn, gây ra sản phẩm lỗi. Đây là lý do cần có thêm tấm bảo vệ để ngăn dị vật rơi vào reticle, mà các hệ thống EUV ban đầu không có.

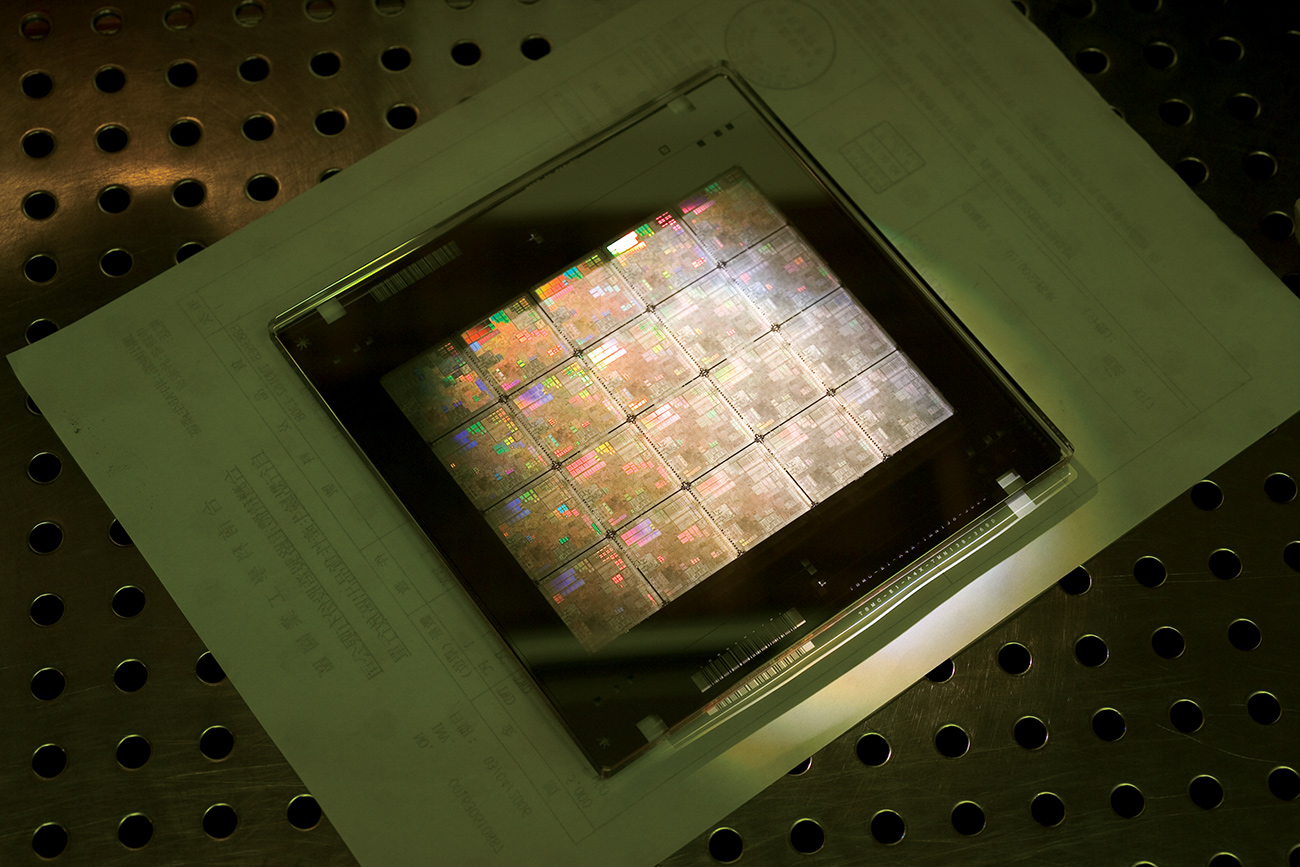

Một tấm reticle dây chuyền 16 nm có màng bảo vệ pellicle

Quảng cáo

Nói thêm, một tấm reticle cho dây chuyền EUV có giá 300,000 USD. Và bạn có thể thấy, mỗi khi có hư hỏng gì thì giá trị sử dụng của tấm reticle sẽ giảm đi. Nếu tấm reticle ứng với bản vẽ 1 con chip, 1 hư hỏng bất kỳ đồng nghĩa tấm reticle này vứt đi. Nếu tấm reticle ứng với bản vẽ 5x5 con chip, 1 hư hỏng nằm ở 1 die chip có nghĩa vẫn có 24 con chip tốt dùng được. Nếu vệt bụi nằm đè lên 2 die chip liền kề thì bạn còn 23 con chip tốt và cứ thế.

Không khó để thấy được, nhà sản xuất chip (Intel, Samsung, TSMC...) sẽ rất không vui khi tấm reticle đắt đỏ kia nhanh chóng hư hỏng xuống cấp. Vì tuy fab sản xuất chip cực kỳ sạch, không có nghĩa là 100% không có hạt bụi nào. Thiết bị càng quay vòng nhanh thì rủi ro các hạt bụi sinh ra do ma sát cơ học càng nhiều. Thế nên, làm sao để reticle càng ít hỏng là mấu chốt để tăng sản lượng và giảm tỷ lệ sản phẩm lỗi xuống. Yêu cầu cấp thiết của một màng bảo vệ reticle là vì vậy.

Tấm bảo vệ pellicle EUV của ASML

Quay lại 2019, lúc EUV mới được đưa vào sản xuất, lúc đó chưa tồn tại pellicle. Tại thời điểm đó, TSMC và Samsung "chỉ dám" dùng EUV cho các chip có kích thước nhỏ (dùng số lượng bù lỗi). Mãi tới tầm 2021, ASML mới ra mắt mẫu pellicle đầu tiên cho EUV. Cần nói rõ thêm rằng do kích thước mạch in càng nhỏ, bản thân tấm reticle lẫn pellicle cũng bị hạn chế về bề dày của chúng (lý do tại sao đắt đỏ). Vì nếu quá dày chúng sẽ gây ra các thay đổi quang học với chùm tia UV chiếu vào (mọi vật liệu khi có bức xạ chiếu tới sẽ xảy ra 3 quá trình - hấp thụ, phản xạ, tán xạ). Reticle cho EUV có bề dày chỉ khoảng 250-300 nm. Còn tấm pellicle của ASML chỉ dày 50 nm, có hệ số chuyển đổi chùm bức xạ đạt 90%, độ sai lệch 0.2% và phản xạ ngược 0.005% cho nguồn phát 400 W.

Tất nhiên, ASML không phải công ty duy nhất cung cấp pellicle. Chúng ta còn IMEC, Mitsu và một vài hãng nghiên cứu khác. Có điều TSMC không nói rõ họ đang dùng pellicle của ai (hoặc có thể là tự phát triển). Chỉ biết để đạt các con số hiện tại, công ty này đã tăng được tuổi thọ reticle lên tới 4 lần (so với 2019), giảm tỷ lệ sản phẩm lỗi tới 80 lần. Hãng chỉ tiết lộ họ đã tối ưu thời gian lẫn công suất mỗi lần phơi sáng, cũng như là hàm lượng chất chặn quang sử dụng (photoresist).

So sánh sản lượng, tỷ lệ lỗi và tuổi thọ reticle do TSMC cung cấp

Lấy bối cảnh TSMC chỉ là công ty gia công, có thể hiểu tại sao họ không kể nhiều về bí mật làm ăn của mình. Dĩ nhiên không ai muốn các đối thủ sẽ nắm được bí kịp để đuổi kịp mình. Nhưng đây cũng là ví dụ cho thấy mối quan hệ biện chứng giữa công cụ sản xuất, lực lượng sản xuất mà Karl Marx từng nói. Mặc dù Intel và Samsung cũng mua được những hệ thống EUV không khác gì TSMC, nhưng tại sao 2 công ty trên (tính tới hiện tại) không thể đuổi kịp TSMC về quy mô cũng như sản lượng, vấn đề chốt lại ở trình độ của lực lượng sản xuất có thể khai thác được công cụ cao tới mức nào. Damage per second có thể cao nhưng hit rate hay critical strike thấp thì cũng không thực sự hiệu quả nhiều.

AnandTech